Fターム[5J022CF02]の内容

アナログ←→デジタル変換 (13,545) | 周辺・部分回路構成 (2,714) | 増幅器(差動・演算) (534)

Fターム[5J022CF02]に分類される特許

41 - 60 / 534

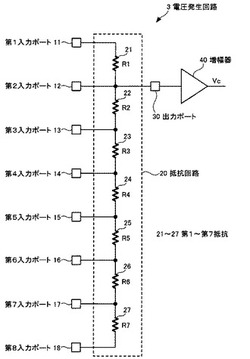

電圧発生回路、共振回路、通信装置、通信システム、ワイヤレス充電システム、電源装置、及び、電子機器

【課題】 可変容量素子の容量を制御するための制御電圧を発生する電圧発生回路において、より簡易で、かつ、より低価格な構成を提供する。

【解決手段】 電圧発生回路3を、抵抗回20と、複数の入力ポート11〜18と、出力ポート30とで構成する。抵抗回路20は、複数の抵抗21〜27を有し、複数の抵抗21〜27を直列又は並列に接続して構成される。複数の入力ポート11〜18には、電位状態をハイ状態、ロー状態及び開放状態のいずれかに制御する制御信号がそれぞれ入力される。そして、出力ポート30は、複数の入力ポート11〜18のそれぞれの電位状態の組み合わせに対応した電圧値の電圧信号Vcを出力する。

(もっと読む)

差動増幅装置

【課題】 差動増幅装置が出力するオフセット電圧を充分に抑制する。

【解決手段】 差動増幅器10は、キャパシタCを介して+IN端子に入力される信号と、−IN端子に入力される信号の差分を増幅する。スイッチS1は、+IN端子が、キャパシタCを介した信号を入力するか否かを切り替える。抵抗RINは、+IN端子と−IN端子の間に接続される。オフセット電圧補正回路20は、+IN端子がキャパシタCを介した信号を入力しないようにスイッチS1が制御された補正期間において、差動増幅器10の出力信号に基づき差動増幅器10のオフセット電圧を補正する。

(もっと読む)

サンプルホールド回路及びAD変換器

【課題】アナログ信号に含まれているサンプルホールド動作周期と同じ周期の周期性ノイズや、サンプルホールド動作周期の逓倍の周期の周期性ノイズ等に起因する影響を抑えて信号処理することのできるサンプルホールド回路及びAD変換器を提供する。

【解決手段】入力されたアナログ信号をサンプルホールドするための第1のサンプルホールド回路部23と、第2のサンプルホールド回路部24との2つのサンプルホールド回路部を備えている。第1のパルス信号生成回路部21は、各サンプルホールド動作周期TSHにおいて、任意のタイミングで第1のサンプルホールド回路部23によりアナログ信号AINがサンプルホールドされると共に、その任意のタイミングを変化させて、第1のパルス信号S1を生成する。これにより、サンプルホールド回路20から出力されたアナログ信号ASHに、なるべく周期性ノイズの同じオフセット成分を付加されないようにする。

(もっと読む)

アナログデジタル変換器

【課題】短時間で誤差を補正することができるアナログデジタル変換器を提供することを課題とする。

【解決手段】アナログデジタル変換器は、アナログ入力電圧をサンプリングするスイッチトキャパシタ回路(101)と、前記スイッチトキャパシタ回路の電圧の正負符号を変換する符号変換回路(401)と、前記符号変換回路の出力電圧を増幅するアンプ(301)と、前記アンプの出力電圧から前記アンプのオフセット電圧を除去するオフセット電圧除去回路(402)と、前記オフセット電圧除去回路の出力電圧をラッチするラッチ回路(302)と、補正モードでは、前記ラッチ回路の出力電圧に応じて前記スイッチトキャパシタ回路の誤差を補正する制御部(103)とを有し、前記スイッチトキャパシタ回路は、アナログデジタル変換モードでは、前記ラッチ回路の出力電圧に応じてアナログ電圧を出力する。

(もっと読む)

半導体集積回路およびその検査方法

【課題】半導体集積回路に内蔵されたアナログ/デジタル変換器をテストするためのテスト信号発生器として半導体集積回路に内蔵されたデジタル/アナログ変換器を使用する際に、デジタル/アナログ変換器が正常なデジタル/アナログ変換動作を実行可能であるか否か動作検証することを可能とすること。

【解決手段】半導体集積回路1は、アナログ/デジタル変換器(ADC)5とデジタル/アナログ変換器(DAC)6とを内蔵する。DAC6は、ADC5をテストするためのテスト信号生成器として使用可能とされる。半導体集積回路1は、DAC6の出力端子とADC5の入力端子の間に入力端子と出力端子とが接続されたバッファ増幅器7を更に具備する。バッファ増幅器7の出力端子とADC5の入力端子のいずれか一方は、半導体集積回路1の外部端子(T1、T2)として外部に導出される。

(もっと読む)

受信回路及び電子装置

【課題】 電子装置における受信回路の面積及び消費電力を低減することができる。

【解決手段】 本受信回路は、受信データを異なるタイミングでサンプリングする複数のサンプリング回路(SWs)と、複数のサンプリング回路によりサンプリングされたそれぞれのデータを保持する複数のホールド回路(C)と、複数のホールド回路からの出力に基づき、入力信号の等化及び補間の度合いを決定するためのパラメータを算出するパラメータ算出回路(70、72、74)と、パラメータ算出回路により算出されたパラメータに基づき、複数のホールド回路のそれぞれの出力に対し重み付けを行う重み付け回路(76)と、重み付け回路により重み付けが行われたホールド回路の出力データを合成して出力する出力回路(N3)と、を備えることを特徴とする受信回路。

(もっと読む)

光伝送装置およびアナログ−デジタル変換装置

【課題】ADCを適切に補正することができる。

【解決手段】変換部1は、光信号を電気信号に変換する。増幅器2は、変換部1によって変換された電気信号を増幅する。ADC3a〜3nは、増幅器2で増幅された電気信号を時分割でアナログ−デジタル変換する。制御部4は、複数のADC3a〜3nの補正を行う際、複数のADC3a〜3nの出力の合計振幅または平均振幅が所定値以上となるように、増幅器2の増幅率を制御する。

(もっと読む)

フォールディング回路およびアナログ・ディジタル変換回路

【課題】光信号を復調する際に、サンプルレートと分解能との間のトレードオフの関係を緩和させ、高いサンプルレートと高い分解能とを両立させたアナログ・デジタル変換を実現する。

【解決手段】フォールディング回路100に、入力信号光を互いに等しい光強度を有するN個の信号光に分配する信号光分配部110と、入力参照光を互いに異なる光強度を有するN個の参照光に分配する参照光分配部120と、N個の信号光とN個の参照光との光強度から入力信号光の光強度を量子化したNビットの温度計コードを導出し、この温度計コードの論理を1ビットおきに反転させた反転温度計コードの各ビットの総和の出力を、入力信号光の光強度の変化に応じて折り返される折返し信号として出力する折返し信号出力部130とを備える。

(もっと読む)

ディスプレイ駆動装置

【課題】ディスプレイ駆動装置、さらに詳細には、平板ディスプレイ駆動装置を提供する。

【解決手段】本発明によるディスプレイ駆動装置は、電源電圧より減少した入力電圧を受け取って基準電圧を生成し、M(Mは、正の整数)ビットのデータ信号に対応する基準電圧を選択するデジタル/アナログ変換部、及びデジタル/アナログ変換部から選択された基準電圧を増幅する増幅部を備える。本発明によるディスプレイ駆動装置は、ディスプレイ駆動装置の回路面積及び電力消費を最小化することができる。

(もっと読む)

デジタルアナログ変換器

【課題】従来のデジタルアナログ変換器では変換精度を向上させることができない問題があった。

【解決手段】本発明のデジタルアナログ変換器は、デジタル入力値の上位側mビットの値に対応した第1のアナログ電圧VO1と第2のアナログ電圧VO2とを出力する上位デジタルアナログ変換器DA1と、下位電圧側ノードND1の電圧VR1と、上位電圧側ノードND2の電圧VR2との電圧差を前記デジタル入力値の下位側nビットの値に応じて分割してアナログ出力電圧VOUTを出力する下位デジタルアナログ変換器DA2と、下位電圧側ノードND1に接続される第1のコンデンサC1と、上位電圧側ノードND2に接続される第2のコンデンサC2と、を有し、上位デジタルアナログ変換器DA1は、下位デジタルアナログ変換器DA2に第1、第2のアナログ電圧VO1、VO2を排他的に出力する。

(もっと読む)

DCオフセット補正機能を備えた無線通信システム

【課題】従来のΔΣ型のA/D変換器を用いたDCオフセット補正は過大入力があると発振し正常にA/D変換できないことから、利得アンプの利得を最小に設定しオフセットを測定していたために精度が悪く、またDC値の測定にはA/D変換後にデジタルローパスフィルタが必要であり低速で回路規模が大きくなる課題を有していた。

【解決手段】DCオフセット補正時にΔΣ型のA/D変換器308の内部の量子化器を用いることで、利得アンプ305の利得を大きくとりながら、過大入力があっても発振せず正常にかつ高速にA/D変換結果が得られる。また、A/D変換器308の出力側にデジタルローパスフィルタを必要としないため、小規模な付加回路で実現可能である。

(もっと読む)

半導体装置および固体撮像装置

【課題】画素情報の読出し速度を向上させることが可能な半導体装置および固体撮像装置を提供する。

【解決手段】カラムADCは、PGA22と、縦列接続された2つの巡回型ADCとを含む。PGA22は、画素の黒レベルおよび信号レベルの差分を増幅した信号にVrefを加算した電位をPGA画素情報として出力する。第1ADC24_1は、Vrefを参照電位としてサンプリングして保持するとともに、PGA画素情報を信号電位としてサンプリングして保持し、これらの差分信号であるi行の画素情報に応じてデジタル値の中の上位ビットを生成すると、(i+1)行の画素情報のサンプリングを開始する。第2ADC24_2は、第1ADC24_1が(i+1)行の画素情報をサンプリングして保持するのと並行して、第1ADC24_1によって生成された上位ビットに応じて該デジタル値の中の下位ビットを生成する。

(もっと読む)

差動増幅回路および液晶表示装置

【課題】消費電流を増加させずにスルーレートを向上する差動増幅回路、表示用駆動回路を提供する。

【解決手段】差動増幅回路は、差動信号を入力する入力段と、入力段の出力に基づいて容量性負荷を駆動する出力段とを具備する。入力段は、差動信号を入力する差動信号入力部(MN1/MN2、MN11/MN12/MP21/MP22)と、差動入力部にバイアス電流を供給する電流源(MN3、MN10/MP20)と、電流源(MN3、MN10/MP20)に並列に挿入される可変容量(Cs)を含むスルーレート調整部(414、415)とを備える。

(もっと読む)

多チャネル量子化器および量子化の方法

【課題】多チャネル量子化器および量子化の方法を提供する。

【解決手段】1つの量子化器は、入力アナログ信号を受け取る複数のチャネル102と、各チャネル内の演算増幅器104と、演算増幅器に接続された比較器106とを有するアナログ−デジタル変換器(ADC)100を含む。ADCはさらに、比較器に接続され、比較器から受け取った比較器信号に基づいて出力を発生するように構成された、各チャネル内の論理回路108を含む。ADCはまた、複数のチャネルに接続され、時間的に変化する基準信号を供給するように構成されたランプ発生器116を含む。

(もっと読む)

アナログデジタル変換器および信号処理システム

【課題】高精度な演算増幅器が不要で、低電力動作、高速動作が可能で、しかも小型化が容易なAD変換器および信号処理システムを提供する。

【解決手段】第1のアナログ信号および第1のアナログ信号の電圧値と第1の基準電圧および第2の基準電圧の差電圧との差に応じた電圧値の第2のアナログ信号を入力し、第1のアナログ信号の電圧値と第2のアナログ信号から生成した中間電圧値の第3のアナログ信号を生成し、第1、第2、および第3のアナログ信号を出力する信号生成部21と、第1のアナログ信号の電圧値と第2のアナログ信号の電圧値を比較し、比較結果に応じた値のデジタルデータを出力する比較部22と、比較部22の比較結果に応じて信号生成部21から出力される第1のアナログ信号、第2のアナログ信号、および第3のアナログ信号の第1の出力部および第2の出力部への入力を切り替える切替部25とを有する。

(もっと読む)

スイッチトキャパシタ回路、サンプル・ホールド回路、および、A/D変換装置

【課題】CLS技術を用いたスイッチトキャパシタ回路に適用する演算増幅器の動作速度に関する所要水準を抑制しつつ比較的振幅の大きい入力信号にも適合するという優位性を維持したスイッチトキャパシタ回路等を実現する。

【解決手段】コンデンサCclsおよびスイッチSW104、SW105、SW106を含んでCLS回路120を構成する一方、スイッチSW107が介挿された導体部、および、SW104、SW105、SW106により切替え回路130を構成し、この切替え回路130によってレベルシフト用コンデンサCclsを、サンプリングフェーズで、アナログ入力信号Vinで充電されるように接続し、レベルシフトフェーズで、アナログ信号出力端子Vbと演算増幅器110の出力端子との間に介挿されるように接続関係を切替えるように構成する。

(もっと読む)

AD変換装置

【課題】差分増幅回路を用いたAD変換装置において、量子化誤差の蓄積を抑圧するように補償して、AD変換出力信号のSNRを従来例に比較して大幅に改善する。

【解決手段】差動増幅回路1AとAD変換器3Aとデジタル復調回路4Aとを備えたAD変換装置において、減算器42,52は、AD変換器3Aからのデジタル信号をアナログ信号にDA変換するDA変換器41,51と、差動増幅回路1Aからのアナログ出力信号からDA変換器41,51からのアナログ信号を減算して、AD変換器3Aの量子化誤差を示す減算結果信号を出力する。AD変換器30は、減算器42,52からの減算結果信号をデジタル信号にAD変換し、加算器43,53は、AD変換器3Aからのデジタル信号にAD変換器30からのデジタル信号を加算することにより量子化誤差が実質的にゼロとなるように補償して、加算結果信号をデジタル復調回路4Aに出力する。

(もっと読む)

A/D変換回路および受信機

【課題】大きなバイアス電流を用いることなく高速動作および低消費電力を可能とするAD変換回路を実現する。

【解決手段】本発明の一態様としてのA/D変換回路は、第1サンプリング容量と、第1サンプリングスイッチと、バッファ回路と、第2サンプリング容量と、第2サンプリングスイッチと、第1変換手段と、第1リセットスイッチと、第2リセットスイッチとを備える。第1および第2サンプリングスイッチをオンにして、第1サンプリング容量に電圧をトラックし、バッファ回路を介して第2サンプリング容量にバッファ電圧をサンプルする。第1サンプリングスイッチをオフにして電圧をホールドする。第2サンプリングスイッチをオフにし、第1変換手段により第2サンプリング容量から電圧を読み出してA/D変換する。その後、第1および第2リセットスイッチにより、第1および第2サンプリング容量をリセットする。

(もっと読む)

アナログ−デジタル変換器、受信器、及び無線通信装置

【課題】

電流モード入力を有するアナログ−デジタル変換器(ADC)を備えた受信器が提供される。

【解決手段】

受信器は、変調された無線信号を復調して電流モードベースバンド信号を生成するように構成されたダウンコンバータ228と、該電流モードベースバンド信号をデジタル出力信号に変換するように構成されたアナログ−デジタル変換器(ADC)224とを有する。ダウンコンバータ228は介在フィルタ素子なくADC224に接続される。

(もっと読む)

音声処理装置

【課題】大きなヘッドルームを設定したアナログ信号をデジタル処理回路で増幅したときのS/N特性を向上する。

【解決手段】音声処理系統11〜1nは、アナログ増幅回路21〜2n、AD変換回路31〜3n、デジタル処理回路41〜4nを有する。第1の音声処理系統11に入力されたアナログ信号は、分配スイッチ62を介して第1と第2の音声処理系統のアナログ増幅回路21、22に分配される。分配されたアナログ信号は、26dBに設定されたヘッドルームに基づいてアナログ増幅回路21、22で増幅され、AD変換回路31、32で−26dBFSのデジタル信号に変換される。これらのデジタル信号は、切換スイッチ71、72を介して、デジタル信号の加算・処理回路40に入力される。これらのデジタル信号は、デジタル信号の加算・処理回路40において加算、増幅され、一般的基準の出力レベルである−20dBFSのデジタル信号として出力される。

(もっと読む)

41 - 60 / 534

[ Back to top ]