Fターム[5J022CF02]の内容

アナログ←→デジタル変換 (13,545) | 周辺・部分回路構成 (2,714) | 増幅器(差動・演算) (534)

Fターム[5J022CF02]に分類される特許

161 - 180 / 534

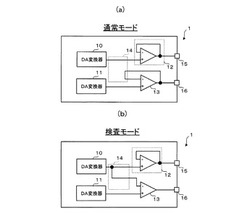

半導体集積回路、液晶駆動回路及び液晶表示装置

【課題】実装面積の増加を抑制しつつ、検査コストを低減させることができる半導体集積回路等を提供すること。

【解決手段】第1のDA変換器10と、第2のDA変換器11と、第1のDA変換器10の出力を増幅する増幅器12と、第2のDA変換器11の出力を入力するオペアンプ13とを備えた半導体集積回路1において、第2のDA変換器11の出力を増幅する増幅器としてオペアンプ13を機能させる通常モードと、第2のDA変換器11の出力を第1のDA変換器10の出力と比較する比較器としてオペアンプ13を機能させる検査モードとを切替える切替え器14とを設けた。

(もっと読む)

ADコンバータ、及びADコンバータの動作試験方法。

【課題】動作試験を容易にする差動入力ADコンバータを提供する。

【解決手段】差動アナログ入力のADコンバータにおいて,第1の差動アナログ入力信号を第1のデジタル出力信号に変換する第1のADコンバータと,第2の差動アナログ入力信号を第2のデジタル出力信号に変換する第2のADコンバータとを有する。第1,第2のADコンバータは,それぞれ,第1,第2の差動アナログ入力信号をサンプルリングするサンプル動作と当該サンプリングした第1,第2の差動アナログ入力信号を出力するホールド動作とを行う第1,第2のサンプルホールド回路を有し,少なくとも第2のサンプルホールド回路は,制御信号により,第2の差動アナログ入力信号の逆相信号を出力する。さらに,制御信号により第2のサンプルホールド回路の正または負極側の出力端子と第1のサンプルホールド回路の負または正極側の入力端子とを接続するテスト用スイッチ手段を有する。

(もっと読む)

デジタル信号再生装置

【課題】従来のデジタル信号再生装置が有していた、アナログ信号に漏洩した高周波ノイズを低減し、アナログ信号の純度を本来の精度まで引き上げることができるデジタル信号再生装置を提供する。

【解決手段】デジタル・アナログ変換部とアナログローパスフィルターから構成されるデジタル信号再生装置において、2個以上のローパスフィルターを有する、あるいは個別半導体によりカスコード回路を用いてアナログフィルター回路を構成する。

(もっと読む)

電流モードAD変換器

【課題】VICの線形性を高めるとともに、ADCの広帯域化を可能とする電流モードAD変換器を得る。

【解決手段】差動信号の入力アナログ電圧値を作動信号の入力アナログ電流値に変換するVIコンバータ10と、1.5ビットの冗長変換機能を有し、VIコンバータの出力である差動信号の入力アナログ電流値をAD変換する電流モードパイプライン型ADコンバータ15とを備え、VIコンバータ10は、電圧利得が−A倍のアンプと、アンプの入力をソースに接続し、アンプの出力をゲートに接続し、負帰還をかけたトランジスタと、抵抗と、定電流源とを含んで構成される。

(もっと読む)

電圧調整回路

【課題】電圧調整回路において、回路が複雑になるレールツーレール型オペアンプを用いることなく、全体として回路の簡素化とチップサイズの低減化を図る。

【解決手段】第1及び第2の出力バッファ4、5をそれぞれNチャネル型オペアンプ、Pチャネル型オペアンプという素子数が少ない2種類のオペアンプを用いて形成する。第1及び第2のスイッチ群2、3は、直列抵抗体1からの2つの電圧Sxa、Sxbを出力する。第2のスイッチング回路6は、直列抵抗体1からの2つの電圧Sxa、Sxbを、それぞれの入力電圧範囲に適合するように、第1の出力バッファ4、第2の出力バッファ5のいずれかに入力するように切り換えを行う。

(もっと読む)

D/A変換回路

【課題】抵抗およびスイッチの数を大幅に削減でき、且つ出力電圧を歪ませることがないD/A変換回路を提供する。

【解決手段】10個の抵抗rを5Vref/4の端子と接地との間に直列接続した直列抵抗回路と、該直列抵抗回路の所定の各抵抗rの接続点に接続され入力データの上位2ビットの値に応じてオン/オフ制御される6個のスイッチからなる上位2ビット側スイッチ群と、前記直列抵抗回路の所定の各抵抗rの接続点に接続され入力データの下位2ビットの値に応じてオン/オフ制御される6個のスイッチからなる下位2ビット側スイッチ群と、上位2ビット側スイッチ群の出力電圧V1と下位2ビット側スイッチ群の出力電圧V2とを入力して前者から後者を減算増幅する減算増幅回路とを備える。出力電圧V1の範囲は、出力電圧V2の範囲よりも広くする。出力電V1,V2の最低電圧は接地電位よりも高くする。出力電圧V1の最高電圧は出力電圧V2の最高電圧よりも高くする。

(もっと読む)

AD変換器および信号処理システム

【課題】必要なSN比に応じて電力を最適な値に設定することができ、時間平均で見た時の電力を削減することができ、入力容量の低減を図ることが可能なパイプライン型AD変換器および信号処理システムを提供する。

【解決手段】パイプライン型AD変換器100は、カスケード接続された複数の残差演算ステージ110、および一つの最終段の残差演算ステージ120のうち、最終段を除く1つ以上の残差演算ステージ110が、分解能が可変な分解能可変残差演算ステージとして形成される。これにより、必要なSN比に応じて電力を最適な値に設定することができ、時間平均で見た時の電力を削減することができ、入力容量の低減を図ることが可能なパイプライン型AD変換器および信号処理システムを実現する。

(もっと読む)

アナログ入力信号をデジタル出力信号に変換する方法

【課題】信号経路間のスイッチングの問題を取り除くこと。

【解決手段】アナログ入力信号をデジタル出力信号に変換する方法であって、信号レベルにおいて異なる少なくとも2つのアナログ信号成分は、該入力信号から導出され、該それぞれの信号成分は、アナログ−デジタル変換を受ける、方法であって、該デジタル化された信号成分は、可変の重み係数によって重み付けされ、該重み付けされた信号成分は、互いに加算されることを特徴とする、方法。

(もっと読む)

半導体集積回路

【課題】電源ノイズ耐性の優れた低消費電流の増幅器を提供する。

【解決手段】トランジスタ対(MN1,MN2)を用いて電流/電圧変換容量素子(CL1,CL2)を第1の電源(VSS)レベルにプリチャージする。このプリチャージ完了後、第2の電源から、差動トランジスタ対(MP1,MP2)を介して定電流を入力信号(VIP,VIN)に応じて振り分けて容量素子に供給する。

(もっと読む)

A/D入力回路の故障診断装置及び故障診断方法

【課題】信号入力線が断線してオープンになったことを、いつでも検出可能なA/D入力回路の故障診断装置を提供する。

【解決手段】隣り合う入力端子に互いに異なる複数種類の電圧信号が入力されるとともに、該複数種類の電圧信号の中から一つの電圧信号を順次切り換えて出力するマルチプレクサ11と、マルチプレクサ11からの出力された電圧信号を取り込んでA/D変換するとともに、A/D変換後の電圧信号を出力するA/Dコンバータと、マルチプレクサ11とA/Dコンバータとの間に設けられ、マルチプレクサ11から出力された電圧信号を電荷として一時的に保持するコンデンサ14とを備え、マルチプレクサ11が複数種類の電圧信号の中から一つの電圧信号を順次切り換えて出力したときに、コンデンサ14に保持した電荷量に変化がない場合は、最後に切り換えた入力端子がオープン状態となっていると判断する。

(もっと読む)

D/A変換器

【課題】デジタル信号からアナログ信号への変換精度を向上させるD/A変換器を提供する。

【解決手段】

D/A変換回路50及び出力電圧設定回路12の加算消費電流は、入力されるデジタル信号D0〜D3の値が上がると、小さくなる変動率になっている。駆動回路13の第3消費電流は、入力されるデジタル信号D0〜D3の値が上がると、大きくなる変動率になっている。この加算消費電流の変動率及び第3消費電流の変動率で相殺するように、駆動回路13の第1〜第3変換抵抗Rh1〜Rh3を設定する。

(もっと読む)

増幅回路及びA/D変換器

【課題】起動時間を短縮し、消費電力の増加を抑制する。

【解決手段】電源電圧Vddと出力ノードVyとの間に接続され、切り替え制御信号が第1の値をとる時にオンし、第2の値をとる時にオフする電流源101と、入力電圧Vinによって電流量が制御される接地された電圧制御電流源104と、前記電圧制御電流源と前記出力ノードとの間に接続されたカスコードトランジスタ102と、前記カスコードトランジスタのゲート電極とソース電極との間に接続されたブーストアンプ103と、前記ブーストアンプの出力ノードとバイアス電圧Vbとの間に接続され、前記切り替え制御信号の値が前記第2の値から前記第1の値へ切り替わるに伴い所定時間オンし、前記ブーストアンプを強制的に立ち上げるスイッチSW13と、を備える。

(もっと読む)

AD変換装置の補正方法、AD変換装置、無線機

【課題】プリアンプのオフセット電圧の補正に必要な電圧が従来よりも低いAD変換装置の補正方法、AD変換装置および無線機の提供。

【解決手段】本発明の一態様に係るAD変換装置の補正方法は、第2の増幅部の入力端を短絡するステップと、比較部へ入力される第1および第2の電圧信号を比較するステップと、比較部での比較結果に応じて、第2の増幅部の出力電圧を補正するステップと、第1の増幅部の入力端を短絡するステップと、第2の増幅部の入力端の短絡を開放するステップと、比較部へ入力される第1および第2の電圧信号を比較するステップと、比較部での比較結果に応じて、第1の増幅部の出力電圧を補正するステップとを具備する。

(もっと読む)

パルス遅延回路およびA/D変換回路

【課題】均等な時間間隔の遅延パルスが得られるパルス遅延回路、及び、A/D変換データの分解能が均一なA/D変換回路を提供する。

【解決手段】パルス信号PAを遅延させて出力する遅延ユニットDUをM(Mは正整数)段直列接続してなるパルス遅延回路10と、サンプリングクロックCKSのタイミングで、パルス遅延回路10内でのパルス信号PAの到達位置を検出(ラッチ)し、その検出結果を、パルス信号PAが通過した遅延ユニットDUの段数を表す所定ビットのデジタルデータDTに変換して出力するラッチ&エンコーダ11とを備えたA/D変換回路1において、各遅延ユニットDUには、バッファ12を介して、A/D変換対象となる入力信号Vinを駆動電圧として印加すると共に、バッファ12の出力を各遅延ユニットDUに供給する信号ラインとグランドラインとの間にコンデンサ13を設ける。

(もっと読む)

ディザ追加型増幅器

アナログ増幅器は、少なくとも1つの信号経路を具備する。上記少なくとも1つの信号経路の各々は、入力端子と出力端子との間に延びるとともに、出力端子に接続された負荷デバイスと入力端子に接続されたトランジスタとを具備する。上記アナログ増幅器は、上記少なくとも1つの信号経路に選択的に接続されたディザ電流源を更に具備する。上記ディザ電流源は、選択された信号経路のトランジスタをバイパスすることによって、選択された信号経路の負荷デバイスに対してディザ電流を直接供給することができる。  (もっと読む)

(もっと読む)

アナログデジタル変換回路

【課題】従来のアナログデジタル変換回路(ADC回路)では、出力結果の線形性を十分に確保できない問題があった。

【解決手段】本発明のADC回路は、第1のプリアンプPA0の入力オフセットを調整する第1のプリアンプキャリブレーション回路CALA0と、第2のプリアンプPA4の入力オフセットを調整する第2のプリアンプキャリブレーション回路CALA4と、第1のプリアンプPA0が出力する第1の出力信号と第2のプリアンプPA4が出力する第2の出力信号との間を補間する補間信号を生成する補間回路30と、入力された信号に基づきデジタル値を出力する複数のコンパレータCMP0〜CMP4と、複数のコンパレータのうち少なくとも補間信号が入力されるコンパレータCMP1〜CMP3の入力オフセットを調整する複数のコンパレータキャリブレーション回路CAL30〜CAL34と、を有する。

(もっと読む)

スイッチトキャパシタ回路およびパイプライン型A/Dコンバータ

【課題】CLS技術を用いて構成されるスイッチトキャパシタ回路およびパイプライン型A/Dコンバータであっても、レベルシフト用コンデンサを用いることによって増加する電力を抑えることのできるスイッチトキャパシタ回路およびパイプライン型A/Dコンバータを提供する。

【解決手段】エスティメートフェーズで、コンデンサCc1(レベルシフト用コンデンサ)を演算増幅器AMP2の出力端子と、演算増幅器AMP2の反転入力端子との間に接続して、演算増幅器AMP2の出力のサンプルと演算増幅器AMP2の位相補償とに兼用する。また、レベルシフトフェーズでは、コンデンサCc1を演算増幅器4の出力端子と出力端子Vbとの間に接続して、演算増幅器AMP2の出力のレベルシフトに用いる。これにより、演算増幅器AMP2の負荷(コンデンサCc1,Cc2の容量)を低減させ、スイッチトキャパシタ回路200の電力を低減させる。

(もっと読む)

オーディオ信号処理装置

【課題】差動回路に入力される2つの信号が同じDA変換回路から出力されるオーディオ信号処理装置を提供する。

【解決手段】オーディオ信号処理装置のDA変換回路の前段にデータ組替回路を設けた。データ組替回路は、第1のデータと第2のデータとをワード単位で交互にシリアルに配列してなる第1のオーディオデータと、第3のデータと第4のデータとをワード単位で交互にシリアルに配列してなる第2のオーディオデータとから、第1のデータと第3のデータとをワード単位で交互にシリアルに配列してなる第3のオーディオデータを生成する。DA変換回路は、生成された第3のオーディオデータを第1のデータと第3のデータとに分離し、それぞれ第1のアナログ信号および第2のアナログ信号に変換する。差動回路は、第1のアナログ信号と第2のアナログ信号とから第3のアナログ信号を合成する。

(もっと読む)

アナログマルチプレクサ

【課題】 複数のアナログ信号を選択して出力するアナログマルチプレクサでは、マルチプレクサ部の出力側の浮遊容量に電荷が蓄積されるために、次に選択した信号にこの蓄積された電荷に起因する誤差電圧が重畳し、正確な信号を出力することができなかったという課題を解決する。

【解決手段】 マルチプレクサ部の出力側にこのマルチプレクサ部の出力を遮断するスイッチ30を設け、このスイッチ30の他端と共通電位点の間に第2のスイッチを設けて、マルチプレクサ部が信号を切り替える直前、あるいは直後に短時間スイッチ30をオフにして、スイッチ31をオンするようにした。浮遊容量13に蓄積された電荷はスイッチ31によって放電されるので、次に選択した信号に誤差電圧が重畳することがなくなる。

(もっと読む)

比較器及びアナログデジタル変換器

【課題】比較器及びそれを備えるA/D変換器において、従来の比較器で存在する極性の異なる2つのクロック信号間のタイミングずれの問題を解消し、且つ、低電力動作を可能にする。

【解決手段】第1及び第2入力電圧信号、並びに、クロック信号が入力され、クロック信号に基づいて動作し、第1及び第2入力電圧信号の値にそれぞれ対応し且つ増幅された第1及び第2出力電圧信号を出力する差動増幅回路部と、第1及び第2出力電圧信号に基づいて動作し、第1及び第2入力電圧信号の比較結果を保持し且つ出力する差動ラッチ回路部とを備える比較器、及び、それを複数備えるA/D変換器を提供する。

(もっと読む)

161 - 180 / 534

[ Back to top ]