Fターム[5J024BA11]の内容

Fターム[5J024BA11]に分類される特許

21 - 40 / 212

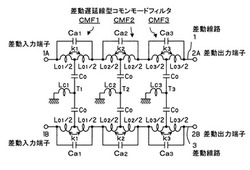

コモンモードフィルタ

【課題】 超高速差動信号を通過させ、コモンモードノイズを通過させ難くする差動遅延線型コモンモードフィルタを得る。

【解決手段】 差動線路1、3中に直列配置したインダクタLo1〜Lo3を含む受動直列素子と、インダクタLo1〜Lo3を橋絡する橋絡容量Ca1〜Ca3と、差動線路1、3間に並列配置された2個の直列キャパシタCoを含む受動並列素子とから全域通過型差動遅延線を形成する。キャパシタCoの接続点T1〜T3とグランド間にコモンモードノイズ減衰用インダクタLc1〜Lc3を挿入し、1区間の差動遅延線型コモンモードフィルタCMF1〜CMF3を形成する。複数の差動遅延線型コモンモードフィルタCMF1〜CMF3を従属接続し、各区間のコモンモードノイズ減衰用インダクタ値および橋絡容量値を異ならせる。

(もっと読む)

LCフィルタ

【課題】小型化しても所望の特性を容易に得ることができるLCフィルタを提供する。

【解決手段】LCフィルタ10は、(a)誘電体層と、誘電体層を介して対向するように配置された対向電極とを有し、対向電極及び対向電極間の誘電体層によりコンデンサが形成された誘電体基板20と、(b)誘電体基板20が実装された実装基板12とを備える。誘電体基板20には第1のボンディングワイヤー26によりインダクタが形成され、インダクタとコンデンサとにより共振器が構成される。誘電体基板20と実装基板12とは、第2のボンディングワイヤー16a,16bにより接続される。第1のボンディングワイヤー26を含む第1の仮想面26kと第2のボンディングワイヤー16a,16bを含む第2の仮想面16kとが、実質的に直角をなす。

(もっと読む)

積層型電子部品

【課題】インダクタとキャパシタを含む共振器を備えた積層型電子部品において、薄型化を可能にし、且つ導体層およびスルーホールの位置のばらつきに起因したインダクタのインダクタンスのばらつきを抑制する。

【解決手段】共振器は、積層体20内に設けられたインダクタ用導体層を含み一方向に長いインダクタ構成部301と、積層体20内に設けられてインダクタ構成部301とキャパシタとを電気的に接続するキャパシタ用接続路304とを有している。インダクタ構成部301の長手方向の両端に位置する第1の端部301Eと第2の端部302Eはグランドに接続されている。キャパシタ用接続路304は1つ以上のスルーホールを含み、インダクタ構成部301の接続箇所301Cに接続されている。接続箇所301Cと端部301E,301Fとの間の距離はキャパシタ用接続路304の長さよりも大きい。

(もっと読む)

電子回路及び電子機器

【課題】従来よりも適用範囲の広い可変インダクタを含む電子回路及び当該電子回路を備える電子機器を提供すること。

【解決手段】本電子回路は、第1インダクタL1、第2インダクタL2a〜L2c、及び電流変化手段SWa〜SWcを備える。第2インダクタL2a〜L2cは、第1インダクタL1に磁界結合され、第1インダクタが生成する磁界により誘導電流が流れる。電流変化手段SWa〜SWcは、第2インダクタL2a〜L2cに接続され、第2インダクタL2a〜L2cに流れる誘導電流を変化させる。第2インダクタL2a〜L2cに流れる誘導電流を変化させることで、可変インダクタ100のインダクタンスを変化させることができる。

(もっと読む)

車載機器用コンデンサ型高周波ノイズフィルター

【課題】使用する部品の数や接続点の数の増加を抑制すると共に、広い周波数帯域幅に渡って高周波ノイズを十分に低減する。

【解決手段】一端が接地される少なくとも1つのコンデンサにより構成される車載機器用コンデンサ型高周波ノイズフィルターであって、入力端子14と出力端子15との間を接続する導電性の電線11と、一端が電線11の一部分と接続され他端が接地されるコンデンサとを備え、前記線路の入力端子側の一区間である入力部(入力側の一区間11a)と出力端子側の一区間である出力部(出力側の一区間11b)とが互いに隣接する位置で交差して、前記入力部と出力部との間に少なくとも1個のループ16を形成し、ループ16の途中の箇所に前記コンデンサの一端を接続し、ループ16のインダクタンスと前記コンデンサとでフィルターを構成する。

(もっと読む)

積層型マルチプレクサ、積層型トリプレクサ及びフィルタ回路

【課題】所定のフィルタ回路の出力側の回路を、積層体の端子電極により形成したインダクタを含めて構成し、小型化と性能の両立が可能な積層型マルチプレクサを提供する。

【解決手段】本発明の積層型マルチプレクサは積層体に構成され、複数の周波数帯域のそれぞれを通過帯域とするフィルタ回路11、12、13は、共通端子Taと複数の個別端子T1、T2、T3を備えている。このうちフィルタ回路13は、共振器Lc、Ldを含む分布定数回路と、キャパシタC32と、直列共振回路13aを含む集中定数回路を備えている。直列共振回路13aに含まれるインダクタL32は、積層体に積層方向に延伸形成された端子電極により形成され、この端子電極は一端がグランド電位に接続され他端がキャパシタC35に接続されている。

(もっと読む)

可変フィルタ

【課題】挿入損失の増大を抑えつつ、急峻な減衰特性を実現することができる可変フィルタを得る。

【解決手段】少なくともどちらか一方が可変素子である容量素子(12、22、32)とインダクタ(11、21、31)からなる直列回路を基本単位回路として構成された第1の可変共振器(10)、第2の可変共振器(20)、および第3の可変共振器(30)を第1の入出力端子(1a)および第2の入出力端子(1b)間に備え、第1の可変共振器は、2つの入出力端子間に直列に接続され、第2の可変共振器は、一端が第1の入出力端子と第1の可変共振器との間に接続され、他端が接地され、第3の可変共振器は、一端が第2の入出力端子と第1の可変共振器との間に接続され、他端が接地されている。

(もっと読む)

コモンモードフィルタ

【課題】 超高速差動信号を通過させ、コモンモードノイズを通過させ難くする。

【解決手段】 差動遅延線DLは、差動線路1、3中に配置された受動直列素子および受動並列素子からなる梯子型の差動4端子回路において、受動直列素子にインダクタLoを、受動並列素子にキャパシタCoを配置して形成される。差動遅延線DLは、並列素子としてのキャパシタCoが、当該キャパシタと等価にして値の等しい2個の直列接続されたキャパシタCo/2とCo/2、又はCoとCoからなる。コモンモードノイズ減衰用の抵抗R12〜R34は、直列接続されたキャパシタCo/2どうし又はCoどうしの接続点T1〜T4間に接続され、コモンモードノイズを吸収減衰させる。

(もっと読む)

半導体装置

【課題】半導体パッケージ内のGNDパッドが、寄生インダクタンス成分を有する事によるGNDワイヤ間アイソレーション悪化のフィルタ回路に対し寄生成分を考慮した回路とする事で、カットオフ特性を良くしたフィルタ回路の提供。

【解決手段】半導体チップ20上に形成されたフィルタ回路の入力側にインダクタL4を設け、更にインダクタL5を介して直列共振回路C2、L2を並列接続し、合わせて並列共振回路C3、L3を直列接続する事で、並列共振回路は減衰させたい高調波等の周波数成分の通過を阻止する構成となり、カットオフ特性を満足させる。

(もっと読む)

可変インダクタ、電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路

【課題】制御電圧入力端子の個数を減少させることができる新規な可変インダクタならびにその新規な可変インダクタを備える電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路を提供する。

【解決手段】本発明の可変インダクタ5においては、複数のインダクタンス素子61、62、63、64におけるそれぞれの接続点とグランド10との間にそれぞれ接続された複数のスイッチダイオード7A、7B、7Cのそれぞれの一端側に対して、複数の定電圧入力端子8A、8B、8Cを介して、互いに異なる定電圧がそれぞれ供給されている。また、本実施形態の可変インダクタ5においては、複数のスイッチダイオード7A、7B、7Cにおけるそれぞれの他端側に対して、1個の制御電圧入力端子9を介して、制御電圧が供給されている。

(もっと読む)

フィルタ装置

フィルタ装置は基板(302)と基板の第1表面に設けられた複数の水平ギャップ閉鎖アクチュエータ(GCA)装置とを有する。複数のGCA装置は1つ以上のGCAバラクタ(700)を有する。複数の水平GCA装置の各々は、少なくとも1つのドライブくし形構造(602a、602b、702a、702b)と、少なくとも1つの入力/出力(I/O)くし形構造(616a、616b、716a、716b)と、ドライブくし形構造及びI/Oくし形構造に互いに入り込んだ少なくとも1つのトラスくし形構造(604、704)とを有する。トラスくし形構造は、トラスくし形構造及びドライブくし形構造の間に印加されるバイアス電圧に基づいて、少なくとも第1の嵌合位置及び第2の嵌合位置の間の移動軸方向に沿って動くように形成されている。  (もっと読む)

(もっと読む)

電子装置

【課題】半導体装置のフィルタ回路に高調波成分の周波数帯域に対応する共振回路部を設けて、所望周波数成分以外の高調波成分を、半導体装置を実装する実装基板を介して、GNDに落とす。このとき、高調波成分は、実装基板の寄生インダクタンス成分と、別の共振回路部とを介して、フィルタ回路に戻ってしまう。その結果、高調波成分において、設計値からリジェクション量が減少してしまう。

【解決手段】実装基板の寄生インダクタンスのうち、半導体装置の共振回路部のGNDと別の共振回路部のGNDとの間の寄生インダクタンス成分を大きく設けることによって、高調波成分のリジェクション量の低下を抑制し、寄生インダクタンスを含まない理想的な場合と同等のリジェクション量を得ることができる。

(もっと読む)

コモンモードフィルタ

【課題】 超高速差動信号を通過させ、コモンモードノイズを通過させ難くする。

【解決手段】 集中定数差動遅延線DLは、差動線路1、3中に配置された受動直列素子および受動並列素子からなる梯子型の差動4端子回路において、受動直列素子にインダクタLoを、受動並列素子にキャパシタCoを配置して形成される。集中定数差動遅延線DLは、並列素子としてのキャパシタCoが、当該キャパシタと等価にして値の等しい2個の直列接続されたキャパシタCo/2とCo/2、又はCoとCoからなる。コモンモードノイズ減衰用インダクタL1〜L4は、直列接続されたキャパシタCo/2どうし又はCoどうしの接続点T1〜T4とグランド電位との間に接続され、キャパシタCo/2、Coとともにコモンモードノイズ減衰用減衰極を形成する。

(もっと読む)

半導体装置および通信装置

【課題】簡便な構成で半導体基板上にその伝播特性が可変な右手系材料、左手系材料による伝送線路を構成可能な半導体装置を提供する。

【解決手段】シリコン基板等の半導体基板11上に、メタマテリアル構造体の所謂左手系の伝送線路12を形成する。この伝送線路12は、キャパシタ部13、インダクタ部14およびMSM接合部15を含み、ハイパスフィルタを構成する。そして、MSM接合部15に外部から電圧V1を印加し、当該電圧V1の電圧値をコントロールすることによって伝播特性を可変とする。

(もっと読む)

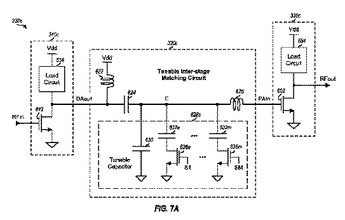

デジタルのチューナブル段間整合回路

性能を改善できるチューナブル段間整合回路について説明する。例示的な設計では、装置は、第1の能動回路(たとえば、ドライバ増幅器)と、第2の能動回路(たとえば、電力増幅器)と、第1の能動回路と第2の能動回路の間に接続されたチューナブル段間整合回路とを含む。このチューナブル段間整合回路は、第1の能動回路と第2の能動回路の間のインピーダンス整合を調整するために個別のステップで変化できるチューナブルキャパシタを含む。例示的な設計では、このチューナブルキャパシタは、(i)並列に接続された複数のキャパシタと、(ii)この複数のキャパシタに対してキャパシタごとに1つ接続された複数のスイッチとを含む。各スイッチは、関連するキャパシタを選択するためにオンにされるか、または関連するキャパシタの選択を解除するためにオフにされることができる。チューナブルキャパシタは、複数のキャパシタと並列に接続された固定キャパシタをさらに含むことができる。  (もっと読む)

(もっと読む)

高周波デバイス

【課題】 渦電流や寄生容量の発生を抑制することができ、優れた高周波特性を示す小型の高周波デバイスを提供する。

【解決手段】 開口14を有する基板11上の誘電体層13にバンドパスフィルタBPFを備える。BPFは例えば第1誘導性素子L1および第1容量性素子C1の組と、第2誘導性素子L2および第2容量性素子C2の組と、第3誘導性素子L3および第3容量性素子C3の組とにより構成されている。開口14は第1誘導性素子L1に対向する位置に設けられている。基板11に対して開口14を設けることにより第1誘導性素子L1の直下での寄生容量および渦電流の発生が抑制され、これにより信号損失が低減されてフィルタ回路の特性が向上する。

(もっと読む)

フィルタ装置

【課題】通過帯域における電力損失を小さくでき、かつ阻止帯域における減衰量を大きくできるフィルタ装置と、当該フィルタ装置を備えた無線通信装置とを提供する。

【解決手段】インダクタ3aとキャパシタ4aとを備えた直列共振回路31fの共振周波数は、インダクタ3bとキャパシタ4bとを備えた直列共振回路32fの共振周波数よりも、フィルタ装置の通過帯域に近くなるように設定される。インダクタ3aのインダクタンス値L1をキャパシタ4aの容量値C1aで割った値は、インダクタ3bのインダクタンス値L2をキャパシタ4bの容量値C2aで割った値より大きい。

(もっと読む)

ハイブリッド・カプラとのインピーダンス整合が改善されたフィルタ

本発明は、テレビジョン信号分配システムにおいて装置間通信に使用される周波数の信号が信号源と干渉するのを防止する帯域除去フィルタに関する。このフィルタは、信号スプリッタと協働し、従来の帯域除去フィルタによって生じるスプリッタを介した装置間通信への悪影響を低減するように設計されている。このフィルタは、主に並列共振回路の動作によってスプリッタに給電するポートに抵抗負荷および高い出力インピーダンスを与えるセクションを帯域除去フィルタに追加したものである。

(もっと読む)

(もっと読む)

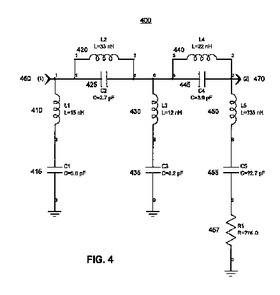

ベッセルフィルタおよび受光装置

【課題】入力側と出力側両方の反射特性(特に通過帯域以降)がよく、小型化、低価格化に適し、広範囲の伝送レートにも対応できる構造を持ったベッセルフィルタを提供する。

【解決手段】入力端子1と出力端子2との間に直列接続されているシリーズ素子L1,L2に対して、抵抗R1,R2を各々並列接続する。さらに、入力端子1とシリーズ素子L1,L2の接続点と出力端子2の3箇所に一端が接続され、他端が接地されているシャント素子C1〜C3に対して、抵抗R3〜R5を各々直列接続する。

(もっと読む)

高周波フィルタ

【課題】伝達特性が可変の高周波フィルタを提供する。

【解決手段】同一の半導体基板に形成されたキャパシタとキャパシタに直列的に接続されたスイッチ素子とを有し、入力端及び出力端間に直列接続された第1の可変容量回路10及び第3の可変容量回路30、第1の可変容量回路10及び第3の可変容量回路30の接続点と接地との間に接続された第2の可変容量回路20、並びに入力端及び出力端に直列接続された第1のインダクタ71と第2のインダクタ72、更に第2の可変容量回路20と第3の可変容量回路30の接続点と接地との間に接続された第3のインダクタ73を備え、スイッチ素子を制御することによりその周波数特性を可変とした。

(もっと読む)

21 - 40 / 212

[ Back to top ]