Fターム[5J039DA10]の内容

パルスの操作 (9,993) | 比較要素 (410) | 電圧比較 (400) | FETによるもの(CMOSを除く) (174) | CMOSによるもの (38)

Fターム[5J039DA10]に分類される特許

1 - 20 / 38

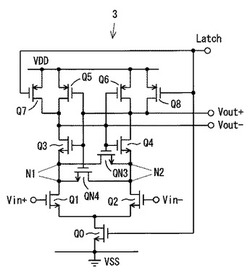

ラッチト・コンパレータ

【課題】差動回路の特性を損なうことなく、高速に信頼性の高いラッチ出力を行うラッチト・コンパレータを提供する。

【解決手段】ラッチト・コンパレータ(1)は、ドレイン・ソース間が、第1の電流経路上の第1のMOSトランジスタ(Q1)と第3のMOSトランジスタ(Q3)との間の第1のノード(N1)と、第2の電流経路上の第2のMOSトランジスタ(Q2)と第5のMOSトランジスタ(Q4)との間の第2のノード(N2)との間に接続されているとともに、ゲートが第1のCMOSインバータの出力に接続された、第7のMOSトランジスタ(QN3)と、ドレイン・ソース間が第1のノード(N1)と第2のノード(N2)との間に接続されているとともに、ゲートが第2のCMOSインバータの出力に接続された、第8のMOSトランジスタ(QN4)と、の少なくとも一方をさらに備えている。

(もっと読む)

半導体装置

【課題】回路構成の簡素化を図るとともに、遅延回路の遅延時間のばらつき等に起因して生じる問題点を解消し、コンパレータの動作を保証する2逓倍器を備えた半導体装置を提供する。

【解決手段】入力クロック信号CLKを可変遅延器16で遅延させた遅延クロック信号CLKDと、前記入力クロック信号の位相を位相比較器18で比較することで前記入力クロック信号CLKの周波数を2逓倍した2逓倍クロック信号CLKX2を生成する2逓倍器20と、前記2逓倍器20からの2逓倍クロック信号CLKX2が第1の論理レベルのとき入力信号の大小の比較動作を行い、前記2逓倍クロック信号CLKX2が第2の論理レベルのとき、比較動作を停止するコンパレータ10と、前記コンパレータ10の出力をモニタし、前記コンパレータ10が比較結果を出力したことを検出した時点でトリガ信号DLCLKを生成する第1の回路12、14を備える。

(もっと読む)

コンパレータシステム、アナログデジタルコンバータおよびコンパレータの閾値補正方法。

【課題】 閾値のずれを補正できるコンパレータシステムを提供する

【解決手段】 コンパレータは、一対のキャパシタを介して入力端子から入力信号を受ける一対の入力ノードと、入力信号の電圧差を示す出力信号を出力する出力ノードとを有する。第1制御回路は、コンパレータの閾値を補正する補正期間に、所定量の負荷が出力ノードに接続された状態で、出力信号の論理が反転するまで一対の入力ノードに設定するコモン電圧を変更し、出力信号の論理が反転するときのコモン電圧の値を求め、求めたコモン電圧を補正期間後の通常動作期間に使用する。第2制御回路は、出力ノードに接続される負荷の量を設定する。第3制御回路は、補正期間に、所定量の負荷が出力ノードに接続されているときのコンパレータの標準の閾値の変動量に対応する電圧差を有する第1電圧および第2電圧を入力端子にそれぞれ供給する。

(もっと読む)

シュミットトリガ回路

【課題】安定なヒステリシス特性を有するシュミットトリガ回路を提供する。

【解決手段】実施形態のシュミットトリガ回路は、PMOSトランジスタP1、P2とNMOSトランジスタN1、N2が直列に接続されたインバータIV1と、PMOSトランジスタP1に並列に接続されたPMOSトランジスタP3と、NMOSトランジスタN1に並列に接続されたNMOSトランジスタN3と、出力信号Zの反転信号DをPMOSトランジスタP3およびNMOSトランジスタN3のゲート端子へ印加するインバータIV2と、を有し、入力信号Aを反転させた信号BをPMOSトランジスタP1およびNMOSトランジスタN2のゲート端子へ印加する高閾値論理回路1と、入力信号Aを反転させた信号CをNMOSトランジスタN1およびPMOSトランジスタP2のゲート端子へ印加する低閾値論理回路2と、を備える。

(もっと読む)

コンパレータ、それを利用したスイッチングレギュレータの制御回路、スイッチングレギュレータ、電子機器

【課題】新規な出力論理を有するコンパレータを提供する。

【解決手段】コンパレータ100は、入力電圧VINを基準電圧VREFと比較する。差動増幅回路10は、その制御端子に基準電圧VREFが印加された第1入力トランジスタMi1と、その制御端子に入力電圧VINが印加された第2入力トランジスタMi2を含む。出力段20は、差動増幅回路10の出力信号Vxを受け、それに応じた信号を比較結果を示す出力信号SOUTとして出力する。フィードバック回路30は、出力段20の出力信号SOUTを受け、出力信号SOUTが第1レベルから第2レベルに遷移すると、出力信号SOUTが第2レベルに戻るように、差動増幅回路10または出力段20にフィードバックする。

(もっと読む)

高速量子化器

【課題】高速量子化器および最適化された時間遅延を提供する。

【解決手段】高速量子化器コンパレータの装置と方法は、3部を含む:プリアンプ部、再生ラッチ部、およびデータラッチ部。時間遅延は、再生ラッチ出力の最初の電圧を変えることによって減少される。電流源はコンパレータの底部に提供され、時間遅延最適化を可能にする。PMOS同等化スイッチが停止されたとき、クロック信号をフィードスルーにし、出力に電荷の注入を提供する。これらの電荷によって、コンパレータの時間遅延が可変となる。リセット時間が比較時間より長いために、非常に低い電流が出力電圧を決定する。

(もっと読む)

ルックアップテーブル回路およびフィールドプログラマブルゲートアレイ

【課題】動作速度の速いルックアップテーブル回路およびフィールドプログラマブルゲートアレイを提供する。

【解決手段】ルックアップテーブル回路1は、入力信号に基づいて複数の抵抗変化型素子の中から一つの抵抗変化型素子を選択する抵抗変化回路2と、抵抗変化回路2の最大抵抗値と最小抵抗値との間の抵抗値を有する参照回路4と、抵抗変化回路2の他端にソースが接続された第1のnチャネルMOSFET6と、参照回路の他端にソースが接続された第2のnチャネルMOSFET8と、第1のnチャネルMOSFET6のドレインを通して抵抗変化回路2に電流を供給する第1の電流供給回路10と、第2のnチャネルMOSFET8のドレインを通して参照回路4に電流を供給する第2の電流供給回路12と、第1のnチャネルMOSFET6のドレイン電位と第2のnチャネルMOSFET8のドレイン電位を比較する比較器14と、を備える。

(もっと読む)

シュミット回路

【課題】ノイズの伝搬をより抑制することが可能なシュミット回路を提供する。

【解決手段】シュミット回路100は、入力信号が入力され、しきい値電圧を可変可能な入力論理回路と、前記入力論理回路の出力信号が入力され、第1のしきい値電圧を有する第1の論理回路C1と、前記入力論理回路の出力信号が入力され、前記第1のしきい値電圧より小さい電圧である第2のしきい値電圧を有する第2の論理回路C2と、前記第1の論理回路C1の出力信号及び前記第2の論理回路C2の出力信号に応じて、前記入力論理回路のしきい値電圧を調整する可変抵抗回路R1、R2と、前記入力信号の電位が前記第1のしきい値電圧と前記第2のしきい値電圧との間の場合はフローティングされたフローティング電位を出力し、前記入力信号の電位が前記第1のしきい値電圧以上若しくは前記第2のしきい値電圧以下の場合は固定電位を出力する第3の論理回路C3と、を備える。

(もっと読む)

コンパレータ回路およびそれを用いた試験装置

【課題】コンパレータの遅延時間分散を低減する。

【解決手段】コンパレータ100は、入力電圧VINと基準電圧VREFを比較する。入力段10は、差動増幅器を含む。遅延回路20は、入力段10の出力信号S1を調節可能に遅延させる。遅延補償回路30は、入力段10におけるオーバードライブ電圧VODに応じて、遅延回路20の遅延量を制御する。遅延補償回路30は、差動増幅器の出力電圧をオーバードライブ電圧VODを示す信号として利用し、遅延回路20の遅延量τを制御する。

(もっと読む)

コンパレータのオフセット補正装置

【課題】コンパレータのオフセット補正装置において、ノイズの影響などに起因して、入力しようとしている電圧と実際入力されている電圧との間に差異がある場合にも、正常に閾値オフセット量を補正する。

【解決手段】コンパレータ201のオフセット補正に際しては、開放スイッチ205を開き、短絡スイッチ204を閉じる。この状態において、制御部203はコンパレータ201に対して、2つの入力端子に入力される同一値のリファレンス電圧同士を比較する動作を複数回繰り返させる。フィルタ202は前記複数回の比較結果を平滑化した頻度信号を出力する。前記制御部203は、前記フィルタ202からの頻度信号に基づいて、コンパレータ201での複数回の比較結果のハイレベルとローレベルとの比率が50%になるように、閾値制御信号をコンパレータ201に出力する。

(もっと読む)

コンパレータ回路、シミュレート方法

【課題】レイアウト上の寄生成分を抽出したポストレイアウトシミュレーションにおいて、小型で低消費電力でありながら精度のよいコンパレータ回路等を提供すること。

【解決手段】比較される入力電圧が印加される入力端子IN1,2と、入力端子から供給された電圧を電流に変換する電圧電流変換部A,Bと、電圧電流変換部が出力したそれぞれの信号を、電源電圧又はGNDに出力するクロスカップルインバータA,Bと、クロスカップルインバータから出力された信号をバッファするための一対のバッファ回路と、バッファ回路の信号を外部に出力する1つ以上の出力端子Out1と、電圧変換部を動作させる一対の第一のスイッチM7,8と、クロスカップルインバータを動作させるための一対の第二のスイッチM11,12と、第一のスイッチのオンタイミングと異なるタイミングで第二のスイッチをオフにする遅延回路と、を有することを特徴とするコンパレータ回路を提供する。

(もっと読む)

コンパレータ回路

【課題】低消費電力動作を実現しつつ信号処理に向けた論理判定時間を格段に削減することができる。

【解決手段】入力電圧と参照電圧とを比較して論理判定結果の出力電圧を発生して差動増幅器を含むコンパレータ回路において、微小電流であるバイアス電流を発生して差動増幅器に供給する電流源と、差動増幅器からの差動電圧を反転して反転信号を出力する第1のインバータ回路と、電流源のバイアス電流を検出し、第1のインバータ回路の貫通電流を検出し、検出したバイアス電流及び検出した貫通電流に基づいて、差動増幅器が論理判定を行わない期間はバイアス電流で差動増幅器を動作させる一方、差動増幅器が論理判定する期間はバイアス電流を増加させてなる適応バイアス電流を用いて差動増幅器を動作させるように適応バイアス電流制御を行うための適応バイアス電流を発生して差動増幅器に供給する適応バイアス電流生成回路とを備える。

(もっと読む)

電圧比較回路および半導体装置

【課題】消費電力の増大や応答速度の低下をきたすことなく、閾値のばらつきを抑えて確実な動作を可能とする電圧比較回路の提供を図る。

【解決手段】複数のトランジスタM1,M2,M11,M12,M21,M22を有する電圧比較回路であって、該複数のトランジスタの少なくとも1つの第1トランジスタM1(M2)は、制御端子と、該制御端子に供給される信号の電圧Vi+(Vi-)により接続が制御される第1および第2端子と、第1スイッチS2p(S2m)を介して所定の電位線PL2に接続されると共に、第1容量C1(C2)の一端が接続されたボディと、を有するように構成する。

(もっと読む)

遅延発生装置および半導体試験装置

【課題】差動ペアトランジスタを用いない比較器を備えた遅延発生装置およびこの遅延発生装置を備えた半導体試験装置を提供することを目的とする。

【解決手段】入力信号に対して設定された時間だけ遅延を持たせるための静電容量を有する遅延部111と比較基準電圧を生成するためのDAコンバータ110と遅延部から出力される出力電圧と比較基準電圧とを比較する比較器1とを備える遅延発生装置であって、比較器1は、比較基準電圧Vthに基づく閾値と出力電圧とを比較して反転するインバータ回路2Aと、インバータ回路2Aの正側電位Vd1を設定する第1の電圧源5と、インバータ回路2Aの負側電位Vs1を設定する第2の電圧源6と、を備えている。

(もっと読む)

自己制限型正帰還を有する比較器

比較器における正帰還を減衰するための方法および回路は、一実施形態では、第1の入力信号(104)を第2の入力信号(106)と比較し、比較に基づいて出力(108)を供給するように構成された増幅器(102)と、増幅器(102)の出力に動作可能に接続された第1の入力(112)を有する非線形機能(110)と、非線形機能(118)の出力(120)および非線形機能(110)の第2の入力(114)に動作可能に接続された帰還ループ(122)とを含み、帰還ループ(122)は、非線形機能(110)の第2の入力(114)への帰還信号(120)を減衰するように構成された帰還制限回路(126)を含む。 (もっと読む)

半導体集積回路

【課題】電源ノイズ耐性の優れ、かつ低消費電流でかつ多段接続が可能な増幅回路を実現する。

【解決手段】第1の電位変換用トランジスタ対(MN1,MN2)および第2のプリチャージトランジスタ対(MP3,MP4)を用いて電流/電圧変換用の容量素子(CL1,CL2)の対向電圧をそれぞれ第1の電源(VDD)レベルおよび第2の電源(VSS)レベルにプリチャージする。このプリチャージ完了後、第1の電源から差動トランジスタ対(MP1,MP2)を介して定電流を入力信号(VIP,VIN)に応じて振り分けて容量素子に供給する。この容量素子への電流供給停止後、第1のトランジスタ対(MN1,MN2)をオン状態、第2のトランジスタ対(MP3,MP4)をオフ状態に設定し、出力ノード(2a,2b)の電圧のレベルシフトをして、出力信号(VON,VOP)を生成する。

(もっと読む)

コンパレータ回路

【課題】出力電圧信号の振幅を十分にとれない場合があった。

【解決手段】本発明は、しきい値電圧を決定する参照電圧を入力する第1、第2の端子と、基準電圧を入力する第3の端子と、前記基準電圧を基準とした、検出すべき電圧を入力する第4の端子と、前記第1、第2の端子を制御端子に接続され、前記参照電圧の電位差に応じた電流をそれぞれ流す、第1導電型の第1、第2のトランジスタと、前記第1のトランジスタと前記第4の端子との間に接続される第2導電型の第3のトランジスタと、前記第2のトランジスタと前記第3の端子との間に接続され、前記第3のトランジスタの流す電流に応じたミラー電流を流す第2導電型の第4のトランジスタと、を有し、前記第2、第4のトランジスタの中間ノードの電圧に応じた電圧を出力信号として出力するコンパレータ回路である。

(もっと読む)

ヒステリシスコンパレータ

【課題】 差動対に入力信号とオフセット電圧を入力し、この差動対に接続される負荷MOSトランジスタのゲートとドレインをたすき掛け接続する構成のヒステリシスコンパレータは、MOSトランジスタのサイズを調整することにより任意のヒステリシス幅を得ることができるが、ヒステリシス幅の1/2のオフセット電圧を与えなければならず、かつヒステリシス幅が半導体プロセスのばらつきによって変動してしまうという課題を解決する。

【解決手段】 差入力信号Vinと閾値Vthが入力される差動対30と負荷部31で構成され、ヒステリシス特性を有する第1のコンパレータ部と、負荷部32と差動対30で構成され、ヒステリシス特性を有さない第2のコンパレータ部の動作を、ヒステリシスコンパレータの出力Voutによって切り替えるようにした。第2のコンパレータ部が動作するときは、出力Voutが遷移する電圧は閾値Vthのみで決まるので、半導体プロセスの影響を受けない。

(もっと読む)

電圧比較器

【課題】消費電流を増加することなく高速化することが可能な電圧比較器の提供。

【解決手段】この発明は、差動増幅回路11、微分回路12、および出力増幅回路13を備えている。差動増幅回路11は、差動入力された信号を差動増幅して出力する。微分回路12は、差動増幅回路11の出力を微分し、この微分出力を出力増幅回路13の定電流トランジスタM7のバイアス電圧に加算する。

(もっと読む)

コンパレータ回路

【課題】短い判定時間を実現して高速化を図り、また高感度化も同時に実現する。

【解決手段】ノードN1,N2の間に2個のインバータを逆並列接続した正帰還部1と、正帰還部1への電源供給を行う電源用トランジスタMP3,MN3と、ノードN1,N2を正電源端子VDDに個々に接続するリセット用トランジスタMP4,MP5と、入力電圧に比例して内部抵抗を減少させる入力用トランジスタMN6,MN7と、入力用トランジスタMN6,MN7をノードN1,N2と接地GNDとの間に個々に接続する判定用トランジスタMN4,MN5と、ノードN1,N2に入力側がそれぞれ接続されたインバータINV1,INV2とを備える。

(もっと読む)

1 - 20 / 38

[ Back to top ]