Fターム[5J039JJ01]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 入力信号特性 (318)

Fターム[5J039JJ01]の下位に属するFターム

Fターム[5J039JJ01]に分類される特許

1 - 8 / 8

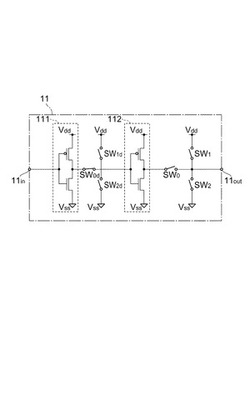

TDC回路

【課題】解像度が小さく測定精度が高い時間測定を行うことができるTDC回路を提供する。

【解決手段】TDC回路1は、共通の構成を有する32個の単位セル110〜1131がリング状に接続されたリング部10等を備える。単位セル11は、第1インバータ回路111,第2インバータ回路112,スイッチSW0,スイッチSW1およびスイッチSW2を含む。第1インバータ回路111のPMOSトランジスタのゲート幅は、第2インバータ回路112のPMOSトランジスタのゲート幅のαp倍である。第2インバータ回路111のNMOSトランジスタのゲート幅は、第1インバータ回路112のNMOSトランジスタのゲート幅のαn倍である。αpおよびαnの双方が1より大きいか又は双方が1より小さい。

(もっと読む)

時間計測回路およびデジタル位相同期回路

【課題】発振器の周期を基準として発振器の出力信号と基準信号との位相のずれを検出する。

【解決手段】多相化回路2は、差動発振信号P1、P2をM(Mは2以上の整数)分周することにより、位相が互いに180/M度ずつ異なる多相化信号S1〜SNを生成し、フリップフロップF1〜FNは、基準信号RCKの入力に同期して多相化信号S1〜SNをそれぞれ取り込み、デコーダ3は、フリップフロップF1〜FNの出力信号Q1〜QNをデコードする。

(もっと読む)

半導体集積回路装置および遅延路の制御方法

【課題】電力効率を向上させる。

【解決手段】クロック信号CLKに同期して動作する2つの同期動作回路11、12間を並列形態で接続して信号伝送可能とされる複数の遅延路13a、13b、・・13nと、複数の遅延路13a、13b、・・13nにおけるそれぞれの遅延時間を検出する遅延検出部14と、遅延検出部14の検出結果に基づいて複数の遅延路13a、13b、・・13nの内の一の遅延路を選択し、選択した一の遅延路以外における信号伝送を阻止するように制御する制御部15と、を備える。

(もっと読む)

デューティ感知回路およびこれを備えるデューティ補正回路

【課題】デューティ補正回路のロッキングタイムを減らし、正確なデューティの補正が可能となり、多様な周波数のクロックについてデューティ補正を可能にするデューティ補正回路を提供すること。

【解決手段】本発明に係るデューティ補正回路は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節した出力クロックCLK_OUT、CLKB_OUTを生成するデューティ調節部110と、前記出力クロックのハイパルス幅とローパルス幅の差異を測定してその差異値S<1:4>を出力するデューティ感知部120と、前記差異値を累積して前記デューティ調節コードを生成する累積部130とを備える。

(もっと読む)

半導体装置、内部信号タイミング回路、及び遅延時間測定方法

【課題】内部信号のタイミングを測定する場合、チップ内に形成されたトランジスタ等の素子における場所依存性によって特性が異なる場合にも、内部信号のタイミングを測定できる測定回路を提供する。

【解決手段】内部で実信号として用いられる第1及び第2の内部回路制御信号を生成する内部回路と、内部回路を通して受信される第1及び第2の内部回路制御信号を遅延時間測定開始信号及び遅延時間測定終了信号として受け、当該遅延時間測定開始信号及び遅延時間測定終了信号間の遅延時間を測定し、出力する遅延時間測定回路を備えた内部信号タイミング回路及び当該回路を含む半導体装置。

(もっと読む)

セットアップ/ホールドタイム測定装置

【課題】テスト信号に応じて外部クロック信号からデータ信号と内部クロック信号を生成し、読取り/書込み動作無しでバッファリングされたデータの状態によってセットアップ/ホールドタイムを測定できるようにしたセットアップ/ホールドタイム測定装置を提供する。

【解決手段】外部クロック信号をカウント信号によって遅延させ、テスト信号に応答して、前記遅れた外部クロック信号から内部クロック信号及びデータ信号を生成するデータ生成部と、前記内部クロック信号に同期して、前記データ信号をバッファリングした信号をラッチするデータラッチと、前記テスト信号に応答して、前記データラッチ部でラッチされたデータ信号からフラグ信号を生成するフラグ信号生成部と、前記フラグ信号に応答して前記カウント信号をカウンティングするカウンターと、を含む構成とした。

(もっと読む)

イコライザのテスト回路および集積回路の評価システム

【課題】量産テストでの使用に適したイコライザのテスト回路および集積回路の評価システムを提供する。

【解決手段】テスト回路1は、擬似乱数データ生成部11が、擬似乱数データを生成し、重み付け係数生成部12が、符号間干渉の干渉強度設定用の重み付け係数を生成し、擬似符号間干渉データ生成部13が、擬似乱数データのビット系列に応じて擬似乱数データに擬似的な符号間干渉を発生させ、重み付け係数により振幅を変化させた擬似符号間干渉データを生成し、ドライバ14が、生成された擬似符号間干渉データを差動信号として出力する。比較部15は、イコライザ100の出力をサンプリング回路200によりサンプリングしたデータを、符号間干渉発生前の元の擬似乱数データと比較し、カウント部16が、比較部15により検出された不一致の数をカウントする。

(もっと読む)

半導体集積回路装置および出力バッファ遅延変動検出方法

【課題】I/Oバッファの実際の配置場所及び実際の動作タイミングにおけるI/Oバッファの同時スイッチングによる出力バッファの遅延変動を容易に検出し、オーバーマージンな設計を回避できるようにした半導体集積回路装置を提供する。

【解決手段】差動アンプ152で、VSS変動の影響を受けている出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP1として求める。差動アンプ153で、VDE変動の影響を受けている出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP2として求める。差動アンプ154で、VDE・VSS変動の影響を受けていない状態での出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP3として求める。

(もっと読む)

1 - 8 / 8

[ Back to top ]