Fターム[5J039JJ05]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 入力信号特性 (318) | 周波数 (36)

Fターム[5J039JJ05]に分類される特許

1 - 20 / 36

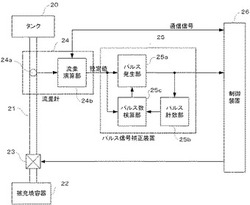

パルス信号補正装置およびそれを用いた充填装置

【課題】流量計と充填を制御する制御装置の間でノイズなどによって流量を表すパルスが増加あるいは消失すると、制御装置が正確な流量を把握できないので、正確に充填することができない。本発明はこのような課題を解決することを目的にする。

【解決手段】パルス信号補正装置を経由して流量計の出力を制御装置に入力する。パルス信号補正装置は流量計の出力と制御装置が受信したパルス数の差分を計算し、この差分に基づいて、次の出力周期で出力パルス数を補正するようにする。制御装置が正確な流量を得ることができるので、正確に充填できる。

(もっと読む)

CDR回路

【課題】前段の光受信装置のスケルチ機能の有無に関係なく汎用的に使用可能なCDR回路を提供する。

【解決手段】CDR回路は、入力データ1に同期した再生クロック2を出力するG−VCO14と、入力データ1の識別再生を再生クロック2に基づいて行うフリップフロップ回路12と、G−VCO14と同一周波数のクロックを出力するサブVCO15と、再生クロック2とサブVCO15の出力クロック4のいずれかを選択する選択回路17と、選択回路17の出力クロック8と参照クロック6とを周波数比較しその周波数差に応じた周波数制御信号5を出力する周波数比較器16とを備える。選択回路17は、少なくとも入力データ1が無信号である期間においてサブVCO15の出力クロック4を選択し、残りの期間において再生クロック2を選択する。

(もっと読む)

半導体装置、及びそのテスト方法

【課題】シリアルインタフェース回路におけるCDR回路の位相追従機能を、ループバックテストによって検査する。

【解決手段】本発明による半導体装置において、PLL回路2は、周波数変調された参照クロック1に基づいて、受信用クロック21及び送信用クロック22を生成する。シリアライザ3は、送信用クロック22に応じたタイミングでパラレルデータ33をシリアル化して出力する。CDR回路8は、受信用クロック21に基づいて、受信データ20に対するクロックデータリカバリを実行し、再生データ24を生成する。デシリアライザ14は、再生データ24をパラレル化する。ループバック回線19は、シリアライザ7から出力されたシリアルデータ18を、受信データ20としてCDR回路8に入力する。

(もっと読む)

PLLロック検出回路、及びPLLロック検出回路を有するPLLシンセサイザ回路

【課題】適切にPLL回路ロックがなされているか否かを検出する。

【解決手段】PLL回路ロックがなされているか否かを検出するPLLロック検出回路を構築する。ここにおいて、そのPLLロック検出回路は、基準発振器から供給される基準発振周波数を示す基準発振周波数信号と、前記基準発振周波数を分周して得られたリファレンス周波数を示し位相比較器に供給されるリファレンス周波数信号と、VCOから供給される電圧制御発振周波数を分周して得られた比較周波数を示し前記位相比較器に供給される比較周波数信号とを受ける、そして、前記リファレンス周波数信号と前記比較周波数信号とに基づいて、前記PLL回路ロックを示すロック検出信号を出力する。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも安定的な動作が可能でかつ出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10の出力端子とVCO11の入力端子との間に設けられたバッファ増幅器16と、VCO11の出力端子とVCO13の入力端子との間に設けられたバッファ増幅器17とを備える。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4のタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、VCO11,13の発振周波数を制御する制御信号8を発生する周波数制御回路である周波数比較器2およびVCO12と、VCO11の出力端子とVCO13の入力端子との間に挿入された減衰器30とを備える。

(もっと読む)

半導体集積回路装置、及び電源電圧制御方法

【課題】短時間に電源電圧を最適値に制御することが可能な半導体集積回路装置を提供することである。

【解決手段】本発明にかかる半導体集積回路装置100は、ターゲット回路2と、ターゲット回路2に電源電圧を供給する電圧供給回路4と、電圧供給回路4の出力電圧を制御する制御回路3と、ターゲット回路2に供給される電源電圧の電圧値を予測する目標電圧予測回路1とを備える。制御回路は、ターゲット回路2の要求動作周波数が第1の動作周波数から第2の動作周波数に変化した際に、電圧供給回路4の出力電圧を所定の電圧値だけ変化させる。目標電圧予測回路1は、所定の電圧値の変化にともなうターゲット回路2の動作周波数の変化量を検出すると共に、動作周波数の変化量と所定の電圧値との関係に基づいて目標電圧値を算出する。電圧供給回路4は、ターゲット回路2に目標電圧値の電源電圧を供給する。

(もっと読む)

中波放送機の発振部

【課題】2台の水晶発振器を備え、一方の水晶発振器が出力する周波数信号を利用して発振する中波放送機の発振部において、2台の水晶発振器各々の発振器の出力周波数のズレを監視し、ズレが発見された場合に、アラーム信号を発生し、迅速な対応を即すことで、中波放送機の信頼性をより高める。

【解決手段】現用と予備の2台の水晶発振器の出力周波数を、常に比較若しくは監視し、周波数ズレが発生した場合に対応できるように発振制御を行う中波放送機の発振部とした。

(もっと読む)

デジタルロック検出装置及びこれを含む周波数合成器

【課題】デジタルロック検出装置及びこれを含む周波数合成器を提供すること。

【解決手段】本発明の一側面は、複数の制御ビートの入力を受け、複数の制御ビートのロッキング(Locking)の可否を通報するビート信号を生成し出力する比較部と、ビート信号から複数の遅延信号を生成した後、複数の遅延信号とビート信号を結合して1つのクロック信号を出力する遅延セルブロックと、クロック信号の遷移時点を検出し、その検出結果を反映するロック表示信号を生成する検出部を含むデジタルロック検出装置及びこれを用いた周波数合成器を提供することができる。

(もっと読む)

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

ジッタ低減回路および半導体集積回路

【課題】クロック信号に乗るジッタを低減することが可能なジッタ低減回路および半導体集積回路の提供を図る。

【解決手段】第1クロック信号CLK1の第1周波数を測定する第1周波数測定回路11と、第2クロック信号CLK2の第2周波数を測定する第2周波数測定回路12と、測定された前記第1および第2周波数を比較し、該第1および第2周波数が所定の関係に有るかどうかを判定する周波数比較判定回路20と、前記周波数比較判定回路からの第1制御信号CNT1を受け取り、前記第1クロック信号の遅延を制御して前記第2クロック信号によるジッタを低減する第1遅延制御回路41と、を有するように構成する。

(もっと読む)

デジタル位相検出器及びデジタル位相同期回路

【課題】デジタル位相検出器の時間分解能をデジタル制御し、回路規模・消費電力を低減する。

【解決手段】信号S1が入力される直列に接続された第1の遅延素子1011〜101Nと、信号S2が入力される直列に接続された第2の遅延素子1021〜102Nと、各々の第1の遅延素子の出力が与えられ、各々の第2の遅延素子の出力をクロックとするラッチ回路1031〜103Nと、前記ラッチ回路の出力値に基づいて信号S1のパルス幅を示すデジタルコードPWmを算出して出力するデコーダ回路104と、デジタルコードPWmと所定のデジタルコードPWrとを比較し、比較結果を出力する比較器105と、前記比較結果に基づいて前記第1及び第2の遅延素子の少なくともいずれか一方の遅延時間を制御する遅延制御回路106と、を備える。

(もっと読む)

PLL制御装置及びPLL制御方法

【課題】親機、複数台の中継機、複数台の子機を備えた大規模なシステムで符号長が比較的長い同期信号を用いても、安定したPLLの引き込みを実現可能とする。

【解決手段】このPLL制御装置では、TIM抽出回路101は入力信号からタイミング成分を抽出し、VCXOは供給される制御信号に基づき基準信号の位相及び/又は発振周波数を制御する。0次PLL回路102はタイミング成分の位相差に基づき基準信号の発振周波数範囲を設定するための制御信号を出力し、1次PLL回路103はタイミング成分の位相差に基づき基準信号の位相を制御するための制御信号を出力する。制御セレクタ105は、0次PLL回路102又は1次PLL回路103からの制御信号を順次切り替えてVCXOに供給する。

(もっと読む)

周波数異常検出回路

【課題】従来の、監視クロックが被監視クロックよりも高い周波数を使用する周波数異常検出回路は、高コストかつノイズ対策が必要で実装が困難であり、また、監視クロックが被監視クロックよりも低い周波数を使用する周波数異常検出回路は、クロック固着のタイミングによっては異常を検出できないだけでなく、リセット時にシフトレジスタを構成するすべてのレジスタ出力が“0”となるので、警報が発出されないようにする構成を別途設けなければならない問題があった。

【解決手段】クロック周波数の上限異常は被監視クロック数のカウント数と上限値との大小比較にて検出し、下限異常は、同期化した監視クロックの立ち上がりエッジにて出力する正極性パルスと、当該パルス出力で”High”を出力する初回エッジホールド回路出力と、下限値と被監視クロック数のカウント値の大小を比較するコンパレータ出力との論理積の出力にて検出すること。

(もっと読む)

パルス発生回路及びパルス発生回路を備えた電子機器

【課題】PVTに依存せずに安定した周波数を出力する。

【解決手段】出力する第1の出力信号Vf1の周波数を第1の制御電圧VC1で制御する第1の電圧制御発振器11と、第1の出力信号Vf1及び基準信号CLKに基づき第1の出力信号Vf1の周波数を一定に維持する第1の制御電圧VC1を生成する制御電圧生成部13と、を含む位相同期回路10と、出力する第2の出力信号Vf2の周波数を第2の制御電圧VC2で制御する第2の電圧制御発振器20と、第1の制御電圧VC1に基づき第2の出力信号Vf2の周波数を一定に維持する第2の制御電圧VC2を生成する制御電圧変換部30と、を含むパルス発生回路1。

(もっと読む)

半導体集積回路装置

【課題】遅延を有する論理回路から検出した信号を直接利用して、その論理回路の電源電圧の制御を行うような機構が求められている。

【解決手段】本発明は、本発明は、論理回路と、前記論理回路の遅延の変化に応じた周波数の検出信号を出力する遅延特性検出回路と、前記検出信号に応じて抵抗値が変化する抵抗素子と、前記抵抗素子の抵抗値の変化に応じて参照電圧を出力する参照電圧生成回路と、前記参照電圧を前記論理回路及び遅延特性検出回路に出力する電圧供給回路とを有する半導体集積回路装置である。

(もっと読む)

半導体集積回路装置および逓倍クロック生成方法

【課題】 エージング時に使用可能な同期逓倍クロック発生回路を提供することである。

【解決手段】 可変ディレイヤを用いた発振回路と、カウンタを用いた発振周波数制御回路とを有し、入力クロック周波数の逓倍の周波数のクロックを発生するクロック発生回路において、上記発振回路を入力クロックに同期させて動作させることで、入力クロックと同期した逓倍クロックを発生させる。

(もっと読む)

半導体集積回路

【課題】低消費電力化に適したAVS技術又はDVS技術を実現した半導体集積回路を提供すること。

【解決手段】半導体集積回路は、クリティカル・パスを形成する第1のフリップ・フロップ、組み合わせ回路及び第2のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第1の遅延回路及び第3のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第2の遅延回路及び第4のフリップ・フロップと、第2のフリップ・フロップの出力と第3のフリップ・フロップの出力とを比較する第1の比較回路と、第2のフリップ・フロップの出力と第4のフリップ・フロップの出力とを比較する第2の比較回路と、これら比較回路の出力に応じて、前記組み合わせ回路に供給される電源電圧を制御する制御回路とを備える。なお、第1の遅延回路による遅延時間と第2の遅延回路による遅延時間は異なる。

(もっと読む)

試験測定装置並びに位相拘束ループ及び方法

【課題】消費電力が大きくなく、位相ノイズが小さく、広い同調範囲のPLLを提供する。

【解決手段】位相検出器34は、基準信号路30及び帰還信号路32から入力の位相差を検出し、位相検出器出力を発生する。発振器32は、位相検出器出力に応答し且つこの位相検出器出力に基づいた発振出力Foutを発生する。この発振出力Foutが帰還信号路32に供給される。基準信号路30内のミキサ74は、基準信号Frefをダイレクト・デジタル・シンセサイザ72からの出力と混合する。基準信号路内のスイッチング機構80は、複数の異なるフィルタの1つを選択的にミキサ及び位相検出器の間に直列に配置する。

(もっと読む)

物体検出回路及びそれを備えた物体検出装置

【課題】受光素子にて検知されたパルス光の波長が判別可能であり、外乱光による影響をさらに低減し、検出精度の高い物体検出回路を実現する。

【解決手段】物体検出回路1は、パルス変調された光を照射する発光素子12と、被検出物体の有無に応じて発光素子12からの出力パルス光を受光する受光素子13と、受光素子13にて検知されたパルス光の波長を判別する信号検出回路19とを備える。

(もっと読む)

1 - 20 / 36

[ Back to top ]