Fターム[5J039KK01]の内容

Fターム[5J039KK01]に分類される特許

281 - 298 / 298

追跡および保持ピーク検出器回路

低い入力信号周波数で動作することができる、追跡および保持ピーク検出器回路は、入力信号のピーク電圧を保持するコンデンサと、コンデンサへのまたはコンデンサからの漏れ電流の影響を低減する論理回路とを含み、その結果、ピーク検出器回路の出力信号の自己スイッチングに対する防護を提供する。  (もっと読む)

(もっと読む)

集積回路

【課題】 内部回路が逓倍クロック信号に基づいて動作することによる電源変動の影響が、クロック信号出力回路に及ぶことを極力回避できる集積回路を提供する。

【解決手段】 電源配線14がデジタル回路群17を経由してクロック信号出力回路11に電源供給を行う経路中にローパスフィルタ22を配置し、電源配線14を伝搬しようとするノイズ成分をアナロググランド側に逃がして除去する。そして、クロック信号出力回路11による逓倍クロック信号fmの発振精度を向上させ、その逓倍クロック信号fmに同期して動作するデジタル回路群17における通信ブロック16の通信精度等を向上させる。

(もっと読む)

クロック信号出力回路

【課題】 電源電圧が変動する場合でも、逓倍クロック信号の出力精度を極力維持することができるクロック信号出力回路を提供する。

【解決手段】 周期カウンタ4では、基準クロック信号fsの周期をリングオシレータ1より出力される高速クロック信号frでカウントし、周期カウンタ24ではN分周された基準クロック信号fsの周期をN分周した高速クロック信号frでカウントする。そして、有効判定回路25は、周波数逓倍動作を開始した直後はマルチプレクサ26により周期カウンタ4側の周期データD1を選択して逓倍クロック信号fmを迅速に出力し、それ以降、周期カウンタ24によってカウントされた周期データD1’が有効になる時間が経過すると、当該周期データD1’を選択するようにマルチプレクサ26を切替えて周波数逓倍演算処理の対象とする。

(もっと読む)

2つのPLLを用いた微小時間差回路及び時間測定回路

【課題】1桁以上時間分解能を向上させることができる微小時間差回路及び時間測定回路を提供する。

【解決手段】所定の基準クロック信号を受け、第1発振周波数を発生する電圧制御発振回路を具える第1位相同期ループ回路と、前記第1位相同期ループ回路と同じ基準クロック信号を受け、前記第1発振周波数と異なる第2発振周波数を発生する電圧制御発振回路を具える第2位相同期ループ回路とを具え、前記第1位相同期ループ回路と前記第2位相同期ループ回路の出力信号の遅延時間差から微小時間を得る。

(もっと読む)

PWM信号の量子化装置及び量子化方法

【課題】 PWM信号の量子化処理時の量子化精度を向上した量子化装置及び量子化方法を提供する。

【解決手段】 量子化装置(1)は、PWM信号を入力し、入力したPWM信号を時間軸方向に所定数倍した信号を生成する増幅器(16)と、増幅器(16)からの出力信号を受け、出力信号の”H”または”L”区間の時間幅を量子化し、デジタル信号として出力する量子化回路(6)とを備える。

(もっと読む)

シグマデルタベースのフェーズロックループ

位相周波数検出器(PFD)と、チャージポンプと、電圧制御発振器とを含むシグマデルタベースのフェーズロックループ・デバイスが提供される。PDFは、基準信号とフィードバック信号とを受信し、基準信号とフィードバック信号との比較に基づく信号を出力する。チャージポンプは、PFDからの出力信号に基づくチャージを出力する。チャージポンプは、固定量の電流を流す第1の電流源と、可変量の電流を流す第2の電流源とを含む。電源制御発振器は、チャージポンプからの受け取ったチャージに基づくクロック信号を出力する。  (もっと読む)

(もっと読む)

データ伝送装置、およびデータ伝送方法

【課題】パラレルデータを、シリアルデータに正確に変換して所定のデータ伝送路に出力するデータ伝送装置、および、パラレルデータを、シリアルデータに正確に変換して所定のデータ伝送路に出力するデータ伝送方法を提供する。

【解決手段】伝送されてくるパラレルデータが同期している第1の基準クロックとは別の第2の基準クロックを生成するクロック生成部1311と、上記パラレルデータを、上記第2の基準クロックに基づく第2のパラレルデータに変換するASIC1313と、このASIC1313から出力された第2のパラレルデータを、上記第2の基準クロックに基づくシリアルデータに変換するシリアライザ1315とを、全て同一基板上に備えた。

(もっと読む)

半導体集積回路装置のタイミング制御回路

【課題】半導体集積回路装置の制御対象回路に与える制御信号が製造プロセスや電源電圧、周囲温度などの変動によって変動するのを抑制すること。

【解決手段】外部クロックextCLKに基づき基準信号actCLKを生成する中央制御回路2側に、遅延値を制御するディジタル値DCTRL[n:0]からなる遅延制御信号を生成する遅延制御回路6を設け、中央制御回路2からローカル制御回路3に対して基準信号と遅延制御信号とを供給する。ローカル制御回路3に設けた可変遅延回路7は、遅延値がディジタル値で制御される単位遅延回路を多段に接続して構成され、メモリセルアレイ1に供給する各種の制御信号を、前記基準信号を前記遅延制御信号のディジタル値が示す所定の遅延値だけ遅延したタイミングで生成する。

(もっと読む)

データ処理方法

【課題】 DIデータの取りこぼしの発生を防止する。

【解決手段】 水晶振動子23のクロック周波数を分周回路31で分周し、パルス信号を生成する。一方、STB信号検出部回路33は、STB DI更新信号を検出し、この検出部回路33の出力には、STB LOCK信号が送出される。カウンタ34は、STB信号検出後、一定時間の間“High”状態で、その後、次のSTB信号が到来するまで“Low”状態の信号を生成する。この “Low”状態の信号の後のSTB LOCK信号と分周回路31で生成されたパルス信号は、ダブルラッチ信号発生回路32に入力されると、ダブルラッチ信号発生回路32は、DIオン/オフ時間比選択信号によるDIオン時間の間にダブルラッチ信号を2回発生する。このラッチ信号が入力データラッチ回路35に与えられると、その出力にはデータ取りこぼしが回避されたデータ得られる。

(もっと読む)

クロック生成回路

【課題】

所望の分数逓倍、分周クロックを出力し、面積、電力の増大を抑止するクロック生成回路の提供。

【解決手段】

複数段の遅延回路10A1〜10A4を備え、入力される信号の遅延を測定する第1の遅延回路列と、第1の遅延回路列に対し信号伝播方向が逆向きに配置され、複数段の遅延回路10B1〜10B4を備えた遅延再現用の第2の遅延回路列と、を備え、第1の遅延回路列で遅延が検出された位置の遅延回路から出力される信号に基づき、前記遅延が検出された位置に対応する、前記第2の遅延回路列の遅延回路において、遅延回路の出力端子が入力端子に帰還されて閉ループを構成しリング発振回路を構成し、リング発振回路の発振出力が、第2の遅延回路列の出力端子から取り出される。第1の遅延回路列の前段には、制御信号に基づき、入力信号に対する出力信号の位相が可変に制御する位相補間器201、202を備え、第1の遅延回路列は、位相補間器201、202の出力信号の位相差を測定する。

(もっと読む)

駆動状態検出回路

【課題】交流駆動される被駆動体の駆動状態を検出する駆動状態検出回路に関し、付加的な回路を設けることなく、簡単な構成で被駆動体の状態を検出できる駆動状態検出回路を目的とする。

【解決手段】交流駆動される複数の被駆動手段(21、22)の駆動状態検出回路において、該被駆動手段に流れる交流電流を各々検出する電流検出手段(Rs1、Rs2、Rs3、Rs4、D1、D2)と、該電流検出手段で検出された複数の交流検出信号のうち最大検出出力する最大値出力手段(91)と、該出力手段の出力信号に係数乗算する係数乗算手段(94)と、電流検出された複数の交流検出信号を各々係数乗算手段(94)の出力信号とを比較し、各被駆動手段(21、22)の状態に応じた状態信号を出力する比較手段(95、96)と、この複数の状態信号を論理合成する論理合成手段(99)と、この出力に基づいて駆動状態検出信号生成する出力手段(100)とを有する。

(もっと読む)

同期式ディジタルフィルタ

【課題】 装置の小型化を図り、しかも、クロック信号に同期し、且つ入力信号に重畳されたノイズを除去する。

【解決手段】 入力信号は第1フリップフロップF/F1の入力端D、正入力論理積回路AND1と負入力論理積回路AND2の第1入力端に供給される。第1フリップフロップF/F1の出力信号は、正入力論理積回路AND1と負入力論理積回路AND2の第2入力端に供給される。正入力論理積回路AND1と負入力論理積回路AND2の出力信号は、マルチプレクサMUXの選択信号端S1,S0に入力され、この選択信号でマルチプレクサMUXのデータ入力を切り替えて、マルチプレクサMUXの出力信号を第2フリップフロップF/F2に入力し、第1、第2フリップフロップF/F1,F/F2のクロック信号入力端CLKに供給される基準内部クロック信号発生部OSCからの内部クロック信号により第2フリップフロップF/F2に出力信号を得る。

(もっと読む)

ジッタ印加回路、及び試験装置

【課題】広帯域、高分解能、大振幅の位相ジッタ成分を、クロック信号に容易に印加することができるジッタ印加回路を提供する。

【解決部】与えられるジッタデータに応じた位相ジッタ成分を含むクロック信号を生成するジッタ印加回路であって、与えられる基準信号に応じて発振信号を生成するPLL回路と、発振信号を遅延させたクロック信号を出力する可変遅延回路と、ジッタデータの低周波成分に基づいてPLL回路の発振周波数を制御し、発振信号に位相ジッタ成分の低周波成分を印加する低周波印加部と、ジッタデータの高周波成分に基づいて可変遅延回路における遅延量を制御し、クロック信号に位相ジッタ成分の高周波成分を印加する高周波印加部とを備えるジッタ印加回路を提供する。

(もっと読む)

スプレッドスペクトラムクロック生成器及びその変調方法

【課題】製造バラツキ、電源電圧、使用温度、使用周波数が変化しても所望の変調度の周波数変調クロックを供給可能とするスプレッドスペクトラムクロック生成回路を提供する。

【解決手段】制御信号に応じて制御周期間隔で発振周期を可変に制御する第1の遅延制御型発振回路104と、第1の遅延制御型発振回路の出力を分周したクロック信号fo1と、位相比較結果に基づき周波数制御信号Cを出力する制御回路103と、変調最大値Aを決定する変調最大値決定回路106と、変調最大値A内で変調制御信号αを生成する変調信号発生回路107と、出力クロック信号の発振周期を制御信号に応じ制御周期間隔に可変に制御する第2の遅延制御型発振回路108を備えている。

(もっと読む)

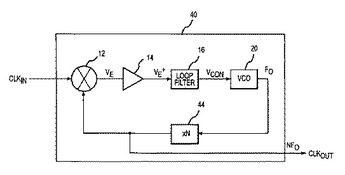

低電力と低いタイミング・ジッタのフェーズ・ロック・ループと方法

フェーズ・ロック・ループは、入力クロック信号から出力クロック信号を生成する。出力クロック信号は、クロック・ツリーを通して結合されて、出力クロック信号の位相を入力クロック信号の位相と比較する位相検出器にフィード・バックされる。出力クロック信号は、位相検出器から出力を受け取るように結合された制御入力を有する電圧制御発振器と、電圧制御発振器の出力に結合された周波数逓倍器とによって生成される。を持っている電圧制御発振器によって生成される。結果として、電圧制御発振器が相対的に低い周波数で動作することによって相対的に小さな電力を使用する一方、周波数逓倍器により生成されたCLKOUT信号は、相対的に高い周波数を持っている。  (もっと読む)

(もっと読む)

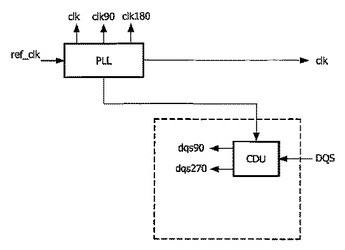

多重データレートRAMメモリコントローラ

多重データレートRAMメモリモジュールのメモリコントローラを備える。前記コントローラは、参照クロック(ref clk)から異なるクロック位相(clk、clk90、clk180)を生成するためのPLLユニット(PLL)を含む。さらに、ストローブ信号(dqs)を遅延させるための制御可能な遅延ユニット(CDU)を備える。  (もっと読む)

(もっと読む)

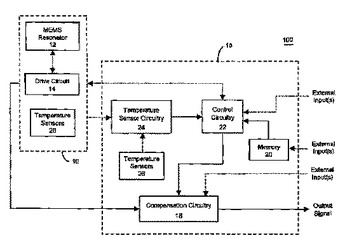

周波数および/または位相補償された微細電気機械発振器

本明細書で説明され、図示される多数の発明がある。1態様で、本発明は、出力信号を生成する微細電気機械共振器と、微細電気機械共振器の出力信号を受け取り、値のセットに応答して第2周波数を有する出力信号を生成するために微細電気機械共振器に結合された周波数調整回路構成と、を有する、補償された微細電気機械共振器を対象とする。1実施形態で、値を、微細電気機械共振器の動作温度および/または微細電気機械共振器の製造変動に依存する、微細電気機械共振器の出力信号の周波数を使用して、決定することができる。1実施形態で、周波数調整回路構成に、周波数逓倍器回路構成(たとえば、PLL、DLL、ディジタル/周波数シンセサイザ、および/またはFLLならびにこれらの任意の組合せおよびその組み合わせの変更)を含めることができる。周波数調整回路構成に、それに加えてまたはその代わりに、周波数分周器回路構成(たとえば、DLL、ディジタル/周波数シンセサイザ(たとえば、DDS)、および/またはFLL、ならびにこれらの任意の組合せおよびその組み合わせの変更)を含めることができる。  (もっと読む)

(もっと読む)

多電源半導体装置

複数のブロック31、32により構成され、各ブロック31、32が独立したクロック回路41、42を有し、可変電源101により動作する多電源半導体装置において、クロック生成回路10から複数のブロック32に供給されるクロック信号に、可変電源101の電圧値に基づいて遅延量が変化する可変遅延回路20を設ける。このことにより、可変電源101の電源電圧を変化させた場合でも、ブロック間のクロックスキューが低減される。 (もっと読む)

281 - 298 / 298

[ Back to top ]