Fターム[5J039KK01]の内容

Fターム[5J039KK01]に分類される特許

161 - 180 / 298

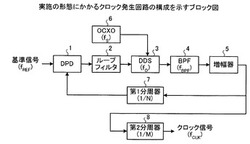

クロック発生回路

【課題】クロック発生回路において、コストの増大を回避すること。

【解決手段】ディジタル位相比較器1、ディジタルループフィルタ2、DDS3、バンドパスフィルタ4、増幅器5、OCXO6および第1分周器7は、ディジタルPLLを構成する。OCXO6から与えられるDDS3の動作周波数をfSとし、DDS3の出力設定周波数をfOとし、nを自然数とすると、DDS3からは、ディジタル/アナログ変換のイメージ成分として、[n×fS±fO]の周波数の信号が出力される。バンドパスフィルタ4は、このイメージ成分の周波数を通過帯域とする特性を有する。

(もっと読む)

クロック信号生成回路、及びクロック信号生成回路の使用方法

【課題】リングオシレータを利用して基準クロック信号の周波数を逓倍した逓倍クロック信号を生成するクロック信号生成回路において、逓倍クロック信号のジッタを抑制する。

【解決手段】高速クロック発生回路2の主要部であるリングオシレータへの電源供給を時定数がτに設定されたローパスフィルタ23を介して行い、高速クロック信号CKrで基準クロック信号CKs(周波数fs)の周期をカウントする周期カウンタ4のカウント値(周期カウント値)DGを、基準クロック信号CKsに従って動作する逓倍クロック生成回路5が、nクロック周期で、逓倍クロック信号CKoに反映させる。そして、基準クロック発生回路3は、周波数fsがτ>n/fsを満たす基準クロック信号CKsを発生させる。

(もっと読む)

信号伝達回路

【課題】新たな構成で複数種類の入力信号を1つのトランスを介して入力側から出力側へ伝達することが可能な信号伝達回路を提供することを目的とする。

【解決手段】温度入力信号が立ち上がると、トランス4の1次側コイルに第1のパルス電圧を発生させ、温度入力信号が立ち下がると、1次側コイルに第2のパルス電圧を発生させる1次側回路2と、トランス4の2次側コイルに第1のパルス電圧に対応するパルス電圧が発生すると、温度出力信号を立ち上がらせ、2次側コイルに第2のパルス電圧に対応するパルス電圧が発生すると、温度出力信号を立ち下がらせる2次側回路3とを有して信号伝達回路1を構成し、FAIL入力信号が立ち上がると、1次側コイルに第3又は第4のパルス電圧を発生させ、2次側コイルに第3又は第4のパルス電圧に対応するパルス電圧が発生すると、FAIL出力信号を立ち上がらせる。

(もっと読む)

半導体集積回路

【課題】従来の半導体集積回路においては、品種展開を行う際に追加のフォトマスクが必要となったり、品種の切り替え制御用として専用のボンディングパッドが必要となったりするという課題があった。

【解決手段】クロック入力とデータ入出力とを兼用する少なくとも2個の兼用ボンディングパッド11,12,13と、これらの兼用ボンディングパッドからの入力がクロック信号であるか否かを判定するクロック判定回路14と、このクロック判定回路からの出力に応じて動作する品種を決定する品種選択回路15とを備える。これにより、チップサイズを増加させることなく、また追加のフォトマスクを必要としない半導体製品の品種展開を実現する。

(もっと読む)

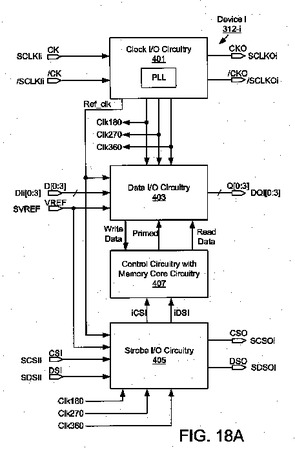

複数のデバイスおよび柔軟なデータ整列を用いるメモリコントローラを有するシステムにおけるクロック再生およびタイミング方法

システムは、メモリコントローラおよび直列接続されている複数の半導体デバイスを備える。各デバイスはデータを格納する。コントローラは、デバイスの動作を同期させるクロックを供給する。各デバイスは、イネーブル信号によって選択的にイネーブルまたはディセーブルされるPLLを備える。選択デバイスのPLLはイネーブル信号によってイネーブルされ、他のデバイスはディセーブルされる。イネーブルされたPLLは、90°の倍数の位相シフトで複数の再生クロックを供給する。データ転送は、再生クロックのうちの1つのクロックと同期する。ディセーブルされたPLLのデバイス内で、データ転送は入力クロックと同期する。イネーブルおよびディセーブルされたPLLにより、各デバイスはソース同期クロッキングおよび共通同期クロッキングを行う。最後のデバイスのデバイス識別子の最下位ビットがクロック整列を決定する。  (もっと読む)

(もっと読む)

クロック信号発生回路

【課題】簡単な回路構成により、低速の基準クロックから高速のクロック信号を生成することができ、高速クロック信号の周波数選択の制限を緩和することができるクロック信号発生回路を提供すること。

【解決手段】クロック信号発生回路100は、低速の基準クロック信号S1を発生する基準クロック信号発生回路110と、基本クロック信号発生回路110からの低速の基準クロック信号S1をN1逓倍し、逓倍出力S2を出力するPLL回路130と、PLL回路130の逓倍出力S2を1/N分周し、低速の基準クロック信号S1よりも高速の第2の基準クロック信号S3を出力する分周回路140と、分周回路140の第2の基準クロック信号S3をN2逓倍し、高速のクロック信号である逓倍出力S4を出力するPLL回路150とをこの順序で備える。

(もっと読む)

注入同期型発振器

【課題】より小型化が可能な周波数逓倍器を提供する。

【解決手段】注入同期型発振器20は、インバータ(22a、22b、22c)を3段リング状に接続してリングオシレータを備えている。そして、2段目のインバータ22bの出力と、3段目のインバータ22cの出力とをnMOSトランジスタ24で接続する構成を採用している。このnMOSトランジスタ24のゲートは、外部から基準周波数信号が供給される。このような構成によって、、リングオシレータの自励発振周波数に近い周波数であって、注入された基準周波数信号と同期した整数倍の周波数で発振が行われる。このように、インジェクションロックを用いて、位相雑音を減らすことができるので、ループフィルタを必要とせず、より小面積で周波数逓倍器を構成することが可能である。

(もっと読む)

A−D変換装置

【課題】電圧−周波数変換方式のA−D変換装置の精度を向上する。

【解決手段】2つの等価な鋸波発生回路18Aおよび18Bと、その2つの鋸波発生回路18Aおよび18Bを交互に切り替えるスイッチ回路19と、を含む電圧制御型発振器24を有する、電圧−周波数変換回路を備える。好ましくは、第1の周期の周期信号を出力する第1の電圧制御型発振器と、第1の周期と異なり、かつ第1の周期と一定の比を保つ第2の周期の周期信号を出力する第2の電圧制御型発振器とを備え、サンプリング周期内に含まれる第1の周期信号の波数に基づいて、入力であるアナログ信号に対応するディジタル信号の上位ビットを算出し、サンプリング信号の活性化時点から第1および第2の周期信号の位相が一致する時点までの間に含まれる周期信号の波数に基づいて、デジタル信号の下位ビットを算出する。

(もっと読む)

データ受信装置およびマイクロコンピュータ

【課題】CR発振回路に温度変化や経年変化が生じても正確な周波数を持つクロック信号を生成する。

【解決手段】CR発振器12の温度を示すA/D変換値とCR発振回路8の逓倍数を決める逓倍数設定値FMULRとを対応付けてEEPROM3に記憶し、A/D変換値(検出温度T)に応じた逓倍数設定値FMULRを読み出してCR発振回路8のレジスタに設定する。通信回路7が同期信号を受信するごとにクロック信号CLKを計数して1ビット長を計測し、その計数値XAと正規の1ビット時間に対する基準周期に基づく基準計数値XBとに基づいて逓倍数設定値FMULRを補正し、補正後の逓倍数設定値FMULRを検出温度Tに対応させてEEPROM3に書き込む。

(もっと読む)

半導体集積回路

【課題】発振回路により作成される動作クロックによる不要な電磁輻射ノイズを低減する。

【解決手段】乱数発生回路10から出力された乱数データは、周波数可変データレジスタ12に格納される。周波数可変データレジスタ12に格納されるデータは、乱数発生回路10から順次発生される乱数データによって更新される。発振回路13はクロックを発生する回路であり、クロックは不図示の動作クロック作成回路を通して動作クロックとして、内部回路14に供給される。発振回路13のクロックの周波数は、周波数可変データレジスタ12に格納された乱数データに応じて可変制御されるようになっている。また、周波数可変データレジスタ12に格納された乱数データに応じて可変制御される周波数の幅を制御するための制御データが格納される周波数可変幅制御レジスタ15が設けられている。

(もっと読む)

クロック発生回路

【課題】高精度な周波数変調が可能なスペクトラム拡散クロック発生回路を提供する。

【解決手段】このスペクトラム拡散クロック発生回路において、PLL回路31は、それぞれ位相の異なるクロック信号CLKV1〜CLKV5を出力する。セレクタ23は、クロック信号CLKV1〜CLKV5のうちのいずれか1つを選択し、制御回路24はセレクタ9の信号選択動作を制御する。入力分周回路1は選択クロック信号を分周して基準クロック信号CLKRを出力する。PLL回路21は、基準クロック信号CLKRを周波数逓倍した発振クロック信号CLKOを生成する。これにより、発振クロック信号CLKOの位相を微調整することができる。したがって、高精度な周波数変調が可能なスペクトラム拡散クロック発生回路が実現できる。

(もっと読む)

位相クロック発生器

【課題】より少ない数のトランジスターを使いながらも、高周波特性が反映されたクロック信号を生成でき、具現可能なクロック周波数帯域に限界がない位相クロック発生器を提供することと、回路サイズ及び電力消費量を最小化して、半導体設計及び工程が容易になり、トランジスターの動作周波数がそのまま反映された高周波クロック信号を生成することができ、ノイズ成分の影響を最小化することができる位相クロック発生器を提供する。

【解決手段】電源線及び接地線の間に繋がって4行とN列を構成して、多数の位相遅延信号をゲート端子を通じて入力されるトランジスターを含み、単位列を構成する4個のトランジスターの中で、一方の側の2個のトランジスターはNMOSでペアを構成し、他方の側の2個のトランジスターはPMOSでペアを構成して、前記単位列を構成するNMOSペアとPMOSペアの間のラインに繋がってクロック信号を送り出すバッファーを含む。

(もっと読む)

高電圧、高速、高パルス繰返し数のパルス発生器

【課題】RF電力増幅器と関連する高パルス繰返し数の制限を解決する高電圧、高速、および高繰返し数パルス発生器(30)を提供する。

【解決手段】パルス発生器(30)は共振技術を利用して、短絡および開回路の双方の負荷状態中に、パルス発生器(30)の機能障害なしに、パルス発生器(30)の継続的な高電圧、高速、および高繰返しパルス数動作を可能にする電流制限特徴をもたらす。本発明の好適な実施例において、パルス発生器(30)は、DC電圧を高周波AC電圧に変換するように構成されているインバータ(40)と、前記AC電圧に応答して、AC電流源として動作するように構成されているコンバータ(50)と、前記AC電流源によって発生するAC入力電流に応答して、高電圧、高速、高繰返し数電圧パルスを発生させるように構成されているパルス整形部分(60)とを備える。

(もっと読む)

信号追跡を行う信号生成器

入力信号を追跡するように出力信号の周波数及び位相が調整される。前記出力信号が導き出される発振信号の周波数を制御するように制御信号が調整される。幾つかの側面においては、前記発振信号の前記周波数は、発振器回路に結合されたリアクティブ回路の再構成によって調整される。前記出力信号の位相は、前記発振信号と調整可能スレショルドの比較に基づいて調整することができる。例えば、前記調整可能スレショルドは、トランジスタ回路に関する調整可能バイアス信号を備えることができ、それにより、前記発振信号は、前記トランジスタ回路への入力として提供され、前記トランジスタ回路の前記出力は、前記出力信号を提供する。 (もっと読む)

可変周波数発振回路

【課題】 回路規模が小さく、半導体装置を誤動作させにくい可変周波数発振回路を提供する。

【解決手段】 1個の発振回路3が使用されるので、回路規模が大きくならない。周波数制御信号SFが切り替わり、定電流I2〜I3がそれぞれ切り替わり、定電流I2〜I3にリンギングが発生すると、リンギングの発生期間に、パルス信号SPがハイになって発振回路3に入力するようになり、そのパルス信号SPによって発振回路3から出力されたクロック信号CLKがローに固定されて発振回路3は通常の発振動作を行わなくなるので、意図しない周波数のクロック信号が発生しなくなる。

(もっと読む)

タイミング発生回路

【課題】

周期が一定であるかまたは変化し、一周期の間に少なくとも2つのレベルで遷移する処理対象信号の当該レベル遷移のタイミングを細かく設定できる回路技術を提供する。

【解決手段】

(A)第1周期信号、第2周期信号、・・・、第M周期信号をそれぞれ出力する周期信号発生回路11と、(B)第1〜第M周期信号を計数する第1〜第M計数回路からなる計数回路群12と、(C)前記所定タイミングの値を時間軸で配分して、前記所定タイミングの時間軸で配分した値を、第1周期信号の周期個数N1、第2周期信号の周期個数N2、・・・、第M周期信号の周期個数NMで表し、第1周期信号の周期個数N1を前記第1計数回路に、

第2周期信号の周期個数N2を前記第2計数回路に、

・・・

第M周期信号の周期個数NMを前記第M計数回路に、

セットする設定装置13とを備える。

(もっと読む)

PLL発振回路

【課題】分数分周型のPLL発振回路における抵抗やキャパシタの定数を小さくすると共に、雑音を低減する。

【解決手段】入力信号INと帰還信号FBaの周波数の差に応じた電流を共通のノードNcに出力する周波数比較器10aと、入力信号INと帰還信号FBbの周波数の差に応じた電流を共通のノードNcに出力する周波数比較器10bと、このノードNcに出力される信号の高周波成分を除去して制御電圧VCを生成するループフィルタ20と、制御電圧VCに応じた周波数foの出力信号OUTを生成するVCO30と、出力信号OUTの周波数をそれぞれ1/Mと1/Nに分周して帰還信号FBa,FBbを出力する分周器40a,40bを設ける。

(もっと読む)

発振回路

【課題】高精度な発振回路を提供する。

【解決手段】例えば、奇数段のインバータ回路IVを含んだ複数のリングオシレータ部RO1,RO2と、このRO1,RO2の出力ノードRO_O1,RO_O2の信号を加算する加算部ADDを設ける。そして、このADDの加算結果をクロック信号として出力ノードOSC_Oから出力すると共に、この出力ノードOSC_OをRO1,RO2の入力ノードRO_I1,RO_I2に帰還する。これによって、例えばRO1,RO2の遅延時間がそれぞれ標準偏差σの正規分布に基づいてばらつく場合に、OSC_Oから得られるクロック信号のばらつきをσ/√2とすることが可能となる。

(もっと読む)

周波数可変オシレータ

【課題】本発明は、入力信号の周波数が可変されも可変された入力信号の周波数により発振信号の周波数を可変する周波数可変オシレータに関するものである。

【解決手段】本発明は、入力信号の電圧レベルを事前に設定された範囲の電流レベルに変換する電圧電流変換回路と、上記電圧電流変換回路からの電流レベルにより周波数を可変して発振する発振回路を含むことを特徴とする。

(もっと読む)

アナログ信号比較器

【課題】

アナログ信号の値を、比較的簡易な回路でかつ短時間で、所定の値と比較する。

【解決手段】

第1のパルス信号を生成する発振器21Aと、アナログ信号を入力し当該アナログ入力信号を第2のパルス信号に変換して出力するVCO22と、発振器21からの第1のパルス信号を入力する第1のシフトレジスタ241と、VCO22からの第2のパルス信号を入力する第2のシフトレジスタ242と、第1および第2のシフトレジスタ241,242の全ビットまたは一部ビットの値を検出し、これらの検出値に基づき、発振器21Aが生成する第1のパルス信号の個数と、VCO22が生成する第2のパルス信号の個数とを比較するパルス個数比較回路とを備えたことを特徴とするアナログ信号比較器。

(もっと読む)

161 - 180 / 298

[ Back to top ]