Fターム[5J039KK01]の内容

Fターム[5J039KK01]に分類される特許

81 - 100 / 298

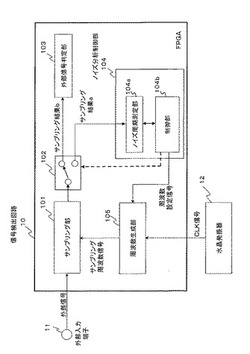

信号検出回路および誤検出防止方法

【課題】周期性を有するノイズによる誤検出を防止する信号検出回路および誤検出防止方法を提供する。

【解決手段】サンプリング周波数信号に従って外部信号をサンプリングするサンプリング部(101)と、サンプリング結果から周期性ノイズの周期を測定するノイズ周期測定部(104a)と、サンプリング結果から外部信号のレベルを判定する外部信号判定部(103)と、ノイズ周期測定時にサンプリング周波数信号をノイズ検出可能な所定の周波数に設定し、その時のサンプリング結果aをノイズ周期測定部へ転送し、ノイズ周期測定後に、サンプリング周波数信号を、測定されたノイズ周期に相当する周波数と一致しない周波数に設定し、その時のサンプリング結果bを外部信号判定部103へ転送するように制御する制御部(104b)と、を有する。

(もっと読む)

位相検出回路および方法

【課題】 相当量の電力を消費し、かつジッタを生成する分周器回路を必要とせずに、高周波周期出力信号を生成する位相ロックループを提供すること。

【解決手段】 位相検出器回路は、第1および第2周期入力信号の位相を比較して、出力信号を生成する。位相検出器は、第1および第2周期入力信号の2つの異なる組み合わせを作り、第3および第4周期信号を生成する回路を備える。この回路は、第3周期信号を、第1相対位相シフトを付与する、第1周期信号および第2周期信号の第1の組み合わせに基づかせる。この回路は、第4周期信号を、第1周期信号および第2周期信号の第2の組み合わせに基づかせて、異なる相対位相シフトを提供する。位相検出器は、また、第3周期信号の電力の大きさを第4周期信号の電力の大きさと比較して、位相比較出力信号を生成する比較回路も備える。

(もっと読む)

クロック装置

【課題】複数のクロック信号を出力するPLL回路において、その特性を問わず、リセットを従来よりも適切なタイミングで行うことを目的とする。

【解決手段】クロック装置は複数のクロック信号を出力するクロック回路を備え、出力するクロック信号を使用して動作している複数の周辺回路からエラー信号を受信し、受信したエラー情報を用いて、前記クロック回路をリセットするか否かを判定し、リセットすると判定した場合に、前記クロック回路をリセットする。

(もっと読む)

スプレッドスペクトルクロック発生器及びそれを含む電子装置

【課題】新しい変調率及び変調周波数を有するスプレッドスペクトルクロック信号を生成することができるスプレッドスペクトルクロック発生器を提供する。

【解決手段】スプレッドスペクトルクロック発生器は、第1スプレッドスペクトルクロック信号を受信して第1スプレッドスペクトルクロック信号の平均周波数に対応する周波数信号を出力する発振回路と、周波数信号を受信して第2スプレッドスペクトルクロック信号を発生する位相固定ループと、第1及び第2スプレッドスペクトルクロック信号を受信して、第2スプレッドスペクトルクロック信号の平均周波数が第1スプレッドスペクトルクロック信号の平均周波数と近接するように位相固定ループを制御する制御回路を含む。このようなスプレッドスペクトルクロック発生器は、スプレッドスペクトルクロック信号を受信して、希望する変調率及び変調周波数を有する新しいスプレッドスペクトルクロック信号を発生する。

(もっと読む)

送信装置および通信システム

【課題】 従来の送信装置では、クロックとデータとの間のスキューが変動した場合にも高精度の通信を実現することが困難であった。

【解決手段】 N(Nは自然数)ビットの第1のパラレルデータ信号を、基準クロックをN逓倍した第1変換クロックでパラレル/シリアル変換を行い、N×K(Kは自然数)ビットの第2のパラレルデータ信号を、基準クロックをN×K逓倍した第2変換クロックでパラレル/シリアル変換を行う。

(もっと読む)

クロック発生装置

【課題】出力するクロックの周波数を意識的に拡散して、テレビ受像機やパソコンモニタ映像受像機への電磁妨害のピークを減らすクロック発生装置を提供する。

【解決手段】周波数拡散情報発生回路90を設け、第二のDTO91と第二のDAC92にてデジタルLPF8から出力される位相誤差情報と周波数拡散情報から正弦波を発生し、アナログPLL93で逓倍することにより、クロック出力端子94から周波数拡散されたクロックを出力することができ、システムが用いる高い周波数からでる妨害を抑制するために意識的に周波数を拡散できるクロック発生装置を得ることができる。

(もっと読む)

クロック信号制御装置および画像形成装置

【課題】周波数拡散によって拡散調整された周波数スペクトラムのピークの重なりを防ぎ、複数の電子機器について周波数拡張変調を行う際のEMI低減効果を確保する。

【解決手段】クロック信号制御装置は、所定の周波数のクロック信号を生成するクロック信号生成部と、クロック信号生成部によって生成されたクロック信号を拡散変調する周波数拡散変調部と、周波数拡散変調部が行う拡散変調の変調タイプの設定を制御する変調タイプ設定制御部とを備える。周波数拡散変調部は、変調タイプ設定制御部の制御によって複数の変調タイプから変調タイプを選択して設定し、設定した変調タイプに基づいてクロック信号を拡散変調する。複数の周波数拡散変調部において異なる変調タイプで周波数拡散を行い、周波数拡散によって拡散調整された周波数スペクトラムの各ピークが重ならないようにし、ピーク値の上昇を抑制してEMIを低減する。

(もっと読む)

適応デジタル位相ロックループ

【課題】従来のデジタルPLLで問題であった出力クロックの位相ノイズ及びジッタ性能の低下に対応するアプローチを提供する。

【解決手段】幾つかの実施形態で、デジタルPLLは、例えば位相エラー等の1又はそれ以上の実時間性能パラメータに応答して有効なDPLL帯域幅を変更する動的制御可能なフィルタを有して開示される。高帯域幅が必要とされないとき、それは比較的低いレベルであるよう制御されてよく、それによって、出力クロックのジッタは低下する。他方で、高帯域幅が必要とされるとき、例えば、ループでの位相エラーが高いとき、フィルタは、基準クロックを追跡するためにループの応答性を高めるよう比較的高いループ帯域幅を提供するように制御され得る。

(もっと読む)

モータ用位相同期回路及びそれを用いたスピンドルモータ

【課題】入力信号の周波数が変化するようなモータの駆動制御において、ステップ入力などのように入力信号の位相が急激に変化した場合でも、オーバーシュートやスリップによる振動などの過渡的な振動の発生を抑制することができる多重PLL回路の構成を得る。

【解決手段】第2PLL21の第2位相比較回路24によって検出される位相差が所定範囲外である場合には、ループ加算器26を介さずに、第1PLL11を用いて第2PLL21のモータ部22を制御する一方、上記位相差が所定範囲内である場合には、上記ループ加算器26を介して上記第1PLL11と上記第2PLL21とを接続して多重PLL回路を構成するように、信号経路切換部33によって、該第1及び第2PLL11,12の信号経路を切り換える。

(もっと読む)

パルス発生器を電力較正するためのシステムおよび方法

電力または電流の較正機能を含む出力信号(例えば、規定パルス)を発生するための装置が開示される。 装置は、出力信号を生成する第1電流を発生するように適合された電流源、第1の電流の関数(例えば、実質的に比例するかまたは等しい)として第2電流を発生するように適合された電流サンプリングモジュール、第3電流を発生するように適合された基準電流モジュール(例えば、バンドギャップ電流源)、および、第2および3電流に基づいて第1電流を校正するように適合された較正モジュールを具備する。電流源は複数の選択可能な電流パスを具備する。電流サンプリングモジュールは、電流源の一つまたは複数の電流パスの少なくとも一部のレプリカを具備する。較正モジュールは、規定時間、環境パラメータ(温度、電圧、パルス繰り返し周波数、振幅要件変化など)、または発生されていない出力信号に応えて較正を行う。 (もっと読む)

半導体集積回路装置、及び電源電圧制御方法

【課題】短時間に電源電圧を最適値に制御することが可能な半導体集積回路装置を提供することである。

【解決手段】本発明にかかる半導体集積回路装置100は、ターゲット回路2と、ターゲット回路2に電源電圧を供給する電圧供給回路4と、電圧供給回路4の出力電圧を制御する制御回路3と、ターゲット回路2に供給される電源電圧の電圧値を予測する目標電圧予測回路1とを備える。制御回路は、ターゲット回路2の要求動作周波数が第1の動作周波数から第2の動作周波数に変化した際に、電圧供給回路4の出力電圧を所定の電圧値だけ変化させる。目標電圧予測回路1は、所定の電圧値の変化にともなうターゲット回路2の動作周波数の変化量を検出すると共に、動作周波数の変化量と所定の電圧値との関係に基づいて目標電圧値を算出する。電圧供給回路4は、ターゲット回路2に目標電圧値の電源電圧を供給する。

(もっと読む)

精密三角波形生成器

【課題】三角波形の品質をさらに正確に制御するためのシステムおよび方法を提供すること。

【解決手段】三角波形生成器は、容量素子、調整器、および制御回路を含むものとして規定される。調整器は、第1の制御信号に応答して容量素子を充電し、第2の制御信号に応答して容量素子を放電するように構成される。制御回路は、基準波形に応答し、第1および第2の制御信号を生成する。一例において、制御回路は、基準波形の振幅、周波数、位相、および対称性に応答して、第1および第2の制御信号を生成する。

(もっと読む)

半導体集積回路

【課題】広い周波数範囲で高調波電流成分を削減して高周波ノイズを低減することのできる半導体集積回路の提供を図る。

【解決手段】クロック信号CKに同期して動作する複数のデジタル回路11,12を含む半導体集積回路であって、前記各デジタル回路は、周波数が同じで位相が異なる第1および第2クロック信号CKa,CKbの一方を受け取り、前記第1および第2クロック信号の位相差は、m,nを自然数として、ほぼ[2m−1]/2nであるように構成する。

(もっと読む)

クロック情報及びデータ情報を含む信号を受信する受信器、並びにクロック埋め込みインターフェース方法

【課題】クロック情報及びデータ情報を含む信号を受信する受信器、並びにクロック埋め込みインターフェース方法を提供する。

【解決手段】クロック情報及びデータ情報を含む差動信号対を受信するにおいて、差動信号対の共通電圧レベルの変化を利用してクロック信号及びデータを復元できる、クロック情報及びデータ情報を含む信号を受信する受信器及びクロック埋め込みインターフェース方法である。

(もっと読む)

半導体集積回路及び半導体集積回路の発振異常検出方法

【課題】オシレータ出力、又はPLL出力、又はリングオシレータ出力のいずれかに発振異常が発生しているか否かを判定できる半導体集積回路を提供する。

【解決手段】本発明の半導体集積回路1は、第1の発振器(オシレータ2)と、第2の発振器(PLL3)と、第3の発振器(リングオシレータ4)と、第1の発振器2のクロック、第2の発振器3のクロックを第3の発振器4のクロックに基づいて順に切り替えて出力するセレクタ6と、セレクタ6から出力されたクロックを、第3の発振器4のクロックに基づいてアップカウント又はダウンカウントし、アップカウント又はダウンカウントの結果に基づいて、セレクタ6から出力されたクロックと、第3の発振器4のクロックとの整合性を判定し、いずれかのクロックに発振異常が発生しているか否かを判定する判定回路7と、を備える。

(もっと読む)

同期化結晶発振器ベースのクロックを採用するシステム

【課題】改良された同期クロックシステムを提供する。

【解決手段】同期クロック信号を必要とする複数のシステムノードを有する電子システム用の同期クロックシステム。クロックシステムは、第1の同期バスと第1の同期バスから絶縁された第2の同期バスと、交互にバスに接続された少なくとも1対、そして好ましくは複数対のSXOモジュールを含む。システムノードの各々は、第1のバスに沿った任意の場所において適宜選択されたあらゆる接続点のうちの異なる1つで接続される。SXOモジュールが接続されるバスに沿った点は、およそ等間隔で隔てられる。システムノードは信号調整回路を用いてバスに接続され、信号調整回路は、補正回路、増幅器、周波数逓倍器、論理変換器、およびファンバッファを含んでいてもよい。

(もっと読む)

スイッチングドライバ回路

【課題】ディスクリート部品を用いることなく、パルス時間が長く、しかも、電圧変動が大きいノイズを確実に除去可能とする。

【解決手段】

入力信号の立ち上がり、立ち下がりを検出し、エッジ検出信号を出力するエッジ検出回路101と、入力信号を所定シフト時間t1シフトして出力するシフトレジスタ回路106と、エッジ検出回路101のエッジ検出信号の入力時点から所定入力時間t2経過後にカウントアップ信号を出力するカウンタ回路102と、シフトレジスタ回路106の出力信号を、カウンタ回路102のカウントアップ信号に同期して出力するDFF回路103と、DFF回路103の出力信号を外部へ出力する出力回路104と、シフトレジスタ回路106とカウンタ回路101のクロック信号を生成、出力する発振回路105とを具備してなり、所定入力時間t2に満たない入力信号が出力されないようになっている。

(もっと読む)

クロック供給システム及び画像形成装置

【課題】SSCGの変調度を大きくすることなく、且つ低コストで、複数の電子部品から放射されるノイズを効果的に低減する。

【解決手段】一定周波数の第1クロック信号を生成する第1クロック生成器と、前記第1クロック信号の周波数変調を行うことで周期的に周波数が変動する第2クロック信号を生成する第2クロック生成器と、複数のクロック供給対象回路で使用される前記第2クロック信号の位相が、前記クロック供給対象回路毎に異なるように位相調整を行う位相調整回路とによってクロック供給システムを構成する。

(もっと読む)

システムにおけるフォールトトレラントなスペクトラム拡散クロック信号の提供

【課題】システムにおけるフォールトトレラントなスペクトラム拡散クロック信号を提供する。

【解決手段】フォールトトレラントなスペクトラム拡散クロック信号を供給するために、それぞれスペクトラム拡散制御回路を有する複数の処理モジュールが提供される。冗長なクロック供給源のクロック信号は、前記複数の処理モジュールに対して供給されるファイルオーバー制御ロジックは前記複数の処理モジュールそれぞれにおいて使用するために前記冗長なクロック供給源から前記クロック信号のうちの対応する1つを選択する。周波数拡散が、少なくともいくつかの前記複数の処理モジュールそれぞれにおいて前記対応する選択されたクロック信号に適用される。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

81 - 100 / 298

[ Back to top ]