Fターム[5J039KK01]の内容

Fターム[5J039KK01]に分類される特許

41 - 60 / 298

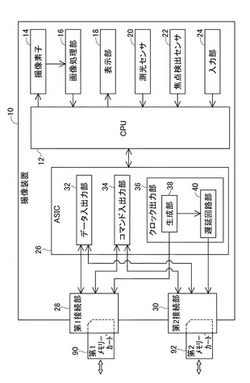

電子機器

【課題】複数の接続部に動作クロックを出力すると、それぞれのクロックの立ち上がり及び立ち下がりにより生じる電磁波の周りへの影響が大きい。

【解決手段】電子機器は、信号の授受する動作クロックの周波数が同じ複数の外部機器が接続される複数の接続部と、複数の接続部に対して互いに位相をずらした動作クロックを出力するクロック出力部とを備える。クロック出力部は、複数の接続部のうちの2つに対して互いに逆位相の動作クロックを出力する。

(もっと読む)

注入同期発振器

【課題】逓倍数が任意の大きな数であっても、位相雑音が低減された注入同期発振器を得る。

【解決手段】注入同期発振器は、注入される注入信号に同期して自励発振周波数の信号を発振する発振器を備える注入同期発振器において、上記自励発振周波数と略同じ周波数の逓倍数分の1の周波数の基準信号が入力されるともに該基準信号にトリガーされてパルスを生成するパルス発生回路と、上記パルス発生回路で生成したパルスとタイミングが異なる少なくとも1つのパルスを生成するとともに該生成されたパルスと上記パルス発生回路で生成したパルスとを合わせて注入信号として出力するパルス数増倍回路と、を備える。

(もっと読む)

PWM制御のデューティ決定方法

【課題】通信周波数を微小変動させる技術よりも、ノイズレベルの低減を更に図ることができるPWM制御のデューティ決定方法を提供する。

【解決手段】制御IC63が、駆動回路に出力するPWM信号のデューティを、指令値を中心に、所定期間内における平均が前記指令値に一致するように微小変動させる場合、PC68のデータベース69に、実際にPWM信号を駆動回路に与えることで発生したノイズ成分のレベル測定結果を反映したデータを、そのデューティの変動態様と共に記憶する。そして、データベース69に記憶されているデータを参照し、与えられた動作環境や動作条件等に応じて抑圧対象となる周波数帯のノイズレベルを低減するように、制御IC63によるPWMデューティの変動態様を決定する。

(もっと読む)

パルス変調型光検出装置及び電子機器

【課題】被検出対象が無いにも関わらず、物体有りと誤って判定される誤動作が生じないパルス変調型光検出装置及び電子機器を提供する。

【解決手段】パルス変調型光検出装置50は、増幅パルス信号S5と同期タイミングパルス信号S2とが同期するか否かを判定し、増幅パルス信号S5と同期タイミングパルス信号S2とが同期していないと判定したとき、同期タイミングパルス信号S2の生成を停止させる停止信号S501を同期タイミング回路5へ出力する外乱光検知部200を備える。

(もっと読む)

位相比較器およびクロックデータリカバリ回路

【課題】充放電流を切り替えるスイッチを確実に動作させ、高速化に対応できチャージポンプ回路の機能を保持できる位相比較器およびクロックデータリカバリ回路を提供する。

【解決手段】入力データと第1のラッチ111のラッチデータの論理不一致を検出する第1の検出回路と、第1のラッチのラッチデータと第2のラッチ112のラッチデータの論理不一致を検出する第2の検出回路と、第1の検出回路および第2の検出回路の検出結果に応じて、電流を充電または放電を切り替えるための切替スイッチ機能を含むチャージポンプ回路と、を有し、第1の検出回路、第2の検出回路、およびチャージポンプ回路は、第1および第2の検出回路の論理不一致判定部とチャージポンプ回路の充放電流を切り替える切替スイッチとが複合化された検出回路複合型チャージポンプ回路120として形成されている。

(もっと読む)

位相同期回路及び無線機

【課題】位相同期回路のセトリング時間を短縮する。

【解決手段】位相同期回路は、制御信号に応じた発振周波数を含む発振信号を生成する電圧制御発振器と、前記発振信号を分周して分周信号を生成する分周器と、前記分周信号と基準信号との位相を比較し、比較信号を生成する位相比較器と、前記比較信号に応じた電流を出力するチャージポンプと、前記電流をフィルタリングし、前記制御信号を生成するフィルタと、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分が極小となった場合に検出信号を生成する周波数差検出回路と、前記検出信号が生成されると、前記分周信号と前記基準信号との位相を同期させる位相調整回路とを備える。

(もっと読む)

PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

(もっと読む)

多相クロック生成回路

【課題】N相から2N相に切り替わったときに位相関係が不適切にならないようにする。

【解決手段】多相クロック生成回路は,基準クロックに同期して0°,90°の位相の中間クロックを生成する第1の分周器と,0°の中間クロックに同期して0°,90°の位相の第1群の出力クロックを生成する第2の分周器と,90°の中間クロックに同期して45°,135°の位相の第2群の出力クロックを生成する第3の分周器と,第1の分周器と第3の分周器との間に設けられ,切替信号に応じて,90°の中間クロックまたは固定値のいずれかを第3の分周器に供給するセレクタとを有する。さらに,切替信号が2N相モードのときに,第1群の出力クロックと第2群の出力クロックの位相関係にエラーがあるか否かを検出するエラー検出回路と,エラー検出回路がエラーを検出したときに基準クロックと非同期のタイミングで2N相モードの切替信号をセレクタに出力する再リセット回路とを有する。

(もっと読む)

時間計測回路およびデジタル位相同期回路

【課題】発振器の周期を基準として発振器の出力信号と基準信号との位相のずれを検出する。

【解決手段】多相化回路2は、差動発振信号P1、P2をM(Mは2以上の整数)分周することにより、位相が互いに180/M度ずつ異なる多相化信号S1〜SNを生成し、フリップフロップF1〜FNは、基準信号RCKの入力に同期して多相化信号S1〜SNをそれぞれ取り込み、デコーダ3は、フリップフロップF1〜FNの出力信号Q1〜QNをデコードする。

(もっと読む)

TDC回路

【課題】解像度が小さく測定精度が高い時間測定を行うことができるTDC回路を提供する。

【解決手段】TDC回路1は、共通の構成を有する32個の単位セル110〜1131がリング状に接続されたリング部10等を備える。単位セル11は、第1インバータ回路111,第2インバータ回路112,スイッチSW0,スイッチSW1およびスイッチSW2を含む。第1インバータ回路111のPMOSトランジスタのゲート幅は、第2インバータ回路112のPMOSトランジスタのゲート幅のαp倍である。第2インバータ回路111のNMOSトランジスタのゲート幅は、第1インバータ回路112のNMOSトランジスタのゲート幅のαn倍である。αpおよびαnの双方が1より大きいか又は双方が1より小さい。

(もっと読む)

スケルチ回路

【課題】消費電流を低減しつつ、回路面積の縮小を図ることが可能なスケルチ回路を提供する。

【解決手段】差動入力される差動入力信号と閾値とを比較して、スケルチ信号を出力するスケルチ回路は、差動入力信号が入力され、前記差動入力信号と前記閾値とを比較して得られた第1のデジタル信号を出力する第1のコンパレータ回路を有する。また、デジタル回路で構成され、前記第1のコンパレータ回路の出力を平滑化し前記スケルチ信号として出力するデジタル平滑化回路を有する。また、第1のコンパレータ回路は、第1のクロック信号により動作が制御され、前記差動入力信号と前記閾値とを比較して得られた第1の差動比較信号を出力する第1のクロックト・コンパレータと第1の差動比較信号が入力され、前記第1の差動比較信号の論理を保持して前記第1のデジタル信号として出力する第1のデータ保持回路を有する。

(もっと読む)

位相同期ループ回路

【課題】必要な特性を満たしつつ、回路構成を簡素化し、省面積化を可能とするデジタルPLLの提供。

【解決手段】リファレンスクロック信号FRと分周クロック信号FDの位相差を検出するTDC101、FDとFRの進み遅れを出力するFF103、位相誤差演算器102、位相誤差(PERR)を平滑化するデジタルフィルタ104、出力クロック信号FOを出力するDCO105、FOを分周したFDを出力するN分周器106、N分周器106内のカウンタ値をFRに応答してサンプルするレジスタ107を備え、TDC101は、位相差検出測定範囲がFOの1周期以内とされ、FRとFDの位相差をFOの1周期に換算した小数で出力し、位相誤差演算器102は、FDとFRの位相差が、FOの周期の整数倍以上のときは、レジスタ107出力と符号情報signから、FOの1周期内のときは、TDCの出力と符号情報signからPERRを演算出力する。

(もっと読む)

デジタル位相同期ループ回路

【課題】TDC(Time−to−DigitalConverter)の回路規模を拡張することなく、デスキュー用途に用いることが可能であるADPLLの構成の提供。

【解決手段】DCO19と、FREFを分周するMDIV11と、DCOの出力FOを分周するPDIV20と、PDIVの出力FOUTを分周するNDIV12と、MDIVの出力信号FRとDCOの出力FOの位相差を測定するTDC13と、NDIVの出力FDとFOの位相差を測定するTDC14と、FRでFOをサンプルするFF15と、FRとFDのうち位相が先行するパルスと次のパルスのエッジの期間、FOをカウントするCONT17と、TDC13、14、FF15の出力を入力し、カウンタの出力を受け、FRとFDの位相差を演算するPERR16と、PERRの出力を入力し、フィルタ処理した信号をDCOに供給するDFIL18を備える。

(もっと読む)

クロックデータリカバリ回路

【課題】簡易な構成で、データおよびクロック間のタイミングスキューの制約をなくすとともに、データの周波数可変範囲を広くとることができるCDR回路を提供する。

【解決手段】CDR回路は、基準クロック信号を用いてクロック信号を所望の周波数にロックするLTモードと、クロック信号をデータ信号に位相同期させる通常動作モードとを有する。CDR回路は、VCOと、入力信号を平滑化して制御電圧を生成してVCOに出力するLPFと、LTモード時に、基準クロック信号とクロック信号との周波数比較を行ない、該比較結果に応じた信号をLPFに出力する周波数ループと、通常動作モード時に、データ信号とクロック信号との位相比較を行ない、該比較結果に応じた信号をLPFに出力する位相ループと、基準クロック信号の周波数カウント値に応じてVCOに設定する周波数レンジを調整する周波数検出回路とを備える。

(もっと読む)

送信装置、受信装置および送受信システム

【課題】回路規模の増大を抑制しつつEMIノイズの低減を図ることができる送信装置を提供する。

【解決手段】送信装置10Aは、送信データ生成部11および出力バッファ部12Aを備える。送信データ生成部11は、受信装置へ送出すべきデータdata1およびクロックclock1を生成し、これらを出力バッファ部12Aへ出力する。出力バッファ部12Aは、データ送信部13およびクロック送信部14Aを含む。クロック送信部14Aは、間欠的に位相シフトを与えられたクロックを生成して送出する。データ送信部13は、クロック送信部14Aにより送出されるクロックに同期してデータを送出する。

(もっと読む)

PWM電力変換装置のデッドタイム補償装置

【課題】デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減することで遅延誤差TDLYを短縮する。

【解決手段】デッドタイム補償部30は、PWMゲート指令Gate_UとPWM出力Vce_Uとの位相差に応じて求めるデッドタイム補償分Vcmp_UでPWM電圧指令Vcmd_Uの電圧値を増減し、この補償後のPWM電圧指令Vcmd_U’をPWM波形発生部20でPWMゲート指令に変換することで、デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減する。

(もっと読む)

発振回路動作状態検出回路

【課題】発振回路の動作状態を短時間で検出する。

【解決手段】VDDの電源端子とVSSの電源端子の間にノードN1を共通接続点とするトランジスタMP1,MN1を直列接続し、ノードN2を共通接続点とするトランジスタMP2,MN2を直列接続する。ノードN1,N2の間に容量C1を接続する。ノードN1,N2にNOR1の入力側を接続する。トランジスタMP1,MN1に直列に電流源I1を接続し、トランジスタMP2,MN2に直列に電流I2を接続する。トランジスタMN1,MN2のOFF抵抗をトランジスタMP1,MP2のOFF抵抗より小さくする。発振回路の発振クロック信号が第1の論理のとき、トランジスタMP1,MN2をONさせると共にトランジスタMP2,MN1をOFFさせ、第2の論理のとき逆にする。

(もっと読む)

TDC回路

【課題】検出可能範囲の拡大と分解能の向上とを両立可能なTDC回路を提供する。

【解決手段】2n個の遅延量の異なる反転遅延素子を直列接続して形成されたループをそれぞれ含む第1の遅延回路および第2の遅延回路に、第1パルス信号駆動回路および第2のパルス信号駆動回路により、第1の遅延回路および第2の遅延回路にそれぞれ検出対象エッジとリセットエッジを有するパルス信号伝搬させる構成を持つバーニアディレイに、第1の遅延回路の反転遅延素子のいずれかと第2の遅延回路の反転遅延素子のいずれかに対して、伝搬されるリセットエッジの入力に対応する論理反転を選択的に遮断する操作をそれぞれ行う遮断回路と、第1の遅延回路および第2の遅延回路に含まれる遮断対象の反転遅延素子に対して、伝搬された検出対象エッジの入力に応じて反転した論理をリセットする操作をそれぞれ行うリセット回路とを備える。

(もっと読む)

クロック発生回路

【課題】ロックアップタイムを短くすることのできるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、基準クロックRCLKに基づいて、周波数を変調させた変調クロックSCLKを発生するスペクトラム拡散クロック発生回路10と、基準クロックRCLKと変調クロックSCLKとの位相の一致を検出したときにHレベルのロック信号LOCKを出力する位相比較器20とを含む。また、クロック発生回路1は、Hレベルのロック信号LOCKが出力されるまでは基準クロックRCLKを出力クロックCLKとして選択し、Hレベルのロック信号の出力に応答して変調クロックSCLKを選択するセレクタ50を含む。

(もっと読む)

PLL周波数シンセサイザ

【課題】改善された位相雑音特性を有するPLL周波数シンセサイザを提供する。

【解決手段】VCO20は、制御電圧VCNTに応じた周波数fVCOで発振する。周波数ミキサ22は、VCO20の出力信号SVCOとローカル周波数fLOを有するローカル信号SLOを周波数ミキシングする。第1フィルタ26は、ミキサ22によるミキシングにより得られる差周波信号SDIFFを抽出する。位相誤差検出部12は、第1フィルタ26により抽出された差周波信号SDIFFと基準周波数fREFを有する基準信号SREFの位相を比較し、位相差に応じた位相誤差信号VPEを生成する。ループフィルタ18は、位相誤差信号VPEをフィルタリングし、制御電圧VCNTを生成する。第2フィルタ28は、ミキサ22によるミキシングにより得られる和周波信号SSUMを抽出し、出力端子OUTから和周波信号SSUMを出力する。

(もっと読む)

41 - 60 / 298

[ Back to top ]