Fターム[5J039KK26]の内容

Fターム[5J039KK26]に分類される特許

41 - 60 / 65

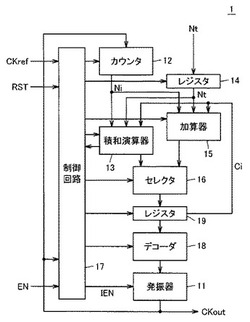

クロック発生回路

【課題】クロック逓倍してクロック信号を発生するクロック発生回路のロックインタイムを短縮する。

【解決手段】ロックイン状態において、2つの数値データCi,C(i+1)を積和演算器が出力し、各数値データに従って発振器11の発振周期を設定して、その出力クロック信号のパルス数をカウントして第1および第2のカウント値を生成する。これらの2つの数値データと2つのカウント値と周期目標データとに従って、発振器の発振周期を設定する第3の数値データを生成して、発振器の発振周期を設定する。

(もっと読む)

半導体集積回路

【課題】外部からクロック信号と非同期にリセット信号等の入力信号が入力される半導体集積回路において、入力信号に混入したノイズを高精度に除去する。

【解決手段】この半導体集積回路は、入力回路から出力される外部入力信号が活性化されたときにシステムクロック信号の生成を開始するシステムクロック信号生成回路と、システムクロック信号に同期して、外部入力信号を初段のフリップフロップにおいてサンプリングし、サンプリングによって得られた信号を順に伝播する従属接続された複数のフリップフロップ、及び、入力回路から出力される外部入力信号と終段のフリップフロップの出力信号とが活性化されているときに、内部回路に供給する内部入力信号を活性化する論理回路を含むサンプリング回路と、内部入力信号に基づいて、外部入力信号がノイズにより活性化されたのか否かを判定する制御回路とを具備する。

(もっと読む)

集積回路装置及び電子機器

【課題】静電気放電等を原因とする誤動作を防止できる集積回路装置等の提供。

【解決手段】集積回路装置はロジック回路ブロックと電源回路ブロックを含む。電源回路ブロックは、複数のレジスタを有し、ロジック回路ブロックからのアドレス信号のレジスタアドレスで指定されるレジスタに対して、ロジック回路ブロックからのデータ信号で設定される電圧調整データが書き込まれるレジスタ部を含む。ロジック回路ブロックは、有効なデータ信号が出力されるデータ有効期間TA以外の期間TBにおいて、第1のビットパターンのアドレス信号(Fh)を出力する。レジスタ部のレジスタマップでは、第1のビットパターンのアドレス信号(Fh)に対応するレジスタアドレス以外のレジスタアドレスに対して、電圧調整データが書き込まれるレジスタがマッピングされている。

(もっと読む)

クロック分周器

【課題】大規模かつ多数のクロック領域を持ったシステムLSIにおいては、ユーザが各クロック領域のクロック周波数(分周比)の設定を間違ったとしても、デッドロックすることなく動作し続けることができるような、クロック分周器を提供することを課題とする。

【解決手段】他のクロック分周器の分周比を参照し、自己のクロック分周器の分周比を決定する分周比決定手段(503)と、前記決定された分周比で入力クロックを分周して分周クロックを生成する分周クロック生成手段(519)とを有することを特徴とするクロック分周器が提供される。

(もっと読む)

多相クロックを生成するためのシステム及び方法

【課題】多相クロックを生成する。

【解決手段】多相クロックを生成するためのシステムと方法が開示される。一実施形態において、多段電圧制御発振器(「VCO」)(302)が、所望の数のクロック位相出力を生成するクロック分周器(304)に複数のクロック位相(ck0−ck5)を伝達する。この実施形態のクロック分周器(304)は、ステートマシンを含み、それは、例えば複数の逓減されたクロック位相を提供する改良型ジョンソンカウンタ(316)であり、それらのクロックの各々は独立した改良型シフトレジスタ(306-314)に接続される。各改良型シフトレジスタは、D型フリップフロップを含み、各D型フリップフロップは別個のクロック位相出力を提供する。一実施形態において、多相クロックのクロック位相出力の数は、VCOのクロック位相の数に改良型ジョンソンカウンタの所望状態の数を掛け合わせる関数である。

(もっと読む)

半導体装置、表示装置、及び電子機器

【課題】ノイズによって誤動作することが少なく安定に動作し、消費電力が少なく、特性変動の少ない半導体装置、および前記半導体装置を有する表示装置、ならびに前記表示装置を有する電子機器を提供する。

【解決手段】出力端子を電源線に接続し、出力端子の電位変動を抑える。さらに、トランジスタの容量により、該トランジスタがオン状態となるゲート電極電位を維持する。また、逆バイアス用信号線により、トランジスタの特性変動を抑える。

(もっと読む)

エラスティックストア回路

【課題】入力、出力データを止めることなく入出力タイミングの位相差を補正するエラスティックストア回路を提供する。

【解決手段】位相安定監視部19は、タイミングS3とタイミングS6の位相差とその安定度を監視し、入出力クロックが安定状態であり、かつ位相差がn/2±2以上である場合に、前方にa段または後方にb段の補正通知信号を出力する。位相補正部18は補正通知信号を受けると、補正すべき段数により、入力データ保持部12に出力するデータを入力データ保持部12がデータを保持する周期タイミングに合わせて切り替える。カウンタ15は補正通知信号を受けると、その周期のみ前方補正の場合は「n-a」クロック周期、後方補正の場合は「n+b」クロック周期で動作させる。

(もっと読む)

メモリ回路

【課題】電源投入時または回路動作中に電源ラインやグランドラインに伝播するノイズによって、記憶回路が誤動作してしまっていた。この記憶回路をメモリ装置の書き込みと消去との制御信号のラッチ回路として使用した場合、メモリ装置の内容が意図せずに書き換えられてしまうことがあった。

【解決手段】本発明のメモリ回路を構成する記憶回路は、第1のラッチ回路5とこれの反転データを入力する第2のラッチ回路6と、第1のラッチ回路5と第2のラッチ回路6の反転出力信号とを入力するアンド回路13とを有している。通常時は、第1,第2のラッチ回路同士は、保持するデータが互いに反転しているため、アンド回路13の出力に変化はないが、ノイズなどにより第1,第2のラッチ回路が保持するデータが互いに同じになると、アンド回路13からはデータが出力されない。したがって、メモリ回路の電源投入時、動作時を問わず誤動作を防止することができる。

(もっと読む)

スリープクロック周波数を推定するための装置および方法

温度補償水晶発振器などの高速クロックを使用してスリープまたは低速クロックの周波数を推定するための装置および方法。開示されている装置は、高速クロックに同期する、スリープクロック周期のそれぞれのサイクルを発行するスリープクロック同期パルスを受け取る第1のカウンタを有する推定器を備える。低速クロック同期パルスは、所定の個数までカウントされ、その後、フルカウント信号が発行される。第2のカウンタは、フルカウント信号を受け取り、フルカウント信号を受け取る毎にインクリメントする。第3のカウンタは、フルカウント信号が現れるまで高速クロックサイクルをカウントする。低速および高速クロックサイクルのカウント数に基づき、測定を実行するため高速クロックの領域のみを使用して低速クロックの周波数を決定し、これにより、測定の精度を高速クロックの精度に結び付けることができる。開示されている装置は、さらに、集積回路および開示されている推定器を使用するトランシーバを備える。それに対応する方法も開示される。  (もっと読む)

(もっと読む)

ダイレクトチャージ型スイッチト・キャパシタ回路を含む電気回路

【課題】スイッチト・キャパシタ回路における寄生容量の影響を抑制する。

【解決手段】 キャパシタCの第1の端子に入力信号を供給し、第2の端子を基準電位に維持させることによってキャパシタCに入力信号の強度に応じた電荷を蓄積させる第1のモードと、キャパシタCの第1の端子をオペアンプ50bの出力端子TbOUTに接続し、第2の端子をオペアンプ50bの反転入力端子Tb(−)に接続する第2のモードとを選択可能とするスイッチング素子Toa,Tia,Tob,Tibとを含むメモリ単位52を少なくとも1つ備え、メモリ単位52に含まれるキャパシタCは、半導体基板の表面のウェル、ウェル上に形成された絶縁膜及び電極層とによって構成され、電極層をキャパシタの第1の端子とし、ウェルをキャパシタの第2の端子とすることによって上記課題を解決することができる。

(もっと読む)

集積化シリアルデータデコーダ

【課題】集積化シリアルデータデコーダを提供する。

【解決手段】本発明は、コンデンサを含まないシリアルデータデコーダを提供し、シリアルデータデコーダを集積回路に設計し、いかなる外部装置も必要としない。本発明の集積化可能なシリアルデータデコーダは、クロック生成器と、周期検出器と、チャネルデコーダと、からなり、コンデンサは含まない。復調されたシリアルデータを入力し、シリアルデータを、周期的に、繰り返し、並列データに転換する。

(もっと読む)

ノイズフィルタ及びフィルタリング方法

【課題】 本発明は、ノイズ除去時間をハードウエアにより決定し、プロセッサが使用される環境に最適なノイズ除去時間を決定することが出来るノイズフィルタ及びフィルタリング方法を提供することを課題とする。

【解決手段】 選択回路18はフィルタの段数が1段の信号Xをフィルタ出力信号OUTとして選択出力している。波形チェック部18は、フィルタ出力信号OUT上のパルス幅が、最小パルス幅指定レジスタ20の設定値より小さいとき、選択回路19にフィルタの段数が2段の信号Y、3段の信号Zを選択出力させる。段数の最適化処理が終了するとフィルタ値最適化完了フラグ(STATUS BIT)21をセットする。

(もっと読む)

半導体集積回路

【課題】逓倍率等の設定用のピンを用意する必要がなく,かつ,逓倍率等の変更時に外部リセット信号を供給する必要がない半導体集積回路を、提供する。

【解決手段】半導体集積回路10を、各種の内部回路に供給する内部クロックを外部クロックから生成するための、生成する内部クロックの種類を指定可能であると共に,生成する内部クロックの種類を指定し直すときにリセットが必要なクロックジェネレータ11と、生成する内部クロックの種類をクロックジェネレータ11に対して指定する処理とクロックジェネレータ11をリセットする処理とを,CPUからのコマンドに基づき実行可能なリセット信号生成回路12及び設定用回路13とを備える回路としておく。

(もっと読む)

周波数逓倍装置

【課題】出力信号の精度を維持することが可能な高精度の周波数逓倍装置を低コストに提供する。

【解決手段】基準信号PREFの1周期分の時間内に生成された出力クロックRCKをカウント(計時)し、そのカウント値を表すデジタルデータDL1〜DL12をラッチ(確定)し、そのデジタルデータをクリアする、という動作を基準信号PREFの2周期毎に繰り返す結果、基準信号PREFの2周期毎にラッチされたデジタルデータDL1〜DL12である周波数制御データCD1〜CD12が新たに生成される。この新たに生成される周波数制御データ[2]は、基準信号PREFの2周期前に生成された周波数制御データ[1]を補正したものといえる。そのため、出力クロックRCKのカウント値が周波数制御データに反映され、新たな周波数制御データ[2]が生成されるまでに要する時間である補正遅延時間tは基準信号PREFの2周期分の時間になる。

(もっと読む)

信号発生装置および方法

【課題】基準クロック信号に従ってデジタル値のシーケンスを生成することのできる信号発生器を提供する。

【解決手段】本発明の一実施形態によれば、基準クロック信号に従ってデジタル値のシーケンスを生成する信号発生器3が提供される。この信号発生器3は、インクリメント信号INC及びオフセット信号Φ1、Φ2を受け取る少なくとも1つの入力端子32、33、34と、オフセット信号Φとインクリメント信号INCに基づいてカウンタ開始値を決定するようになっている開始値回路302と、開始値に設定されるようになっており、基準クロック信号の各サイクルにおいて、規定の値が達成されるまで、カウンタの位置をインクリメント信号INCに従って新しい値に変更するようになっているカウンタと、カウンタ値を出力する出力端子とを備える。

(もっと読む)

アナログデジタルコンバータ

【課題】V−F変換を利用したADコンバータであって、変換周波数を高めることなく、高精度にAD変換を行うことが可能なものを実現する。

【解決手段】二本のVCOを設け、両VCOの周期差を利用して主VCOの周期未満のV−F変換値を求める。BASE−VCO1から出力されるパルス信号のパルス数をカウンタ4にて計数することにより、デジタル信号の上位ビットを生成する。一方、下位ビットについては、第3レジスタ10並びに第2および第3減算器11,12により、サンプリング周期ごとに、現在のサンプリング信号Psの活性化時点からBASE−VCO1およびJAW−VCO2の出力の位相一致時点までの間に含まれる、BASE−VCO1の出力のパルス数に基づいて、サンプリング周期内初頭からBASE−VCO1の出力のサンプリング周期内最初のパルス発生までの位相差を算出することにより生成する。

(もっと読む)

パルス幅変調回路及び多相クロック生成回路

【課題】

周波数の微調整を行うことが可能なパルス幅変調回路及び多相クロック生成回路を提供すること。

【解決手段】

本発明にかかるパルス幅変調回路は、基準クロックに基づいて多相クロック信号を生成する多相クロック生成手段と、入力データと、多相クロック信号とに基づいてパルス幅変調信号を生成するパルス幅変調信号生成手段とを備えたパルス幅変調回路であって、多相クロック生成手段は、位相ロックループ回路を有し、多相クロック信号のうち任意のクロック信号を選択し、帰還クロックとして前記位相ロックループ回路に出力するパルス幅変調回路である。このような構成によれば、多相クロック生成回路の生成する多相クロックのクロック周波数が変更可能となり、クロック周波数及びパルス周波数の微調整を行うことが可能となる。

(もっと読む)

逓倍クロック信号出力回路

【課題】 電源を分離するようなコストアップする対策を採らずとも、逓倍クロック信号の周波数を安定化させることができる逓倍クロック信号出力回路を提供する。

【解決手段】 逓倍クロック信号出力回路1にカウンタ・数値平均化回路3を備え、基準クロック信号PREFの周期をカウントするカウンタによる複数回のカウント結果を制御周期内で平均化し、デジタル制御発振回路2は、その平均化されたデータDTAVEを演算処理して逓倍クロック信号POUTを生成する。

(もっと読む)

ドライバ回路、シフトレジスタ及び液晶駆動回路

【課題】 表示部のトランジスタの動作速度を増加させ、かつこのトランジスタを駆動するa−Si TFT用の動作寿命が従来に比較して長いドライバ回路,シフトレジスタ、またこのシフトレジスタを用いた液晶駆動回路を提供する。

【解決手段】 本発明のドライバ回路は、しきい値電圧を制御するバックゲートが設けられており、ゲートに印加された電圧に対応して、ドレインから入力される電圧をソースから出力信号として出力するトランジスタが設けられている。

(もっと読む)

高速データ・サンプリング・システム

【課題】相対的に低速の回路を利用して相対的に高レートでアナログまたはディジタル・データ信号をサンプリングするシステムを提供する。

【解決手段】システム40はデータ信号を受信する複数のサンプル・アンド・ホールド回路42〜50を含んでいる。これらサンプル・アンド・ホールド回路は同一周波数であるが、相互に対して等位相でずれている、それぞれのクロック信号Φ1 …Φn によってクロックがとられている。サンプル・アンド・ホールド回路の各々は一連のシフト・レジスタ62〜70に接続されている。これらのシフト・レジスタは、それぞれのサンプル・アンド・ホールド回路によってとられたサンプルS1 …Sn を順次に格納するように動作する。シフト・レジスタの出力82〜90を、マトリックス・ディスプレイの列ドライバに印加する。

(もっと読む)

41 - 60 / 65

[ Back to top ]