Fターム[5J039KK27]の内容

Fターム[5J039KK27]に分類される特許

181 - 200 / 200

分周回路およびデジタルPLL回路

【課題】出力信号に生じるジッタ量を抑えることができる分周回路を提供する。

【解決手段】直列に接続されたD−FF7,9,11を、入力信号S0を基準クロック信号として駆動し、分周比決定信号S21によって選択された分周比で入力信号S0を分周して第1の分周信号S7を生成する回路モジュール3と、直列に接続されたD−FF47,49,51,53を、第1の分周信号S7を基準クロック信号として駆動し、当該直列に接続されたD−FFの段数に応じた分周比である8分周で、第1の分周信号S7を分周して出力信号S57を生成する回路モジュール45と、回路モジュール45のD−FFの出力および4/5選択信号S24に基づいて、分周比決定信号S21を生成するOR回路55とを有する。

(もっと読む)

スペクトラム拡散クロック生成回路

【課題】設計が容易、かつ変調プロファイルの変更も簡単であり、しかもプロセス、温度、電源電圧の変動に関わらず、常に一定の周波数変調を効率的に行うことができるスペクトラム拡散クロック生成回路を提供する。

【解決手段】スペクトラム拡散クロック生成回路は、電圧制御発振器から、基準クロックに位相同期され、その位相が各々90°ずつずれた4相のクロックを出力するPLLと、基準クロックに同期して動作し、4相のクロックの各々に対応して一定のパターンで周期的に繰り返し変化し、4相のクロックのうちの隣接する2相のクロックの間の重み付けを行うための制御信号を出力する位相補間制御回路と、隣接する2相のクロック毎に、制御信号に応じて隣接する2相のクロックの各々に重み付けをして合成し、両者の間を所定の段階に位相補間することを全ての隣接する2相のクロックについて行い、位相補間して得られたクロックをスペクトラム拡散クロックとして出力する位相補間器とを備える。

(もっと読む)

デュアルループPLLおよび逓倍クロック発生装置

【課題】 初期起動においてロックアップ時間を短縮できるデュアルループPLL(Phase Looked Loop)を提供すること、および消費電力低減に寄与する逓倍クロック発生装置を提供すること。

【解決手段】 デュアルループPLLは、位相を比較する位相比較器1を有する位相比較ループと、周波数を比較する周波数比較器7を有する周波数比較ループとを有するデュアルループPLLを備え、周波数比較器7は、位相比較器1に用いる、外部基準クロックラインCLex11から入力される基準クロック信号と異なる、キャリブレーションクロックラインCLcal18から入力される入力信号を用いて周波数比較を行う。また、上記デュアルループPLLを用いて、逓倍クロック発生装置を構成する。

(もっと読む)

半導体集積回路装置

【課題】 高信頼性のデッドロック解除機能を持つPLL回路を備えた半導体集積回路装置を提供する。

【解決手段】 PLL回路のデッドロック解除回路として、制御電圧モニタ回路によりPLL回路の位相比較出力に対応したVCO制御電圧が規定値を超えることを検出し、位相モニタ回路により基準信号と帰還信号の位相が入力半サイクル以上外れていることを検出し、判定回路により上記制御電圧モニタ回路と位相モニタ回路の両検出信号が成立した場合にのみデッドロック状態と判定して、上記VCO制御電圧を強制的に下げてデッドロック状態の解除を行う。

(もっと読む)

クロック発生回路、信号多重化回路及び光送信器、並びに、クロック発生方法

【課題】 トグルフリップフロップ回路(TFF)を用いて分周クロック信号を発生させる場合に、初期状態が定まらないというTFFの本質的な問題に起因して、発生する各分周クロック信号間に位相ずれが生じてしまうのを回避しながら、4チャンネルよりも多くのチャンネル数のデータ信号の多重化を実現できるようにする。

【解決手段】 クロック発生回路であって、位相の異なる一対の分周クロック信号を出力しうる複数のトグルフリップフロップ回路TFF1,TFF2を直列に接続し、トグルフリップフロップ回路TFF2から出力される一対の分周クロック信号の一方又は両方をディレイさせて一対の分周クロック信号とは異なる位相のクロック信号として出力しうるディレイ回路DFF1を、トグルフリップフロップ回路TFF2に接続して構成される。

(もっと読む)

遅延同期ループ及びこれを具備した半導体メモリー装置

【課題】 互いに異なる位相を有した複数個のクロック信号を発生することができる遅延同期ループを提供する。

【解決手段】 クロック信号とフィードバッククロック信号との位相差を検出し、前記位相差によって変化する複数ビットの遅延制御信号を発生する位相検出器12と、前記複数ビットの遅延制御信号に応答して前記クロック信号を遅延させて複数個の出力クロック信号及び前記フィードバッククロック信号を発生する所定個数の縦続接続された第1の遅延セルを具備する第1の遅延器18と、前記複数個の遅延制御信号に応答して反転クロック信号を遅延させて複数個の反転出力クロック信号を発生する所定個数の縦続接続された第2の遅延セルを具備する第2の遅延器22と、前記複数個の出力クロック信号及び前記複数個の反転出力クロック信号の中で関連があるクロック信号を位相混合して補正された複数個の出力クロック信号を発生する位相混合器24とを含む。

(もっと読む)

クロック信号出力回路

【課題】 電源電圧が変動する場合でも、逓倍クロック信号の出力精度を極力維持することができるクロック信号出力回路を提供する。

【解決手段】 周期カウンタ4では、基準クロック信号fsの周期をリングオシレータ1より出力される高速クロック信号frでカウントし、周期カウンタ24ではN分周された基準クロック信号fsの周期をN分周した高速クロック信号frでカウントする。そして、有効判定回路25は、周波数逓倍動作を開始した直後はマルチプレクサ26により周期カウンタ4側の周期データD1を選択して逓倍クロック信号fmを迅速に出力し、それ以降、周期カウンタ24によってカウントされた周期データD1’が有効になる時間が経過すると、当該周期データD1’を選択するようにマルチプレクサ26を切替えて周波数逓倍演算処理の対象とする。

(もっと読む)

集積回路

【課題】 内部回路が逓倍クロック信号に基づいて動作することによる電源変動の影響が、クロック信号出力回路に及ぶことを極力回避できる集積回路を提供する。

【解決手段】 電源配線14がデジタル回路群17を経由してクロック信号出力回路11に電源供給を行う経路中にローパスフィルタ22を配置し、電源配線14を伝搬しようとするノイズ成分をアナロググランド側に逃がして除去する。そして、クロック信号出力回路11による逓倍クロック信号fmの発振精度を向上させ、その逓倍クロック信号fmに同期して動作するデジタル回路群17における通信ブロック16の通信精度等を向上させる。

(もっと読む)

位相差検出装置

【課題】回路内部で発生するジッタ成分を小さくすることができる位相差検出装置を提供する。

【解決手段】 第1入力信号と第2入力信号との位相差を検出する位相差検出装置であって、第1入力信号を2分周した第1分周信号を、第1入力信号の全ての立ち上がりエッジが、第1分周信号の立ち上がりエッジ又は立ち下がりエッジのいずれかと対応するように生成する第1分周器と、第2入力信号を2分周した第2分周信号を、第1分周信号とエッジが対応するように生成する第2分周器と、第1分周信号における立ち上がりエッジと、第2分周信号において当該立ち上がりエッジと対応するエッジとの間の位相差を検出する第1位相検出器と、第1分周信号における立ち下がりエッジと、第2分周信号において当該立ち下がりエッジと対応するエッジとの間の位相差を検出する第2位相検出器とを備える位相差検出装置を提供する。

(もっと読む)

2つのPLLを用いた微小時間差回路及び時間測定回路

【課題】1桁以上時間分解能を向上させることができる微小時間差回路及び時間測定回路を提供する。

【解決手段】所定の基準クロック信号を受け、第1発振周波数を発生する電圧制御発振回路を具える第1位相同期ループ回路と、前記第1位相同期ループ回路と同じ基準クロック信号を受け、前記第1発振周波数と異なる第2発振周波数を発生する電圧制御発振回路を具える第2位相同期ループ回路とを具え、前記第1位相同期ループ回路と前記第2位相同期ループ回路の出力信号の遅延時間差から微小時間を得る。

(もっと読む)

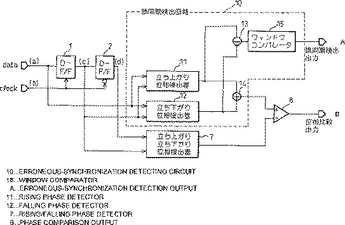

位相誤同期検出回路

位相比較回路に関し、特にデータとクロックとの位相差の比較において、データのデューティが100パーセントからずれたときに生じる位相の誤同期を検出する位相誤同期検出回路を提供する。データとクロックとの位相差を検出する位相比較器において、その位相誤同期検出回路は、データの立ち上がりとクロック位相との位相差を検出してその平均位相差を出力する第1の位相検出部と、データの立ち下がりとクロック位相との位相差を検出してその平均位相差を出力する第2の位相検出部と、前記第1の位相検出部からの平均位相差と前記第2の位相検出部からの平均位相差との差が所定の範囲を超えるときに位相誤同期と判定する位相誤同期判定部と、により構成する。  (もっと読む)

(もっと読む)

シグマデルタベースのフェーズロックループ

位相周波数検出器(PFD)と、チャージポンプと、電圧制御発振器とを含むシグマデルタベースのフェーズロックループ・デバイスが提供される。PDFは、基準信号とフィードバック信号とを受信し、基準信号とフィードバック信号との比較に基づく信号を出力する。チャージポンプは、PFDからの出力信号に基づくチャージを出力する。チャージポンプは、固定量の電流を流す第1の電流源と、可変量の電流を流す第2の電流源とを含む。電源制御発振器は、チャージポンプからの受け取ったチャージに基づくクロック信号を出力する。  (もっと読む)

(もっと読む)

可変遅延回路及び半導体集積回路装置

【課題】 高い精度で遅延時間を制御できる可変遅延回路を用いた半導体集積回路装置を提供することを目的とする。

【解決手段】入力クロック信号を遅延させる第1のDLL回路3と、第1のDLL回路よりも高い精度で遅延を制御できる第2のDLL回路10とを有し、第1及び第2のDLL回路の位相比較(31、14)を独立に動作させ、かつ第2のDLL回路の遅延量制御を第1のDLL回路の動作に従属させることで、入力クロック信号に対し所定の位相関係を有する出力クロック信号を出力するように第1及び第2のDLL回路で遅延を与える半導体集積回路装置。

(もっと読む)

分周器及びそれを備えた携帯機器

【課題】 位相誤差・振幅誤差発生の原因となる電圧−電流変換部を共通化することにより、回路構成による出力誤差発生の確率を低減し得る分周器を提供する。

【解決手段】 差動対を成すTr(トランジスタ)Q1・Q2を用いて電圧信号であるクロック信号CLK1とその相補信号であるクロック反転信号CLK2とを電流信号に変換する電圧−電流変換部11と、TrQ1から出力される電流信号i101を入力して互いに180度位相の異なる2つの第1の信号・第2の信号をそれぞれ生成するTrQ11・Q12及びTrQ5・Q6と、TrQ2から出力される電流信号i102を入力して互いに180度位相の異なる2つの第3・第4の信号をそれぞれ生成するTrQ9・Q10及びTrQ7・Q8とを備えたI−Q信号生成部12とを備える。I−Q信号生成部12の第1・第3の信号の位相差が90度であり、第2・第4の信号の位相差が90度である。

(もっと読む)

多相クロック生成回路

【課題】 基準クロックの高速性やフリップフロップの高速動作を必要とせずに、狭い位相差を有する多相クロックを生成することができる多相クロック生成回路を提供する。

【解決手段】 基準クロックを基に位相が異なる複数の出力クロックを生成する多相クロック生成回路において、位相が異なる第1及び第2の基準クロック(clka,clkb)をそれぞれ分周して出力クロックを生成する第1及び第2の分周回路(diva,divb)と、第1及び第2の分周回路の所定のノード(divbx_qx,divax_qx)間を間欠的に短絡するスイッチとを有し、当該スイッチは、定常動作状態で前記所定のノードが同じレベルに制御されるタイミングで、当該所定のノード間を短絡する。具体的には、スイッチは、第1、第2の基準クロックのいずれかまたは両方により短絡制御される。独立して動作する分周回路が、位相が異なる基準クロックを分周して、位相が異なる出力クロックを生成し、短絡スイッチにより両分周回路の動作を整合させて、分周回路が生成するそれぞれの分周クロックの位相ずれを整合させる。

(もっと読む)

変調回路、同変調回路を有する位相同期回路及び同位相同期回路を有するインタフェース装置

【課題】ジッタが低減される変調回路、又はそれを用いた、小数点以下の分周数を有する位相同期回路、或いは同位相同期回路を用いたインタフェース装置を提供すること。

【解決手段】本発明の変調回路は、レベルに応じて分離された信号modiと信号modtを出力するレベルシフト部0901と、信号modiを入力し、入力されるクロックclockによって動作して信号modoを出力する変調器0903と、信号modoと信号modtとを入力して演算を行ない、振れ幅1の信号divoを出力する演算器0905とを備える。信号divoは、例えば、任意の整数M,Nに対して、整数値N,(N+1),・・・・・・,(N+2M),(N+2M+1)を表す信号として実現される。

(もっと読む)

パルス幅補正回路

【課題】クロックおよびデータ列のどちらであっても、そのパルス幅を補正することができ、しかも、その面積効率および高速性も向上させることができるパルス幅補正回路を提供する。

【解決手段】入力信号を、その立上りのタイミングで2分周する第1の2分周器と、入力信号を、その立下りのタイミングで2分周する第2の2分周器と、第1の2分周器の出力信号および第2の2分周器の出力信号のうちの一方を所定時間遅延する遅延素子と、第1の2分周器の出力信号および第2の出力信号のうちの他方と遅延素子の出力信号とのEXORをとって、入力信号のハイレベルもしくはローレベルのパルス幅が、遅延素子の遅延時間の分だけ広くなる方向に補正された出力信号を出力する論理回路とを備える。

(もっと読む)

クロック生成回路

【課題】

所望の分数逓倍、分周クロックを出力し、面積、電力の増大を抑止するクロック生成回路の提供。

【解決手段】

複数段の遅延回路10A1〜10A4を備え、入力される信号の遅延を測定する第1の遅延回路列と、第1の遅延回路列に対し信号伝播方向が逆向きに配置され、複数段の遅延回路10B1〜10B4を備えた遅延再現用の第2の遅延回路列と、を備え、第1の遅延回路列で遅延が検出された位置の遅延回路から出力される信号に基づき、前記遅延が検出された位置に対応する、前記第2の遅延回路列の遅延回路において、遅延回路の出力端子が入力端子に帰還されて閉ループを構成しリング発振回路を構成し、リング発振回路の発振出力が、第2の遅延回路列の出力端子から取り出される。第1の遅延回路列の前段には、制御信号に基づき、入力信号に対する出力信号の位相が可変に制御する位相補間器201、202を備え、第1の遅延回路列は、位相補間器201、202の出力信号の位相差を測定する。

(もっと読む)

ワイドレンジクロック発生器

第1のクロック発生回路と、周波数分割回路と、複数のマルチプレクサとを有する、ワイドレンジ複数位相クロック発生器である。第1のクロック発生回路は、それぞれが、第1の周波数および複数の異なる位相角のうちのそれぞれ1つをそれぞれが有する複数の第1のクロック信号を生成する。周波数分割回路は、第1のクロック発生回路から、複数の第1のクロック信号を受信して、第2の周波数および複数の異なる位相角のうちのそれぞれ1つをそれぞれが有する複数の第2のクロック信号を生成する。マルチプレクサは、それぞれが、第1のクロック信号のうちのそれぞれ1つを受信するように結合された第1の入力と、第2のクロック信号のうちの、第1のクロック信号のうちの前記1つと実質的に同じ位相角を有するそれぞれ1つを受信するように結合された第2の入力とを有する。  (もっと読む)

(もっと読む)

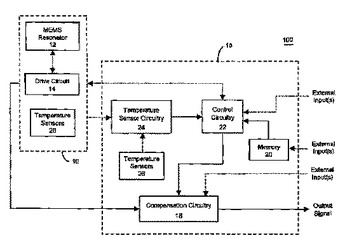

周波数および/または位相補償された微細電気機械発振器

本明細書で説明され、図示される多数の発明がある。1態様で、本発明は、出力信号を生成する微細電気機械共振器と、微細電気機械共振器の出力信号を受け取り、値のセットに応答して第2周波数を有する出力信号を生成するために微細電気機械共振器に結合された周波数調整回路構成と、を有する、補償された微細電気機械共振器を対象とする。1実施形態で、値を、微細電気機械共振器の動作温度および/または微細電気機械共振器の製造変動に依存する、微細電気機械共振器の出力信号の周波数を使用して、決定することができる。1実施形態で、周波数調整回路構成に、周波数逓倍器回路構成(たとえば、PLL、DLL、ディジタル/周波数シンセサイザ、および/またはFLLならびにこれらの任意の組合せおよびその組み合わせの変更)を含めることができる。周波数調整回路構成に、それに加えてまたはその代わりに、周波数分周器回路構成(たとえば、DLL、ディジタル/周波数シンセサイザ(たとえば、DDS)、および/またはFLL、ならびにこれらの任意の組合せおよびその組み合わせの変更)を含めることができる。  (もっと読む)

(もっと読む)

181 - 200 / 200

[ Back to top ]