Fターム[5J039KK27]の内容

Fターム[5J039KK27]に分類される特許

41 - 60 / 200

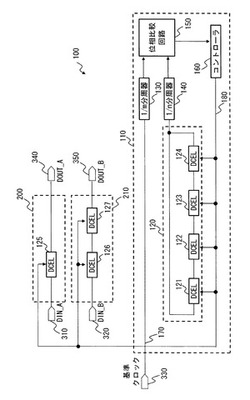

位相調整回路及び位相調整方法

【課題】消費電力を低減し、かつ回路面積も小さい位相調整回路を提供すること

【解決手段】位相調整回路100は、複数の遅延素子回路121〜124をリング状に結合したVCO120を有するPLL発振回路100を備える。また位相調整回路100は遅延素子回路を所望の遅延量に応じた数(125〜127)だけ有し、入力信号に前記所望の遅延量を与える位相遅延回路200、210を備える。PLL発振回路100は基準クロックの入力に応じた基準信号に、基準信号の所定周期分の遅延を与えた発振信号をVCO120において生成する。PLL発振回路100は、基準信号と、発振信号に応じた信号と、が略同位相となるように算出された遅延量に応じた遅延制御信号を遅延素子回路121〜124、及び遅延素子回路125〜127の各々に対して入力する。

(もっと読む)

集積回路及び位相制御方法

【課題】分周クロック信号とクロック信号との位相関係を適応的に制御可能な集積回路を提供する。

【解決手段】集積回路は、第1のクロック信号を分周して第2のクロック信号を生成する分周回路と、第1のクロック信号が伝搬する第1の信号伝搬経路と、第2のクロック信号が伝搬する第2の信号伝搬経路と、第1の信号伝搬経路を伝搬後の第1のクロック信号に第2の信号伝搬経路を伝搬後の第2のクロック信号を少なくとも2回掛け合わせることにより出力信号を生成するミキサ回路と、ミキサ回路の出力信号の直流成分を検出する直流検出回路と、直流検出回路が検出した直流成分に応じて第1の信号伝搬経路及び第2の信号伝搬経路の少なくとも一方の伝搬遅延量を制御する制御回路とを含む。

(もっと読む)

クロック発生回路及びその制御方法

【課題】従来技術のクロック発生回路は、クロックの周波数の切り替え時において、電流変動を抑制することができないという問題があった。

【解決手段】本発明にかかるクロック発生回路は、第1の周波数を有するクロック信号を第1の周波数よりも周波数が高い第2の周波数に切り替え可能なクロック発生部と、クロック信号のクロックパルスを所定の間引き率でマスクする間欠クロック生成部と、を有する。そして、間欠クロック生成部は、クロック信号の周波数が第1の周波数から第2の周波数に切り替わる場合に、第2の周波数に切り替わる時点から所定の期間、第2の周波数を有するクロック信号のクロックパルスを所定の間引き率でマスクすることを特徴とする。

(もっと読む)

回路シミュレーション装置、回路シミュレーション方法及びプログラム

【課題】位相同期回路を含む回路シミュレーションにおいて、フィードバックループに分周器が存在している場合であっても正確にシミュレートできるようにすること。

【解決手段】フィードバックループに設けられた分周器の分周比を測定するための第1のクロック信号を生成する測定クロック生成部と、分周器が第1のクロック信号を受信して分周して出力した第2のクロック信号と、第1のクロック信号とを参照して、分周器の分周比を測定する分周比測定部と、入力クロック信号を受信し、入力クロック信号の周期と予め設定された逓倍比と測定された分周比の逆数に相当する逓倍比とに応じて、入力クロック信号を逓倍して第3のクロック信号として出力する逓倍クロック生成部と、第1のクロック信号及び第3のクロック信号を受信し、いずれかを出力クロック信号として出力するクロック出力制御部とを有する。

(もっと読む)

局部発振器

【課題】デジタル制御発振器の出力と参照信号とが非同期であっても、安定したPLL動作を確立できる局部発振器を提供することを目的とする。

【解決手段】デジタル制御発振器の発振信号と前記参照信号との位相差を発振器分数位相として出力し、また、前記発振信号の位相が、前記参照信号の位相に対して、前記発振信号の半周期よりも位相が遅れている場合に「−1」、遅れていない場合に「+1」の補整情報を出力する時間デジタル変換器と、|前記補整情報−予測位相情報|>|前記補整情報+前記第1位相情報−前記予測位相情報|の場合に、前記第1位相情報に前記補整情報を加算したものを第2位相情報として出力し、|補整情報−発振器予測位相|>|補整情報+第1位相情報−発振器予測位相|でない場合に、前記第1位相情報を第2位相情報として出力する補正部と、を備えている。

(もっと読む)

局部発振器

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

多相クロック生成回路

【課題】

位相ノイズが少ない多相クロック生成回路を提供する。

【解決手段】

多相クロック生成回路は,基準クロックを生成する基準クロック生成器と,リング状に接続された複数の遅延回路を有し,前記複数の遅延回路がそれぞれ位相がずれた出力クロックを出力する多相クロック発振器と,前記複数の遅延回路のいずれかの出力端子に前記基準クロックを供給する基準クロック注入回路とを有する。多相クロック発振器のクロックの位相ノイズを低減し周波数変動が抑制できる。

(もっと読む)

半導体装置

【課題】半導体装置の回路面積の増大を抑制し、かつクロックジッタを低減できるようにする。

【解決手段】基準クロック信号を動作クロックとして動作する回路ブロックと、基準クロック信号をn分周したクロック信号を動作クロックとして動作する回路ブロックとを有する半導体装置にて、遅延回路により基準クロック信号に所定の遅延を与えて、セレクタが制御信号に応じて基準クロック信号及び遅延が与えられたクロック信号の内から1つのクロック信号を選択して基準クロック信号を動作クロックとして動作する回路ブロックに出力するようにして、電源ノイズにより生じる位相変化を合わせた基準クロック信号の位相変化量を各周期で等しくしてクロックジッタを低減できるようにする。

(もっと読む)

電子回路、電子機器、デジタル信号処理方法

【課題】多相クロックを使用してデジタル信号処理を行なう場合に、クロック信号の各位相関係を正しく保ったまま高速動作が要求される各デジタル信号処理部まで多相クロックを分配できるようにする。

【解決手段】基準タイミング生成部110は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低い基準タイミング信号J0を生成して局所タイミング再生部120に供給する。局所タイミング再生部120は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低いクロック信号であって、高速信号処理部140におけるデジタル信号処理の基準となる複数のクロック信号でなる多相タイミング信号J2を生成して高速信号処理部140に供給する。高速信号処理部140と局所タイミング再生部120を1対1で設け、1つの局所タイミング再生部120から複数の高速信号処理部140へ多相タイミング信号J2を分配しないようにする。

(もっと読む)

基準周波数発生装置

【課題】比較器が出力する追従誤差に応じて適切な制御を行い、外乱の影響によっても基準周波数信号の精度が低下しない構成の基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置は、電圧制御発振器と、位相比較器と、制御器と、ファジィ補償器と、を備える。電圧制御発振器は、基準周波数信号を出力する。位相比較器は、基準周波数信号を分周した信号と、リファレンス信号と、を比較して位相差を算出する。制御器は、位相差を考慮して制御電圧信号を電圧制御発振器に出力する。ファジィ補償器は、位相差が急激な変動をしているか否かを、ファジィ理論を用いて判定する。そして、ファジィ補償器は、位相差が急激な変動をしていると判定した場合は、当該位相差が基準周波数信号に影響を及ぼさないように補償値を決定する。

(もっと読む)

位相周波数比較器およびシリアル伝送装置

【課題】ループ帯域幅を安定させる位相周波数比較器を簡易な回路で提供する。

【解決手段】基準クロック102とフィードバッククロック103とを入力とし、周波数シンセサイザへのアップ信号と周波数シンセサイザへのダウン信号とを出力する位相周波数比較器において、第1位相周波数比較回路106と、第2位相比較回路107と、前記基準クロック102と前記フィードバッククロック103とを入力とし、前記第1位相周波数比較回路106の入力と前記第2位相比較回路107の入力とに、所定の相対的な遅延を与える遅延回路部108とを備え、周波数比較を前記第1位相周波数比較回路106で行い、位相比較を前記第1位相周波数比較回路106とラッチを制御した前記第2位相比較回路107とで行う位相周波数比較器。

(もっと読む)

位相検出回路および方法

【課題】 相当量の電力を消費し、かつジッタを生成する分周器回路を必要とせずに、高周波周期出力信号を生成する位相ロックループを提供すること。

【解決手段】 位相検出器回路は、第1および第2周期入力信号の位相を比較して、出力信号を生成する。位相検出器は、第1および第2周期入力信号の2つの異なる組み合わせを作り、第3および第4周期信号を生成する回路を備える。この回路は、第3周期信号を、第1相対位相シフトを付与する、第1周期信号および第2周期信号の第1の組み合わせに基づかせる。この回路は、第4周期信号を、第1周期信号および第2周期信号の第2の組み合わせに基づかせて、異なる相対位相シフトを提供する。位相検出器は、また、第3周期信号の電力の大きさを第4周期信号の電力の大きさと比較して、位相比較出力信号を生成する比較回路も備える。

(もっと読む)

スプレッドスペクトルクロック発生器及びそれを含む電子装置

【課題】新しい変調率及び変調周波数を有するスプレッドスペクトルクロック信号を生成することができるスプレッドスペクトルクロック発生器を提供する。

【解決手段】スプレッドスペクトルクロック発生器は、第1スプレッドスペクトルクロック信号を受信して第1スプレッドスペクトルクロック信号の平均周波数に対応する周波数信号を出力する発振回路と、周波数信号を受信して第2スプレッドスペクトルクロック信号を発生する位相固定ループと、第1及び第2スプレッドスペクトルクロック信号を受信して、第2スプレッドスペクトルクロック信号の平均周波数が第1スプレッドスペクトルクロック信号の平均周波数と近接するように位相固定ループを制御する制御回路を含む。このようなスプレッドスペクトルクロック発生器は、スプレッドスペクトルクロック信号を受信して、希望する変調率及び変調周波数を有する新しいスプレッドスペクトルクロック信号を発生する。

(もっと読む)

送信装置および通信システム

【課題】 従来の送信装置では、クロックとデータとの間のスキューが変動した場合にも高精度の通信を実現することが困難であった。

【解決手段】 N(Nは自然数)ビットの第1のパラレルデータ信号を、基準クロックをN逓倍した第1変換クロックでパラレル/シリアル変換を行い、N×K(Kは自然数)ビットの第2のパラレルデータ信号を、基準クロックをN×K逓倍した第2変換クロックでパラレル/シリアル変換を行う。

(もっと読む)

適応デジタル位相ロックループ

【課題】従来のデジタルPLLで問題であった出力クロックの位相ノイズ及びジッタ性能の低下に対応するアプローチを提供する。

【解決手段】幾つかの実施形態で、デジタルPLLは、例えば位相エラー等の1又はそれ以上の実時間性能パラメータに応答して有効なDPLL帯域幅を変更する動的制御可能なフィルタを有して開示される。高帯域幅が必要とされないとき、それは比較的低いレベルであるよう制御されてよく、それによって、出力クロックのジッタは低下する。他方で、高帯域幅が必要とされるとき、例えば、ループでの位相エラーが高いとき、フィルタは、基準クロックを追跡するためにループの応答性を高めるよう比較的高いループ帯域幅を提供するように制御され得る。

(もっと読む)

データ送出装置、データ受信装置、及びデータ送受信システム

【課題】従来のHDMIのオーディオクロック伝送システムでは、サイクルタイムスタンプ値が変動してオーディオクロックの精度が劣化してしまう。

【解決手段】データのサンプルクロックを所定の分周比で分周してクロックを生成するクロック分周手段と、クロック分周手段で生成したクロックをカウントするカウント手段と、カウント生成手段で計測したカウント値を平均化する平均化手段と、平均化手段で取得した平均カウント値のビット数を削減するノイズシェーピング手段と、基本クロック、ノイズシェーピング手段で生成したカウント値及びクロック分周手段で使用した分周比を送出する送出手段を備える。

(もっと読む)

PLL回路

【課題】高速かつ確実に低雑音特性を得ることができるPLL回路を得ることを目的とする。

【解決手段】相互に異なる移相量PS14,PS24,PS34がそれぞれ設定されており、N分周された発振信号の位相を設定されている移相量だけ変える移相器4−1〜4−3と、移相量の差分の関係が移相器4−1〜4−3のそれぞれに設定されている移相量の差分の関係と一致する条件の下で、相互に異なる移相量PS15,PS25,PS35がそれぞれ設定されており、R分周された基準信号Refの位相を設定されている移相量だけ変える移相器5−1〜5−3とを設ける。

(もっと読む)

パラレル−シリアル変換器及びパラレルデータ出力器

【課題】パラレル−シリアル変換器において、データ信号をラッチするフリップフリップ(FF)に供給されるクロック信号の位相ずれを調整する。

【解決手段】FF1−1〜1−5によるデータ信号D0,D1を選択回路2で選択出力したデータ信号D[0+1]をFF4によりラッチ出力するパラレル−シリアル変換器において、レプリカのデータ信号repIN0,repIN1を選択回路10で選択出力したデータ信号repDをラッチしたFF11によるデータ信号repOUTに基づき位相ずれ検出回路12,13が生成する位相調整指示値信号に従い、分周回路3による分周クロック信号の位相を調整してクロック信号divCLKを発生する任意位相生成回路15を備えると共に、クロック信号ffCLKとrepCLKとを位相比較し、クロック信号repCLKを移相させる位相設定回路16,17を備える。

(もっと読む)

モータ用位相同期回路及びそれを用いたスピンドルモータ

【課題】入力信号の周波数が変化するようなモータの駆動制御において、ステップ入力などのように入力信号の位相が急激に変化した場合でも、オーバーシュートやスリップによる振動などの過渡的な振動の発生を抑制することができる多重PLL回路の構成を得る。

【解決手段】第2PLL21の第2位相比較回路24によって検出される位相差が所定範囲外である場合には、ループ加算器26を介さずに、第1PLL11を用いて第2PLL21のモータ部22を制御する一方、上記位相差が所定範囲内である場合には、上記ループ加算器26を介して上記第1PLL11と上記第2PLL21とを接続して多重PLL回路を構成するように、信号経路切換部33によって、該第1及び第2PLL11,12の信号経路を切り換える。

(もっと読む)

クロック情報及びデータ情報を含む信号を受信する受信器、並びにクロック埋め込みインターフェース方法

【課題】クロック情報及びデータ情報を含む信号を受信する受信器、並びにクロック埋め込みインターフェース方法を提供する。

【解決手段】クロック情報及びデータ情報を含む差動信号対を受信するにおいて、差動信号対の共通電圧レベルの変化を利用してクロック信号及びデータを復元できる、クロック情報及びデータ情報を含む信号を受信する受信器及びクロック埋め込みインターフェース方法である。

(もっと読む)

41 - 60 / 200

[ Back to top ]