Fターム[5J039KK27]の内容

Fターム[5J039KK27]に分類される特許

101 - 120 / 200

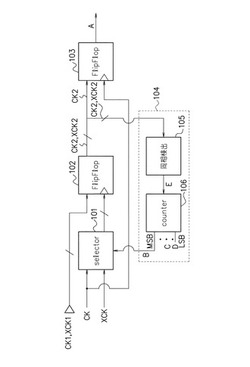

リタイミング回路及び分周システム

【課題】クロック信号の同期エッジのタイミングと入力信号のエッジのタイミングが一致したときの誤動作を防止することができるリタイミング回路及び分周システムを提供することを課題とする。

【解決手段】第1及び第2のクロック端子に差動クロック信号を入力し、第1及び第2の入力端子に第1の差動信号を入力し、第1及び第2の出力端子から第2の差動信号を出力する第1のフリップフロップ回路(102)と、前記第2の差動信号を構成する第1及び第2の信号が同相になると同相検出信号を出力する同相検出回路(105)と、前記同相検出信号のカウント値をカウントするカウンタ(106)と、前記カウンタのカウンタ値に応じて前記第1のフリップフロップ回路の前記第1及び第2のクロック端子に入力する前記差動クロック信号の位相を切り換えるセレクタ(101)とを有することを特徴とするリタイミング回路が提供される。

(もっと読む)

DDS回路及び電子装置

【課題】 チューニングワードのビット長を増加させずに、分解能を向上させ得るDDS回路及び電子装置を提供することを目的とする。

【解決手段】 リファレンスクロックの周波数に基づいて、チューニングワードから正弦波の信号を出力するDDS部11と、リファレンスクロックの周波数を分周する分周器12aと、DDS部11で出力された正弦波の信号の周波数を分周する分周器12bと、分周器12aで分周された周波数と分周器12bで分周された周波数とを合成した合成周波数を備える正弦波の信号を出力するミキサ12cと、を有することを特徴としている。

(もっと読む)

位相同期ループ回路の制御方法及び位相同期ループ回路

【課題】ロックアップ時間を短縮すること。

【解決手段】PLL回路20の位相比較器23は、基準信号frと比較信号fpの位相を比較し、両信号fr,fpの位相差に応じた信号を出力する。ループフィルタ25は強誘電体容量C1を含み、位相比較器23の出力信号に応じたチャージポンプ24から出力される位相差電流IPにより直流電圧を生成するとともに、その直流電圧を平滑化して制御電圧VCを生成する。VCO26は、制御電圧VCに応じた周波数の出力信号foを生成する。カウンタ31は、入力信号fiをカウントし、カウント値と第1の設定値,第2の設定値とを比較し、第1の期間、強誘電体容量C1を高電位電源VDDの電源線に接続し、第2の期間、強誘電体容量C1と低電位電源VSSの電源線を接続する。

(もっと読む)

カウンタ回路、レイテンシカウンタ及びこれを備える半導体記憶装置、並びに、データ処理システム

【課題】ハザードなどが発生しやすい高周波信号を正しくカウントすることが可能なカウンタ回路を提供する。

【解決手段】クロック信号LCLKに基づいて、互いに位相の異なる分周クロックLCLKE,LCLKOを生成する分周回路100と、分周クロックLCLKEをカウントする第1のカウンタ210と、分周クロックLCLKOに同期して第1のカウンタ210のカウント値を取り込む第2のカウンタ220と、第1及び第2のカウンタ210,220のカウント値を排他的に選択する選択回路230とを備える。本発明によれば、第1及び第2のカウンタ210,220のカウント値の関係が常に一定に保たれることから、ハザードが生じた場合であってもカウント値がジャンプするのみであり、カウント値が不定となることがない。

(もっと読む)

PLL位相合わせ回路

【課題】PLL回路のリファレンスクロックが停止された後に再開された場合、再開後のリファレンスクロックとフィードバッククロックとの位相合わせを短時間で行い、再ロックさせることができるPLL位相合わせ回路を提供する。

【解決手段】PLL位相合わせ回路は、PLL回路と、フィードバッククロックを分周する第1の分周回路と、PLL回路の出力クロックを分周する第2の分周回路と、リファレンスクロックの動作状態を監視するクロックモニタ回路とを備える。第1の分周回路の分周数は、第2の分周回路の分周数と等しく、クロックモニタ回路が、リファレンスクロックが停止されたことを検出すると、第1の分周回路がリセットされてフィードバッククロックが停止され、リファレンスクロックが再開されたことを検出すると、第1の分周回路のリセットが解除されてフィードバッククロックが再開される。

(もっと読む)

IQ信号発生器のためのスワップ機能を実施するためのシステム及び方法

【課題】IQ信号発生器に対してスワップ機能を実施するためのシステム及び方法を提供する。

【解決手段】IQ信号発生器を実施するためのシステム及び方法は、クロック入力信号に応答してI信号を発生するマスターラッチ、及び反転クロック入力信号に応答してQ信号を発生するスレーブラッチを含む。マスターセレクタが、マスターラッチからスレーブラッチへの通信経路を形成するように構成され、スレーブセレクタが、スレーブラッチからマスターラッチへのフィードバック経路を形成するように構成される。上述のI及びQ信号は、いかなる介在電子回路もなしにそれぞれマスター及びスレーブラッチから直接出力される。

(もっと読む)

パルス発生回路及びパルス発生回路を備えた電子機器

【課題】PVTに依存せずに安定した周波数を出力する。

【解決手段】出力する第1の出力信号Vf1の周波数を第1の制御電圧VC1で制御する第1の電圧制御発振器11と、第1の出力信号Vf1及び基準信号CLKに基づき第1の出力信号Vf1の周波数を一定に維持する第1の制御電圧VC1を生成する制御電圧生成部13と、を含む位相同期回路10と、出力する第2の出力信号Vf2の周波数を第2の制御電圧VC2で制御する第2の電圧制御発振器20と、第1の制御電圧VC1に基づき第2の出力信号Vf2の周波数を一定に維持する第2の制御電圧VC2を生成する制御電圧変換部30と、を含むパルス発生回路1。

(もっと読む)

位相制御回路

【課題】 データ信号とクロック信号がどのような位相差であっても位相差に応じたパルス幅の位相差信号を出力する。

【解決手段】 データ信号および反転した信号Yを入力し、反転した信号Yをデータ信号の遷移タイミングで保持して信号Xを出力する第1の保持手段と、クロック信号および信号Xを入力し、信号Xをクロック信号の遷移タイミングで保持して信号Yを出力する第2の保持手段と、信号Xおよび信号Yを入力し、その位相差に応じたパルス幅を有する位相差信号を生成し、データ信号とクロック信号の位相差に応じたパルス幅を有する位相差信号として出力する比較手段とを備える。

(もっと読む)

クロック信号分周回路および方法

【課題】大きな回路規模を必要とすることなく、有理数分周した出力クロック信号のサイクル時間変動を抑制するとともに、分周時に出力クロック信号の位相を調整する。

【解決手段】クロック選択制御回路100により、入力クロック信号のサイクルごとに、分周比に応じた一定サイクル時間を有する基準分周クロック信号と入力クロック信号との位相関係を示す位相計算値111を計算するとともに、位相調整信号に応じてその値を増減し、この位相計算値111に基づいて、出力動作のうち、基準分周クロック信号の位相と近いクロック信号を生成するための出力動作を指示する制御信号102,103を生成する。クロック選択回路101により、制御信号102,103に基づいて、入力クロック信号のクロックパルスをそのまま非反転で出力するか、反転して出力するか、マスクして出力しないか、のいずれかの出力動作を選択して実行することにより、出力クロック信号を生成する。

(もっと読む)

発振装置

【課題】通信機などが必要とする発振装置の発振周波数範囲の広帯域化が、簡単な構成で精度よく行えるようにする。

【解決手段】8GHzから12GHzなどの第1の周波数帯域幅の可変範囲を持つ低位相雑音な発振手段と、発振手段の発振出力を分周する周波数分周器とを備える。発振手段が出力する発振信号の周波数と、周波数分周器で分周する分周比を制御して、周波数分周器の出力周波数を、発振手段の発振周波数以下の周波数で、第1の周波数帯域幅と同じかそれ以上の周波数帯域幅で可変設定される所望の周波数とする制御を行う。

(もっと読む)

半導体集積回路

【課題】低消費電力化に適したAVS技術又はDVS技術を実現した半導体集積回路を提供すること。

【解決手段】半導体集積回路は、クリティカル・パスを形成する第1のフリップ・フロップ、組み合わせ回路及び第2のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第1の遅延回路及び第3のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第2の遅延回路及び第4のフリップ・フロップと、第2のフリップ・フロップの出力と第3のフリップ・フロップの出力とを比較する第1の比較回路と、第2のフリップ・フロップの出力と第4のフリップ・フロップの出力とを比較する第2の比較回路と、これら比較回路の出力に応じて、前記組み合わせ回路に供給される電源電圧を制御する制御回路とを備える。なお、第1の遅延回路による遅延時間と第2の遅延回路による遅延時間は異なる。

(もっと読む)

位相同期装置

【課題】本発明は、短いロッキングタイムを有しながらも、安定的に動作できる位相同期装置を提供する。

【解決手段】本発明の位相同期装置は、入力クロックを所定の分周比で分周した後、順次遅延させる動作により周波数を判別し、前記判別された周波数情報を用いて発振器ゲイン設定信号を生成する発振器ゲイン設定手段と、前記入力クロックに応じて、前記発振器ゲイン設定信号に対応する周波数を有する出力クロックを発振させるPLL回路を含むことを特徴とする。

(もっと読む)

入出力端子共用クロック周波数選択発振回路

【課題】本発明は、クロックを数多く変更可能で、LSIのクロック入力用のピン数を大幅に削減でき、クロックが安定したら自動的に信号入力用のピンに変更できる入出力端子共用クロック周波数選択発振回路を提供することを目的とする。

【解決手段】選択信号が入力されることで選択信号に応じた所定の周波数のクロック信号を発生させると共に、発生させたクロック信号が安定したことを示すロック信号を出力するPLL発振回路2と、入力手段を介して入力される入力信号を保持しPLL発振回路2に選択信号として出力するフリップフロップと、入力手段とフリップフロップとの間に設けられ該入力手段からの入力信号をフリップフロップへ伝達すると共に、PLL発振回路2からのロック信号が入力されると入力手段からの信号をI/O制御回路4へ伝達するよう切換えるI/O切換え回路3とを備えたことを特徴とする。

(もっと読む)

ジッタ印加回路、パターン発生器、試験装置、および、電子デバイス

【課題】高周波数かつ大振幅のジッタを生成する。

【解決手段】ジッタを有するジッタ重畳信号を生成するジッタ印加回路であって、与えられる基準信号を、それぞれ予め設定される遅延量で順次遅延させる、縦続接続された複数の遅延回路と、それぞれの遅延回路が出力する信号のタイミングに応じて、ジッタ重畳信号のそれぞれのエッジを生成する信号生成部と、ジッタ重畳信号の各周期に印加すべきジッタに応じた遅延量をそれぞれ設定する遅延設定部とを備え、少なくとも一つの遅延回路の遅延量が、ジッタ重畳信号の平均周期の整数倍とは異なる値に設定されるジッタ印加回路を提供する。

(もっと読む)

ジッタ増幅回路、信号発生回路、半導体チップ、及び試験装置

【課題】入力信号に含まれるジッタを増幅するジッタ増幅回路150。

【解決手段】入力信号に含まれるジッタを増幅するジッタ増幅回路であって、入力信号を受け取り、入力信号の波形を歪ませることにより、入力信号の高調波成分を生じさせる歪回路と、歪回路が出力する歪信号を、ジッタを増幅すべき増幅率に応じた次数の高調波成分以外の成分を除去して通過させるフィルタとを備えるジッタ増幅回路。

(もっと読む)

同期クロック生成回路及び同期クロック生成回路を備えたアナログ/ディジタル角度変換器と角度検出装置

【課題】安価に構成することができる同期クロック生成回路を提供する。

【解決手段】角度検出器10の出力する2相の角度信号S1とS2を、第1二乗回路11と第2二乗回路12でそれぞれ二乗し、それぞれの二乗信号を加算回路14で加算し、加算回路14の出力信号の直流成分をフィルタ16で除去する。フィルタ16の出力信号と基準電位とを比較するコンパレータ18で矩形波に変換し、その矩形波の位相を移相器20で所定量遅らせる。移相器20の出力信号を、同期化分周回路22で角度検出器10に供給する励磁信号に同期して1/2分周して同期クロックSQ3を得る。

(もっと読む)

信号発生回路

【課題】広帯域の信号を発生させる場合において、消費電力を低減することが可能な信号発生回路を提供することを目的とする。

【解決手段】基準信号aを出力する基準信号源51と、基準信号aと出力信号cとの位相差に対応する電圧を出力する位相比較器53と、位相比較器53から出力される電圧に基づく発振信号bを出力する電圧制御発振器55と、発振信号bを分周して出力信号cを出力する分周回路3と、ロック検出器56と、基準信号aと出力信号cとの位相差がゼロであることを示すフラグ信号fがロック検出器56から出力されている間、分周回路3に流れる電流を所定量ずつ下げ続け、その後、ロック検出器56からフラグ信号fが出力されなくなると、分周回路3に流れる電流を少なくとも上記所定量上げて再度上記位相差をゼロにさせる制御回路2とを備えて信号発生回路1を構成する。

(もっと読む)

クロック生成回路およびその使用方法

【課題】基準信号の周波数を逓倍又は分周したクロック信号を生成するクロック生成回路において、一つの基準信号から任意周波数のクロック信号を発生可能とする。

【解決手段】クロック生成回路1は、リング状に連結したm個の遅延素子DUからなるパルス遅延回路10と、各遅延素子DUから順次出力される通過信号P1〜Pmに基づき、基準信号CKIの周期を遅延素子DUでの遅延時間を単位として表した周期データDTを生成する周期測定部20と、除数又は乗数として使用される設定値MNを格納する設定値レジスタ50と、周期データDTに、設定値MNを乗・除してクロック信号の出力周期を表す制御データCDを生成する制御部30と、制御データCDと通過信号P1〜Pmとに基づき、基準信号CKIを分周又は逓倍したクロック信号CKOを出力する出力部40とを備え、実数で表された設定値MNを用いる。

(もっと読む)

クロック発生回路

【課題】クロック発生回路において、コストの増大を回避すること。

【解決手段】ディジタル位相比較器1、ディジタルループフィルタ2、DDS3、バンドパスフィルタ4、増幅器5、OCXO6および第1分周器7は、ディジタルPLLを構成する。OCXO6から与えられるDDS3の動作周波数をfSとし、DDS3の出力設定周波数をfOとし、nを自然数とすると、DDS3からは、ディジタル/アナログ変換のイメージ成分として、[n×fS±fO]の周波数の信号が出力される。バンドパスフィルタ4は、このイメージ成分の周波数を通過帯域とする特性を有する。

(もっと読む)

クロック信号発生回路

【課題】簡単な回路構成により、低速の基準クロックから高速のクロック信号を生成することができ、高速クロック信号の周波数選択の制限を緩和することができるクロック信号発生回路を提供すること。

【解決手段】クロック信号発生回路100は、低速の基準クロック信号S1を発生する基準クロック信号発生回路110と、基本クロック信号発生回路110からの低速の基準クロック信号S1をN1逓倍し、逓倍出力S2を出力するPLL回路130と、PLL回路130の逓倍出力S2を1/N分周し、低速の基準クロック信号S1よりも高速の第2の基準クロック信号S3を出力する分周回路140と、分周回路140の第2の基準クロック信号S3をN2逓倍し、高速のクロック信号である逓倍出力S4を出力するPLL回路150とをこの順序で備える。

(もっと読む)

101 - 120 / 200

[ Back to top ]