Fターム[5J039KK27]の内容

Fターム[5J039KK27]に分類される特許

161 - 180 / 200

半導体装置

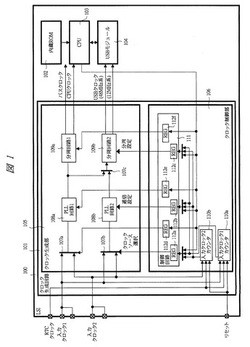

【課題】USBクロックやシステムクロック等を使用する半導体装置において、汎用性を向上することができる技術を提供する。

【解決手段】複数のクロック(入力クロック1、入力クロック2)を入力とし、その複数のクロックのそれぞれを入力クロック1カウンタ110a及び入力クロック2カウンタ110bで一定期間計測し、その計測結果を用いて複数のクロックのそれぞれの周波数を検出し、その検出結果に基づいて、クロックソース選択回路107bで複数のクロックのいずれかを選択し、PLL回路2(108b)で逓倍し、分周回路2(109b)で分周し、USBクロックを生成する。

(もっと読む)

クロック発生回路

【課題】基準クロックと分周クロックとの伝送路におけるチップ内ばらつきによるスキューを抑制し、タイミング収束性を改善したクロック発生回路を実現する。

【解決手段】クロック発生回路は、第1の回路10と、第2の回路20Aと、第3の回路50Aとを備えている。第1の回路10は、第1のクロック信号s10を生成する。第2の回路20Aは、前記第1のクロック信号s10を分周して、第2のクロック信号s20を生成する。第3の回路50Aは、前記第1及び第2のクロック信号s10,s20から、前記第2のクロック信号s20の周期を有し、かつ第1の論理レベルから第2の論理レベルへの変化のタイミングが前記第1のクロック信号s10の当該タイミングと同じである第3のクロック信号s50を生成する。

(もっと読む)

拡散スペクトラムクロック発生装置としての非線形フィードバック制御ループ

【課題】この特許開示は、クロック信号とその高調波から生成されるスプリアス放射のために、最大限可能な限りの出力密度の削減を提供するクロック信号のための、ランダム拡散を生成するために、クロック信号を拡散する回路、システムおよび方法を示す。

【解決手段】これらの新規な発明は、拡散スペクトラムクロックの生成において、支援のために非線形フィードバック制御ループ116を利用し、高価な遮蔽や他のEMI抑制方法を利用することなく、クロック信号とその高調波によって生成されるスプリアス放射のためのFCC要求に合格できる電子製品が得られる。

(もっと読む)

分周回路

【課題】グリッチの発生を抑制することのできる分周回路を提供すること。

【解決手段】分周回路2aの第1カウンタ21は基準クロック信号ICKの立ち上がりエッジに同期動作して基準クロック信号ICKを分周した第1分周信号RCKを出力する。第2カウンタ22は基準クロック信号ICKの立ち下がりエッジに同期動作して基準クロック信号ICKを分周した第2分周信号FCKを出力する。第1カウンタ21は、第2イネーブル信号生成回路24により生成された第1イネーブル信号RENに応答してカウント動作を実行・停止し、第2カウンタ22は、第1イネーブル信号生成回路23により生成された第2イネーブル信号FENに応答してカウント動作を実行・停止する。出力回路25は、第1分周信号RCKと第2分周信号FCKを合成して分周クロック信号DCKを生成する。

(もっと読む)

信号発生装置

【課題】信号発生装置の複数のチャンネルに供給されるクロックを停止することなく、チャンネル間の出力信号位相を制御する。

【解決手段】第1及び第2チャンネル20及び22は、クロック位相シフト回路26及び28と、メモリ、並直列変換回路、DACを有する信号発生ブロック10及び12を具えている。位相比較回路24は、信号発生ブロック10及び12内のメモリから波形データを読み出すための分周クロックを受けて、これらの位相を比較し、位相差信号を生成する。CPUは、この位相差信号を用いてクロック位相シフト回路26及び28を制御し、信号発生ブロック10及び12に供給するクロックの位相シフトを行うことで、第1及び第2チャンネル20及び22の出力信号の位相関係を所望の関係に制御する。

(もっと読む)

クロック発生装置

【課題】遅延回路により、1/2N(Nは正の整数)周期遅延させたN個のクロックの排他的論理和をとることでN逓倍クロックを発生する従来技術では、プロセスのバラツキにより遅延回路の遅延値が変動し、N逓倍クロックのジッタやデューティ劣化するなどの問題があった。

【解決手段】本発明では外部よりあらかじめ1/2N(Nは正の整数)周期遅延させた信号を入力することで、半導体製造プロセスのバラツキによる遅延回路の遅延変動は発生しない。したがって、排他的論理和により生成されるN逓倍クロックはジッタやデューティ劣化を低減でき、高精度なN逓倍クロックを生成できる。また、N逓倍クロックを半導体集積回路の外部に出力し、周波数のバラツキやデューティ劣化量を計算し、入力信号の入力タイミング及びデューティを調整することで高精度なN逓倍クロックを供給する。

(もっと読む)

電力/ダイエリア削減を目的とするクロックスペクトラム拡散(ディザリング)回路の完全デジタル化

【課題】クロック列をデジタル的にスペクトラム拡散する。

【解決手段】クロック列を形成するクロック、及びクロック列を変調し、ディザリングされたクロック列を生成するべく、クロック列の周波数を時間変動分周値によって分周する可変分周器を有する。本回路は更に、周波数変調波形を生成するべくディザリングされたクロック列を蓄積する第1のアキュムレータ、及び位相変調信号を生成するべく、周波数変調波形を蓄積する第2のアキュムレータを有する。本回路は更に、位相変調信号に基づいて、時間変動分周値を計算する位相値計算器、及び最初に述べたクロック列の拡散スペクトラムである第2のクロック列を生成するべく、ディザリングされたクロック列の変調をトラッキング及びフィルタリングするクローズドループ制御回路を有する。

(もっと読む)

半導体装置

【課題】本発明は、低いコストでワンチップLSIと同等のデータ転送速度を達成する半導体システムを提供することを目的とする。

【解決手段】半導体装置は、外部から受信した受信クロック信号を入力として内部クロック信号を供給する内部クロック発生回路と、チップの一辺に配置され該内部クロック信号を出力するクロック送信用端子と、該一辺に配置された複数の入出力端子と、該内部クロック信号に基づいて入出力制御用クロック信号を生成する制御用クロック発生回路と、該入出力制御用クロック信号に同期して該入出力端子を介して外部へのデータ出力及び外部からのデータ取り込みを行う複数の入出力回路と、該制御用クロック発生回路と該複数の入出力回路の各々とを接続する同一長の複数の接続配線を含むことを特徴とする。

(もっと読む)

位相同期ループ回路及び位相同期方法

【課題】 電源電圧のレベルが低くなっても高周波数の多様なクロック信号を発生することが可能な位相同期ループ及び方法を提供すること。

【解決手段】 位相同期ループ回路は外部クロック信号と帰還クロック信号を受信し、外部クロック信号の位相が帰還クロック信号の位相より先行するとアップ信号を発生し、外部クロック信号の位相が帰還クロック信号の位相より遅れるとダウン信号を発生する位相検出器と、アップ信号に応答して制御電圧が増加し、ダウン信号に応答して制御電圧を減少するループフィルタ回路と、制御電圧を受信してn(nは4以上の整数)個の内部クロック信号を直接発生する電圧制御発振器回路とを含むこともできる。また、位相同期ループ回路は少なくとも4個のループを含み制御電圧を受信して複数の内部クロック信号を発生する電圧制御発振器回路も含むことができる。

(もっと読む)

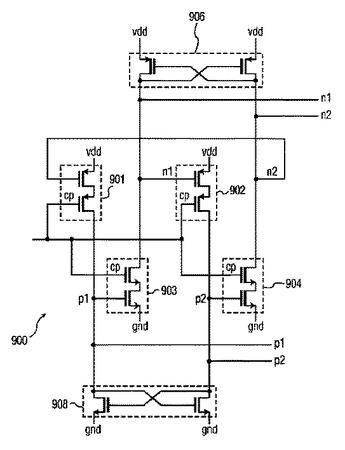

多相分周器

本発明の多相分周器はリングに接続された複数のダイナミックインバータを具え、リング全周上の中間ノードが交差結合ラッチで安定化されている。クロック入力パルスが各ダイナミックインバータの出力をイネーブルし、対応する状態変化をクロスラッチに生じさせる。多相出力がすべてのラッチに並列に与えられる。  (もっと読む)

(もっと読む)

周波数逓倍器、及びそれを用いた周波数シンセサイザ並びに通信システム

【課題】 小さな回路面積で3逓倍波を生成する周波数逓倍器を提供する。

【解決手段】 周波数逓倍器10は、方形波状の信号を出力する方形波出力回路12と、ポリフェーズフィルタ14を備えており、方形波出力回路12から出力された信号がポリフェーズフィルタ14に入力される。ポリフェーズフィルタ14の周波数領域の極は、方形波状の信号に含まれる第1次成分に対応するように設定される。これにより、ポリフェーズフィルタ14から、方形波状の信号の3倍の周波数を持つ正弦波を取り出すことができる。

(もっと読む)

クロック生成回路のテスト回路

【課題】 正確に変調周期分のサンプリングが可能で測定期間を短くすることができ、中心周波数を正確にテストすることでSSCGの変調機能の一つであるダウンスプレッドコントロールの機能テストを正確に行うことができるクロック生成回路のテスト回路を得る。

【解決手段】 コンパレータ21で変調波生成回路16からのアナログ変調波信号Smをデジタル信号Sdに変換して出力し、該デジタル信号Sdに応じて、カウンタ22でクロック生成回路2から出力されたクロック信号Soの周期のカウントを行い、該カウント値とあらかじめ規格値メモリ24に設定されたクロック信号Soの中心周波数の規格値とを比較回路25で比較するようにした。

(もっと読む)

クロック発生装置及び半導体集積回路装置

【課題】 高速動作メモリを用いる場合であっても拡散スペクトル・クロック信号を用いて、EMIを効果的に低減することができるクロック発生装置及び半導体集積回路装置を提供する。

【解決手段】 拡散スペクトル・クロック発生器210は、DDR SDRAM112Aの連続アクセスを判定し、DDR SDRAM112Aのデータ読み出し時の連続アクセスでは拡散OFFにする状態判定器220を備える。

(もっと読む)

パルス幅変調回路及び多相クロック生成回路

【課題】

周波数の微調整を行うことが可能なパルス幅変調回路及び多相クロック生成回路を提供すること。

【解決手段】

本発明にかかるパルス幅変調回路は、基準クロックに基づいて多相クロック信号を生成する多相クロック生成手段と、入力データと、多相クロック信号とに基づいてパルス幅変調信号を生成するパルス幅変調信号生成手段とを備えたパルス幅変調回路であって、多相クロック生成手段は、位相ロックループ回路を有し、多相クロック信号のうち任意のクロック信号を選択し、帰還クロックとして前記位相ロックループ回路に出力するパルス幅変調回路である。このような構成によれば、多相クロック生成回路の生成する多相クロックのクロック周波数が変更可能となり、クロック周波数及びパルス周波数の微調整を行うことが可能となる。

(もっと読む)

検出回路及び半導体装置

【課題】

簡易な回路構成により、外部クロックの停止を効率よく検出できる検出回路及び半導体装置を提供すること。

【解決手段】

本発明にかかる半導体装置は、発振クロックを逓倍したPLL出力クロックを生成するPLL回路11と、PLL出力クロックに基づいて動作する内部回路13と、発振クロックとPLL出力クロックに基づいて発振クロックの停止を検出し、検出した結果を内部回路13へ出力する発振停止検出回路12と、を有するものである。

(もっと読む)

半導体集積装置

【課題】内部の機能切替における必要なクロックの切替にかかる煩雑さを解消し、外部から内部の機能切替の命令のみで精密なクロック設定を実現する半導体集積装置を提供する。

【解決手段】外部から入力される内部機能の切替の命令100の内容を判別し、特定の機能ブロック118に対して必要なクロックの周波数を判別するクロック周波数判定回路114と、切り替え前後の周波数の関係により、機能切り替えとクロック切り替えのタイミングを制御し、切り替えの状態を表す機能切替・クロック切替完了フラグ110を外部に出力するクロック切替制御回路113とを備えることにより、クロック切り替えの制御を外部から行う必要がなくなるようにした。

(もっと読む)

集積回路

【課題】 より効果的に不要輻射を抑制できる集積回路を提供することを課題とする。

【解決手段】 各グループの電流使用規模がほぼ均一になるようにそれぞれ1以上の回路ブロックが属する複数の回路グループと、前記回路グループの数と同数の、同一周波数でタイミングの異なるクロックを生成するクロック生成部12とを集積回路に備え、クロック生成部12は、クロック生成部12が生成する各クロックの基となる基本クロックを生成するソースクロック生成部121と、ソースクロック生成部121により生成された基本クロックを1以上の段階に遅延させて、基本クロックと同一周波数でタイミングの異なるクロックを1つ以上生成する遅延回路122とを備え、各回路グループにそれぞれ異なるクロックを供給する。

(もっと読む)

入力装置とそれを構成する半導体装置

【課題】カスケード接続された複数のICのクロック信号線にアナログフィルターを挿入することなく、静電気ノイズによる誤動作を防止構成できるようにする。

【解決手段】複数の外部信号入力手段P11と外部信号入力手段P11と読み出し線との間にそれぞれ接続されたスイッチS11を有し、スイッチを導通させることにより外部信号入力手段P11より読み出し線に出力する外部入力部I11と、外部クロック信号CLK0に同期して外部制御信号を順次シフト入力したシフトデータに応じてスイッチS11からS13が導通するように出力するシフトレジスタSE1と、シフトレジスタSE1から出力された外部制御信号O1を外部へ出力する出力回路SO1とを有する半導体装置IC1において分周回路D11で、外部クロック信号CLK0を分周して内部クロック信号CLK11を生成し内部クロック信号CLK11に同期して外部制御信号を外部へ出力回路SO1を用いることでデータのズレを低減するようにした。

(もっと読む)

クロックジェネレータ

【課題】 チャージポンプ回路の出力電圧変動を抑制する。

【解決手段】 PLL回路1は、位相比較器2、チャージポンプ回路・LPF部3、VCO4、及び分周器5から構成され、チャージポンプ回路・LPF部3には、チャージポンプ回路6の充電電流及び放電電流を同一にするための補正チャージポンプ電流をチャージポンプ回路6に供給するチャージポンプ電流補正回路9が設けられている。

(もっと読む)

直交クロック分周器

n分周プロセスは、4/nスケールプロセス(110,210,310)及び後続する4分周プロセス(120,220,320)によって行われる。直交入力クロックは、クロック位相選択プロセスによって、4/nスケールプロセスを容易にする。終わりの4分周プロセスを組み込むことによって、直交出力信号は簡単に供給される。3分周直交分周器は、3つごとの直交クロック位相の選択によって4/nスケールプロセスを行い、4分周プロセスの直交出力は、この3つごとのクロック位相選択を行うために制御信号を供給する。  (もっと読む)

(もっと読む)

161 - 180 / 200

[ Back to top ]