Fターム[5J039KK27]の内容

Fターム[5J039KK27]に分類される特許

61 - 80 / 200

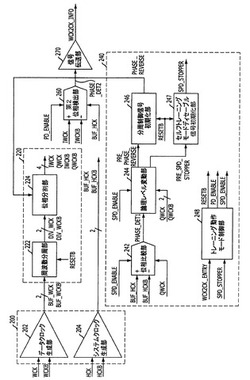

半導体装置

【課題】高速の半導体装置で要求されるクロック整列トレーニング動作を提供すること。

【解決手段】システムクロック及びデータクロックを入力されるクロック入力部(200)と、データクロックの周波数を分周して所定の位相差を有する複数の多重位相データ分周クロックを生成し、分周制御信号に応答して多重位相データ分周クロックの位相の反転可否を決定するクロック分周部(220)と、多重位相データ分周クロックのうち所定の第1選択クロックの位相を基準としてシステムクロックの位相を検出し、その結果に対応して分周制御信号のレベルを決定する第1位相検出部(240)と、多重位相データ分周クロックのうち所定の第2選択クロックの位相を基準としてシステムクロックの位相を検出し、その結果に対応してトレーニング情報信号を生成する第2位相検出部(260)と、トレーニング情報信号を外部に伝送するための信号伝送部(270)とを具備する。

(もっと読む)

分周回路

【課題】高速クロック信号に対しても正確に分周精度の分周信号を生成することのできる分周回路を提供する。

【解決手段】連続する2つの整数PおよびP+1でそれぞれ分周動作が可能な可変整数分周器(1A,1B)を並列に設け、これらの分周器を、半クロックの位相差で分周動作をさせる。経路選択信号(MXCNT)に従ってこれらの可変整数分周器の出力信号(DO1,DO2)のいずれかを選択して最終分周信号(DO)を生成する。

(もっと読む)

信号発生装置および試験装置

【課題】ループ帯域より高い周波数のジッタを印加する。

【解決手段】指定された位相の出力信号を発生する信号発生装置であって、所定周期の基準信号と出力信号との位相差に応じた制御信号を出力する位相差検出部と、制御信号の高域成分を除去するループフィルタと、ループフィルタにより高域成分が除去された制御信号に応じた周波数の周期信号を発生する発振部と、指定された位相分、周期信号に対して位相がシフトされた出力信号を出力する位相シフト部と、を備える信号発生装置を提供する。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

半導体集積回路

【課題】複数の回路ブロックを有する半導体集積回路にて、電源ノイズにより発生するクロック信号におけるジッタを低減する。

【解決手段】第1の回路ブロックに供給される第1のクロック信号のクロックパスディレイを測定する遅延測定回路と、第2の回路ブロックの動作による電源電圧の変動時間を測定する時間測定回路と、第2の回路ブロックに供給される第2のクロック信号を遅延させる遅延調整回路と、第1のクロック信号と第2のクロック信号との位相差を測定する位相差測定回路と、遅延調整回路での遅延量を制御する位相制御回路とを備え、第2の回路ブロックの動作周波数が第1の回路ブロックの動作周波数より低い場合には、位相制御回路が、ジッタが最小となる電源ノイズと第1のクロック信号との設定位相差を算出し、位相差測定回路により測定した位相差が設定位相差になるように遅延量を制御する。

(もっと読む)

高速デバイド−バイ−ツー回路

高周波数デバイダ(124)は、複数の差動ラッチ(142,143)を含む。各ラッチは、クロス連結されたPチャネルトランジスタのペア(158,159および161,162)と可変抵抗素子(163,164)を含む。ラッチは、可変抵抗素子へ供給されるマルチ・ビット・デジタル制御値(CONTROL)を設定することによって高オペレーティング周波数でより低い出力抵抗を持つように制御される。高周波数で低下された出力抵抗を持つようにラッチを制御することは、ラッチの3dB帯域幅が、広いオペレーティング周波数レンジに維持されることを可能にする。かなりの直流バイアス電流が可変抵抗素子を渡って流れないように、可変抵抗素子は、ラッチの2つの差動出力ノード(146,147または152,153)の間に配置される。結果として、よい出力信号電圧振幅が高周波数で維持され、従来の差動ラッチデバイダにおける出力信号振幅の低下および電流消費増加と比較して、デバイダ電流消費は、高周波数であまり増加しない。 (もっと読む)

周波数の即時調整が可能な節電型トリガー制御装置、および、その方法

【課題】周波数の即時調整が可能な節電型トリガー制御装置及びその方法を提供する。

【解決手段】本発明に係る装置は、少なくとも2つの信号入力端を有する信号制御ユニットと、計数制御ユニットと、クロック生成器と、からなる。2つの信号入力端はそれぞれ、トリガー回数を受信し、その後対応する回数の周波数逓増トリガー信号又は周波数逓減トリガー信号を生成する。計数制御ユニットにより受信した周波数逓増トリガー信号及び周波数逓減トリガー信号を計数する。クロック生成器により計数した周波数逓増トリガー信号又は周波数逓減トリガー信号の回数に基づき、出力周波数を線形逓増又は逓減する。本発明の装置は更に、電源コントローラーを有し、出力電圧を調整する。本発明は、システムのいかなる状態下でも、外部の制御により即時にシステムの周波数/電圧を線形調整でき、節電目的が達成される。

(もっと読む)

PLL回路および電圧制御発振器

【課題】PLL回路のデッドロック状態になることを防止する

【解決手段】閾値判定部13aは、制御電圧の高低を示す制御信号を生成する。制御部13bは、制御信号に応じた制御値を出力し、制御値が発振周波数の上限および下限について最も高い対応関係を示す場合において制御信号が高を示すとき、および制御値が発振周波数の上限および下限について最も低い対応関係を示す場合において制御信号が低を示すときのいずれか一方を満たす際、所定の制御値を出力する。発振器13cは、制御電圧と発振周波数との対応関係が発振周波数の上限および下限が異なるように複数定められていると共に対応関係が複数の制御値と対応付けられており、制御値が示す対応関係における制御電圧に応じた発振周波数を有する出力信号を出力する。

(もっと読む)

スペクトラム拡散クロック生成器及び半導体装置

【課題】回路規模の大きなDACやアナログ変調回路を用いずに理想的な周波数特性を得ることが可能なスペクトラム拡散クロック生成器及びスペクトラム拡散クロック生成器を備えた半導体装置を提供する。

【解決手段】動作クロックを生成する電圧制御発振器と、動作クロックの位相と基準クロックの位相とを比較し比較結果により電圧制御発振器の発振の基準となる電圧を生成する帰還制御部と、動作クロックの周波数に変動を与える成分をデルタシグマ変調したパルス信号として生成する変調パルス生成部と、パルス信号の振幅を設定するレベル設定部と、帰還制御部が生成した電圧とレベル設定部によって振幅が設定されたパルス信号とを加算する加算部と、加算部の出力信号を濾波して電圧制御発振器に与える制御電圧を生成する低域パスフィルタと、を備える。

(もっと読む)

クロック検出方法及びその装置

【課題】既存のクロック検出方法のリソース占用率が高い問題を解決できるクロック検出方法及びその装置を提供する。

【解決手段】該方法は、プログラマブル部品が、ローカルタイムソースにより生成されたソースクロック信号に周波数分割を行って参照クロック信号を取得し(S101)、プログラマブル部品が、ソースクロック信号をカウント動作クロックとし、検出対象クロック信号の、参照クロック信号の連続するN(Nは正整数である)個のハイ電圧レベルの各ハイ電圧レベル期間における立ち上がりエッジカウント値とハイ電圧レベルカウント値を確定し(S102)、プログラマブル部品が、検出対象クロック信号の、各ハイ電圧レベル期間におけるハイ電圧レベルカウント値と第1の所定値との大きさ関係、及び立ち上がりエッジカウント値と第2の所定値との大きさ関係に基づいて、検出対象クロック信号が有効であるかを確定する(S103)。本発明によると、少ないリソースを占め、クロック検出の信頼性が向上でき、また、検出対象クロック信号の周波数範囲が広くなり、検出対象クロック信号の高周波数グリッチによる影響を避けることができる。

(もっと読む)

多相発振器を有する位相ロックループ

位相ロックループが複数のデジタル入力を有する多相発振器を利用する。時間に関して互いにオフセットされた複数のDQフリップフロップが、複数の制御信号を生成して、発振器から制御位相情報をデジタル形式で取り出す。発振器における任意の2つのデジタル入力間に接続されたDQフリップフロップが、進行波の方向を判定する。その方向と位相情報とにより、ルックアップテーブルがアドレス指定され、発振器の現時点のフラクショナル位相が判定される。発振器周波数を低減するために、N分周回路が用いられる。発振器に関する全位相表示信号が、現時点のフラクショナル位相を用いて判定される。この全位相を基準位相と比較して、発振器に対する修正を行うための制御信号を生成する。フィードフォワード経路において、分周器が、発振器からの高周波信号をより低い所望の周波数に分割し、それにより位相分解能を向上させる。 (もっと読む)

デジタルフェーズロックドループ回路

【課題】安定した位相同期ループを構成できない。

【解決手段】本発明は、第1、第2のクロック信号をカウントする第1、第2のカウンタと、第1のクロック信号を遅延させた第1、第2の遅延クロック信号を生成する遅延クロック生成回路と、第1のクロック信号及び第1、第2の遅延クロック信号のそれぞれで第2のカウンタのカウント値をサンプリングするサンプル回路と、第1、第2のクロック信号を所定の数で分周した第3のクロック信号との位相差と、サンプリングしたカウント値に応じ、そのサンプリングしたカウント値のうち1つを選択する選択回路と、第1のカウンタ及び選択回路が選択したカウント値に応じて第1、第3のクロックとの位相差を演算する位相誤差演算回路と、位相誤差演算回路の演算結果に応じて第2のクロックを出力するデジタル制御発振器とを有するデジタルフェーズロックドループ回路である。

(もっと読む)

半導体集積回路

【課題】増幅回路やBPF/BRFを必要とせず、回路面積および消費電力を削減することができる半導体集積回路を提供することである。

【解決手段】半導体集積回路300は、第1の周波数を有する第1の電圧信号と、第1の電圧信号の位相反転した第2の電圧信号と、第1の電圧信号の位相直交した第3の電圧信号と、第3の電圧信号の位相反転した第4の電圧信号とが入力され、及び、第2の周波数を有する第5の電圧信号と、第5の電圧信号の位相反転した第6の電圧信号と、第5の電圧信号の位相直交した第7の電圧信号と、第7の電圧信号の位相反転した第8の電圧信号とが入力されて、第1の周波数と前記第2の周波数とを加算または減算して複数の電流信号として、所定の出力径路から出力する、ミキサ回路部100と、複数の電流信号を用いて2分周を実行する2分周部200と、を有し、所定の出力径路上にバイアス電流が流れるものである。

(もっと読む)

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

半導体装置

【課題】フラクショナルN−PLL回路における出力クロック信号でのスプリアスの発生を抑制する。

【解決手段】出力クロック信号を出力する電圧制御発振器と、出力クロック信号を分周して分周クロック信号を生成し、基準クロック信号と分周クロック信号とを比較し、比較結果に基づき出力信号を出力するN個の制御ユニットと、各制御ユニットからの出力信号を加算する加算器と、加算器の出力をフィルタ処理し電圧制御発振器に出力するローパスフィルタとを備え、分周クロック信号に同期して所定の順序で巡回させ供給するN個のデータからなる分周比に係る設定情報を、各制御ユニットに対して初期値を互いに異ならせて供給し分周動作及び比較動作を行わせるようにして、N個の制御ユニットにより移動平均フィルタを形成し量子化ノイズを低減し、出力クロック信号でのスプリアスの発生を抑制できるようにする。

(もっと読む)

サプライレギュレートされたフェイズロックループ(PLL)及び用いる方法

サプライレギュレートされたフェイズロックループ(PLL)が提供される。PLLは、サプライレギュレーティングループ、電圧制御発振器(VCO)、及びVCOのためのプログラマブルデカップリングキャパシタアレイを備える。VCOデカップリングキャパシタアレイのキャパシタンスは、NかけるCUNITに等しくなるように調整可能であり、NはN分周回路の乗算ファクタの現在の値であり、CUNITはデカップリングキャパシタアレイを製造するために選ばれたプロセス技術に対して特徴付けられたユニットキャパシタンスである。PLLが1つの周波数帯から他にスイッチするとき、VCOデカップリングキャパシタによって導入される高次ポールがPLL参照周波数をトラックし、PLLの動作安定性を改善する。  (もっと読む)

(もっと読む)

信号周波数変更回路及びその周波数変更方法

【課題】デューティサイクルエラーを最小化し、消費電流を減少させる。

【解決手段】信号周波数変更回路は、クロック信号を遅延制御信号に相応する第1遅延時間だけ遅らせて遅延信号を生成し、前記クロック信号を前記第1遅延時間に比べて小さい第2遅延時間だけ遅らせて予備周波数変更クロック信号を生成する遅延線;位相固定完了信号を生成する検出部;前記位相固定完了信号の活性化時点の以前まで供給される前記クロック信号を利用して、前記遅延制御信号及び多重化制御信号を順次シフトさせる制御部;前記多重化制御信号に応じて、前記予備周波数変更クロック信号のうちから1つを選択して出力するマルチプレクサ;及び前記クロック信号と前記マルチプレクサの出力信号を利用して、前記クロック信号の周波数と異なるように変更された周波数を有する周波数変更クロック信号を生成する出力部を備える。

(もっと読む)

PLL回路

【課題】温度変動による位相雑音の悪化を低減することが可能なPLL回路を提供することを目的とする。

【解決手段】電圧制御発振回路81と、分周器82と、基準信号REF-INと発振信号Outputとの互いの位相を比較し、位相差に応じたパルス幅のパルス信号UP、DOWNを出力する位相比較器と、パルス信号UP、DOWNのパルス幅に応じた大きさのCP電流ICPp、ICPnを出力する出力電流補正機能付きチャージポンプ1と、CP電流ICPp、ICPnに応じてVt電圧を制御するループフィルタ85と、温度変動に応じて遅延時間が変化する遅延回路8とを備えてPLL回路100を構成し、遅延回路8の遅延時間に基づいて、CP電流ICPpとCP電流ICPnとの差が小さくなるように、CP電流ICPp又はCP電流ICPnを補正する。

(もっと読む)

デューティ検出回路及びこれを備えるクロック生成回路、並びに、半導体装置

【課題】デューティ検出信号を高頻度に更新する。

【解決手段】内部クロックRCLK,FCLKのデューティを検出する複数のデューティ検出部210−1〜210mと、複数のデューティ検出部を互いに異なる位相で動作させる制御部220と、複数のデューティ検出部からのデューティ検出信号を選択する出力選択部230とを備える。本発明によれば、複数のデューティ検出部が互いに異なる位相で動作することから、各デューティ検出部におけるデューティ検出信号の生成頻度よりも高頻度でデューティ検出信号DCCSを出力することが可能となる。このため、本発明によるデューティ検出回路をDLL回路のクロック調整に使用すれば、DLL回路の制御周期を短縮することが可能となる。

(もっと読む)

位相比較装置

【課題】高速動作するBang-Bang型位相比較回路の出力パルスに歪や欠損がある場合であっても、チャージポンプやA/D変換器を用いることなく、進相、遅相のいずれであるかを正確に表すデジタル信号を得る。

【解決手段】Bang-Bang型の位相比較回路10と、該位相比較回路の進相出力パルスおよび遅相出力パルスを入力して遅相/進相の識別を行う位相比較結果識別回路20とを備える。位相比較結果識別回路20は、位相比較回路10の進相出力パルスによってリセットされた後にクロック信号のカウントを行い所定のカウント値に達すると遅相を示す信号を出力する第1カウンタ回路21と、位相比較回路10の遅相出力パルスによってリセットされた後に前記クロック信号のカウントを行い所定のカウント値に達すると進相を示す信号を出力する第2カウンタ回路22と、前記遅相を示す信号と前記進相を示す信号を入力して進相/遅相の識別信号を出力する識別回路23とを具備する。

(もっと読む)

61 - 80 / 200

[ Back to top ]