Fターム[5J039MM06]の内容

Fターム[5J039MM06]に分類される特許

1 - 20 / 71

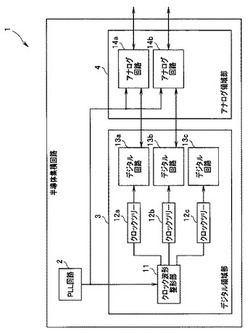

半導体集積回路

【課題】クロック信号の立ち下がりエッジで発生する消費電力を低減することができる半導体集積回路を提供することである。

【解決手段】実施の形態の半導体集積回路は、クロック信号生成部と、クロック波形整形部と、複数の機能ブロックとを有する。クロック信号生成部は、所定の周波数のクロック信号を生成する。クロック波形整形部は、クロック信号生成部で生成されたクロック信号と立ち上がりエッジの位相が同一で、かつ立ち下がりエッジの位相が異なる複数のクロック信号を生成する。複数の機能ブロックは、それぞれがクロック波形整形部で生成された複数のクロック信号のいずれかで動作する複数のフリップフロップを有する。

(もっと読む)

信号発生装置および試験装置

【課題】エッジの位相を固定して、信号のデューティ比を変更する。

【解決手段】指定されたデューティ比の出力信号を出力する信号発生装置であって、入力信号と出力信号との位相差を検出する位相検出器と、位相検出器により検出された位相差をフィルタリングして、発振器に供給するループフィルタと、位相差に応じた周波数の発振信号を出力する発振器と、指定値に応じて発振信号のデューティ比を変更して出力信号として出力するとともに位相検出器に供給するデューティ変更部と、を備える信号発生装置を提供する。

(もっと読む)

半導体集積回路

【課題】分周信号を検査するにあたって、その周波数のみならず第1区間長および第2区間長をも検査し、比較対象に用いる信号を生成する高価な検査装置を必要としない自己診断回路を有する半導体集積回路およびその検査方法を提供する。

【解決手段】分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわち第1区間および第2区間の比率、の2つに対して行う。外部からはデューティー比を定義する2つの期待値を供給する。

(もっと読む)

クロック逓倍回路、固体撮像装置及び位相シフト回路

【課題】クロック周波数が大きく変動しても、所望のデューティ比のクロック信号を精度よく生成する。

【解決手段】クロック逓倍回路10を、第1インバータ2と、第2インバータ3と、容量素子4と、電流供給部1と、差動検出部6と、逓倍信号生成部9とを備える構成とする。本発明では、電流供給部1は、第1クロック信号CKの周波数が高くなると電流を増大して第1インバータ2及び第2インバー3の電流シンク端子2aに該電流を供給する。また、差動検出器6は、容量素子4の両電極間の電位差信号が入力され、該電位差信号の変化範囲の中間値における比較結果に基づいて、第1クロック信号CKの正相信号に対して90度の位相差を有する第2クロック信号Xを生成する。そして、逓倍信号生成部9は、第1クロック信号CK及び第2クロック信号Xに基づいて第1クロック信号CKの2逓倍信号を生成する。

(もっと読む)

クロック調整回路、デューティ比のずれ検出回路、撮像装置、及び、クロック調整方法

【課題】クロック信号のデューティ比が所望の値からずれても、デューティ比のずれを高精度に検知して補正する。

【解決手段】本発明のクロック調整回路は、第1スイッチ素子21と、第2スイッチ素子22と、第3スイッチ素子23と、第4スイッチ素子24と、第1容量素子25と、第2容量素子26と、ずれ検出部27とを備える構成とする。本発明では、第1スイッチ素子21及び第2スイッチ素子22からなる回路に、正相のクロック信号を印加する。また、第3スイッチ素子23及び第4スイッチ素子24からなる回路に逆相のクロック信号を印加する。そして、ずれ検出部27は、第1スイッチ素子21の出力端C及び第3スイッチ素子23の出力端D間の電位差に基づいてクロック信号のデューティ比のずれを検出する。

(もっと読む)

デューティ比自動調整コンパレータ回路

【課題】電源電圧などの回路の動作条件の変動に関わらず、デューティ比の変動を抑圧、低減する。

【解決手段】差動増幅回路1と、この差動増幅回路1において差動対を構成する2つのMOSトランジスタ21,22のソース同士の接続点における電位に基づいて閾値電圧を生成する閾値電圧生成回路2と、インバータ動作における閾値電圧を、閾値電圧生成回路2により生成された閾値電圧に設定可能に構成された閾値電圧可変インバータ回路3とが設けられることにより、インバータ動作における閾値電圧が、差動増幅回路1の出力振幅の中心電圧に設定でき、電源電圧の変動などが生じてもインバータの入出力間におけるデューティ比の変動が抑圧、低減できるものとなっている。

(もっと読む)

周波数逓倍トランシーバ

デューティ補正回路、遅延同期ループ回路、カラムA/D変換器、固体撮像素子およびカメラシステム

【課題】デューティ比が50%より大きい場合も小さい場合も両方を一つの素子で対応が可能であり、素子数を削減できるだけではなく、スイッチング回数を削減することが可能で、消費電流を削減することができるデューティ補正回路、DLL回路、カラムA/D変換器、固体撮像素子、およびカメラシステムを提供する。

【解決手段】デューティ補正回路10は、第1入力および第2入力を有するC素子11と、C素子11の第2入力に接続されたインバータ12と、を有し、C素子11は、入力が両方とも論理“1”になると出力が論理“1”になり、入力が両方とも論理“0”になると出力が論理“0”になり、その他の状態では出力は前の状態を保持し、C素子11の第1入力およびインバータ12にそれぞれ互いに位相差がほぼ半周期の相補クロックが入力される。

(もっと読む)

遅延時間差測定回路

【課題】本発明の一実施例では、2つの信号間の遅延時間差を信号のエッジに応じて正確に測定する遅延時間差測定回路を提供することを目的とする。

【解決手段】上記課題を解決するため、2本の信号線の伝播遅延時間差を測定する遅延時間差測定回路は、該2本の信号線に接続され、選択信号に応じて一方の信号線を伝播する信号を出力する選択回路と、該選択回路に接続され、該選択回路の出力信号を一定時間遅延させて該選択信号として出力する切替回路と、該選択回路の出力側と該2本の信号線の入力側を接続する帰還経路と、該帰還経路に接続され、該帰還経路を伝播する信号の自己発振周期に基づいて該2本の信号線を伝播する信号の遅延時間の差を算出する制御回路とを有する。

(もっと読む)

インダクタオーバーヘッドなしで共振クロック分配ネットワークの固有周波数を選択する方法

共振クロック分配ネットワークのためのインダクタアーキテクチャが提示される。このアーキテクチャにより、選択的にインダクタを切り離すことによって共振クロック分配ネットワークの固有周波数の調整が可能になり、複数のクロック周波数でエネルギ効率の良い作動が実現する。提示されたアーキテクチャは、主として統合されたインダクタを備える共振クロックネットワーク設計を対象としており、面積オーバヘッドが現れない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

共振クロック分配ネットワークの周波数スケール調整された作動のためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。このアーキテクチャにより、選択的にイネーブルされるフリップフロップの導入によって、複数のクロック周波数での共振クロック分配ネットワークのエネルギ効率の良い作動が可能になる。提示されたアーキテクチャは、主として一体化インダクタを有する共振クロックネットワーク設計を目的としており、インダクタのオーバヘッドが出現しない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

プログラム可能な駆動回路を備えた共振クロック分配ネットワークアーキテクチャ

プログラム可能なサイズのクロック駆動回路及びプログラム可能なデューティサイクルの基準クロックを使用して、共振又は非共振モードで複数のクロック周波数の中の任意の1つの周波数で作動する場合に小さなエネルギ消費で目標クロック立ち上がり時間及びクロック振幅を実現する共振クロック分配ネットワークアーキテクチャが開示さる。一般に、このネットワークは、複数のクロック周波数をもつ半導体デバイス、及び高性能で低電力クロックを必要とするマイクロプロセッサ、ASIC、及びSOC等に適用可能である。 (もっと読む)

共振クロックネットワークを従来モードで作動させるためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。提示されたアーキテクチャにより、共振クロック分配ネットワークの従来モードでのエネルギ効率の良い作動が可能になり、クロック波形の目標仕様を満たすことができる。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、アットスピード試験及び達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

半導体装置及び位相検知回路

【課題】位相検知の誤判定を防止した高精度の位相検知回路を提供する。

【解決手段】電源線VSS1とセンスノードLSAT、LSAB間に、nMOSトランジスタの組(M1、M2、M3)、(M4、M5、M6)を備え、各トランジスタのゲートに内部クロックRCLK、RCLKのインバータINV1による反転信号、外部ロックCK、/CKをそれぞれ入力し、電源線VDD1とセンスノードLSAT、LSAB間に、pMOSトランジスタの組(MP1、MP2、MP3)、(MP4、MP5、MP6)を備え、各トランジスタのゲートにFCLKのインバータINV2による反転信号、内部クロックRCLK、外部ロックCK、/CKをそれぞれ入力し、センスノードLSAT、LSABは差動アンプAMPで増幅されラッチ回路L1でラッチされる。pMOSトランジスタ(MP11、MP12、MP13)はLSAT、LSABをプリチャージ・イコライズする。

(もっと読む)

サンプリングミキサ回路

【課題】サンプリングパルスの周波数を高めたりデューティ比を特別に絞り込むことなく実効的にデューティ比の小さいサンプリングパルスを得ることができ、従って、高域までの周波数特性に関する要求水準が緩和されたサンプリングミキサ回路を提供する。

【解決手段】サンプリングに適用する各キャパシタC1〜C4の充電経路となる各電流パス113−1,113−2,113−3,113−4を第1スイッチおよび第2スイッチの直列接続回路を含むように構成し、これら各電流パスが所定の各位相差で順次周期的に導通すると共に各電流パス毎の第1および第2スイッチが所定の位相差でオンになる多相のサンプリングパルスを各対応する第1スイッチおよび第2スイッチに供給することによって、各電流パスにおける導通状態の繰り返しに関するデューティ比が上記サンプリングパルスのデューティ比よりも小さくなるようにする。

(もっと読む)

閉ループ・クロック訂正方法および閉ループ・クロック訂正制御システム適応装置

【課題】閉ループ・クロック訂正方法および閉ループ・クロック訂正制御システム適応装置を提供する。

【解決手段】閉ループ・クロック訂正システムおよび方法は、少なくとも1つの同位相クロックおよび少なくとも1つの直交位相クロックを含む2つ以上の入力信号を調整するステップと、調整された直交位相クロック信号を、4象限補間出力クロック位相を生成可能なデバイスに印加するステップとを含む。補間出力クロック位相は、遅延されて測定デバイス用のクロックを形成する。2つ以上の調整された入力信号は、測定デバイス上で補間出力クロック位相の範囲にわたって測定される。測定デバイスからのサンプル情報を使用して、同位相クロックおよび直交位相クロック上の誤差が決定される。同位相クロックおよび直交位相クロックは、決定された誤差情報を使用して適応される。

(もっと読む)

高周波電源装置

【課題】安定したパルス高周波電力を供給することができる高周波電源装置1を提供する。

【解決手段】高周波電源装置1は、パルス高周波電力の出力電圧を検出して包絡線検波を行い、その検波信号をサンプルホールド部6によりサンプリングし、サンプリング電圧Vsを高周波電力生成部3にフィードバックしてパルス高周波電力Poutの制御を行う。サンプルホールド部6は、サンプルホールド信号のオン期間中、検波信号Paをサンプリング電圧Vsとして出力し、サンプルホールド信号のオフ期間中、サンプルホールド信号がオンからオフへ切り替るタイミングの検波信号Paの電圧レベルをホールドして、サンプリング電圧Vsとして出力する。

(もっと読む)

信号周波数変更回路及びその周波数変更方法

【課題】デューティサイクルエラーを最小化し、消費電流を減少させる。

【解決手段】信号周波数変更回路は、クロック信号を遅延制御信号に相応する第1遅延時間だけ遅らせて遅延信号を生成し、前記クロック信号を前記第1遅延時間に比べて小さい第2遅延時間だけ遅らせて予備周波数変更クロック信号を生成する遅延線;位相固定完了信号を生成する検出部;前記位相固定完了信号の活性化時点の以前まで供給される前記クロック信号を利用して、前記遅延制御信号及び多重化制御信号を順次シフトさせる制御部;前記多重化制御信号に応じて、前記予備周波数変更クロック信号のうちから1つを選択して出力するマルチプレクサ;及び前記クロック信号と前記マルチプレクサの出力信号を利用して、前記クロック信号の周波数と異なるように変更された周波数を有する周波数変更クロック信号を生成する出力部を備える。

(もっと読む)

デューティ検出回路及びこれを備えるクロック生成回路、並びに、半導体装置

【課題】デューティ検出信号を高頻度に更新する。

【解決手段】内部クロックRCLK,FCLKのデューティを検出する複数のデューティ検出部210−1〜210mと、複数のデューティ検出部を互いに異なる位相で動作させる制御部220と、複数のデューティ検出部からのデューティ検出信号を選択する出力選択部230とを備える。本発明によれば、複数のデューティ検出部が互いに異なる位相で動作することから、各デューティ検出部におけるデューティ検出信号の生成頻度よりも高頻度でデューティ検出信号DCCSを出力することが可能となる。このため、本発明によるデューティ検出回路をDLL回路のクロック調整に使用すれば、DLL回路の制御周期を短縮することが可能となる。

(もっと読む)

非重複クロック生成のための技術

【解決手段】望ましい周波数範囲にわたって、正確な非重複時間及びクロックフェーズ遅延時間を生成する技術が提供される。一構成において、装置はそれに結合されるクロック生成回路への制御電圧を順に生成する遅延ロックループ(DLL)回路を含む非重複クロック生成回路を備えている。制御電圧はクロック生成回路によって生成される非重複遅延クロック信号の正確なタイミング関係を維持するように動作する。一態様において、DLL回路は知られたデューティサイクルによる入力クロックを受信し、入力クロックサイクルの特定の部分へのユニット遅延をフィックスする出力制御電圧を得る。更なる態様において、クロック生成回路は製造プロセス変化とは関係ない非重複時間(tnlp)でクロック信号の第1のセットから遅延されたクロック信号の第2のセット及びクロック信号の第1のセットを生成するDLL回路に結合される複数の電圧制御遅延セルを備えている。 (もっと読む)

1 - 20 / 71

[ Back to top ]