Fターム[5J039MM11]の内容

Fターム[5J039MM11]に分類される特許

1 - 20 / 131

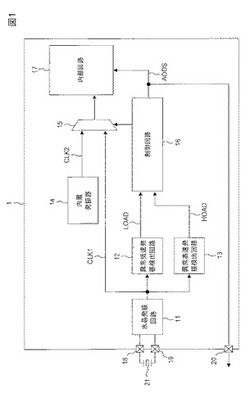

半導体集積回路装置

【課題】半導体集積回路装置の内部回路に供給されるクロック信号の周波数が、正常時よりも高くなった場合の上記内部回路の暴走を回避する。

【解決手段】半導体集積回路装置(1)において、内部回路(17)と、水晶振動子を用いた発振動作によりクロック信号を形成する水晶発振回路(11)と、上記内部回路が正常に動作可能な周波数のクロック信号を形成する内蔵発振器(14)とを設ける。また上記水晶発振回路で形成されたクロック信号の周波数が、上記内部回路の正常動作の周波数範囲よりも上昇したことを検出可能な異常高速発振検出回路(13)を設ける。さらに上記異常高速発振検出回路での検出結果に基づいて、上記水晶発振回路で形成されたクロック信号に代えて、上記内蔵発振器で形成されたクロック信号を上記内部回路に供給するための制御回路(16)を設けることで、内部回路の暴走を回避する。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】第1のクロック分配回路は、タイミング信号を複数の第1の分配点に分配する。第2のクロック分配回路は、タイミング信号を複数の第2の分配点に分配する。最小遅延クロック信号出力部は、複数の第1の分配点のいずれかに分配されたタイミング信号と複数の第2の分配点のいずれかに分配されたタイミング信号とのうち遅延が小さい方の信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。

(もっと読む)

遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法

【課題】簡易な処理によって遅延素子の遅延情報を出力する遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法を提供すること。

【解決手段】本発明にかかる遅延検出回路10は、基準信号生成部11と、遅延チェーン12と、保持部13と、を備える。基準信号生成部11は、クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくともクロック信号の一周期の間は第2のレベルが維持される基準信号を生成する。遅延チェーン12は、多段接続された複数の遅延ゲート12−1〜12−nを有し、基準信号が入力される。保持部13は、クロック信号に同期して複数の遅延ゲート12−1〜12−nの出力信号を保持し、前記遅延手段の遅延情報を出力する。

(もっと読む)

半導体集積回路及び半導体集積回路の検査方法

【課題】ジッタ耐性検査における検査コストの低減を図りつつ、入力される主信号の特性劣化を抑制できる半導体集積回路を提供する。

【解決手段】半導体集積回路101は、主信号にジッタ信号が付加されてなる検査信号を生成する機能を有し、ジッタ信号の基となる信号を生成するジッタ信号生成部50と、電源線Vccと接地線GNDとの間に介在し、電源線Vccからの電力供給を受けて外部からの主信号を増幅して出力するバッファ回路10と、電源線Vccとバッファ回路10との間およびバッファ回路10と接地線GNDとの間に介在し電源線Vccからバッファ回路10への供給電力をジッタ信号の基となる信号の大きさに基づいて変化させることにより主信号にジッタ信号を付加するジッタ信号付加部30とを備える。

(もっと読む)

非同期データ転送装置

【課題】電流量の監視による遅延仮定なしで配線故障検出ができ、遅延故障耐性と配線故障耐性を同時に有した非同期データ転送装置を提供する。

【解決手段】IPコア間に配設するLSIの非同期データ転送装置1において、第1のIPコアに接続する第1の配線3aと、第2のIPコアに接続する第2の配線3bと、第1の配線3aに接続する送信器2と、第2の配線3bに接続する受信器4と、送信器2と受信器4とを接続する第3の配線3cと、を含み、送信器2は、符号器5と入力制御部6とを有する入力部2Aと、出力部2Bと、を含み、受信器4は、入力部4Bと、復号器7と出力制御部8とを有する出力部4Aと、を含み、送信器2の符号器5は、第3の配線3cのオープン故障を検出する電流ドライバ回路11a,11b,11c,11dを備える。

(もっと読む)

位相差検証回路

【課題】別途、基準クロックなどを用意することなく、複数のクロック信号間の位相差が一定であるか否かを検証することができる位相差検証回路を得ることを目的とする。

【解決手段】AND回路11−0〜11−7からパルス信号#0〜#7が出力されている期間中、電荷を蓄積するキャパシタチャージ回路13−0〜13−7を設け、比較回路14が、キャパシタチャージ回路13−0〜13−7により蓄積された電荷の充電量を示す電圧信号Vout#0〜#7を比較し、その電圧信号Vout#0〜#7が一致していれば、クロック信号#0〜#7間の位相差が一定であることを認定する。

(もっと読む)

ピークホールド回路のリセット装置

【課題】安価な構成で適切なタイミングにリセット信号を出力させる。

【解決手段】A/D変換回路3からデジタル信号として入力されるホールドコンデンサCのホールド電圧の電圧レベルの増加を検出したときに、増加前後の電圧レベルの差をコンパレータ5aによって求める。そして、求めた差が所定のしきい値以下である場合は、リセット信号を出力する。よって、入力信号Vinの入力に伴うホールドコンデンサCのホールド電圧の増加量が、ホールド電圧の飽和判断に適した所定のしきい値以下になった時点で、初めてホールドコンデンサCをリセットしてホールド電圧を放電させる。これにより、ホールドコンデンサCの1回目のチャージ時点におけるホールド電圧に比べてはるかに、入力信号Vinの反転信号の電圧レベルのピーク値に近い値にホールド電圧が達するまで、ホールドコンデンサCをチャージさせた時点で、リセット信号を確実に出力することができる。

(もっと読む)

バイポーラ信号の周波数測定方法および装置

【課題】正パルスおよび負パルス間の位相偏差に影響されることなくバイポーラ信号の周波数を正確に測定する。

【解決手段】バイポーラ信号をB/U変換110した被測定クロックのパルス列の立ち上がりを第1カウンタ120でカウントし、当該カウント値を基に測定期間を設定する。このとき、測定期間の開始および終了のタイミングを決める各パルスの極性が一致するようにしておく。そして、基準クロックに従いカウント動作する第2カウンタ130を上記測定期間で有効にし、該第2カウンタのカウント値を用いて被測定クロックの周波数を算出する。

(もっと読む)

ハイサイドスイッチ回路、インターフェイス回路、および電子機器

【課題】ハイサイドスイッチの過電流の検出精度を高めることが可能なハイサイドスイッチ回路、および、そのハイサイドスイッチ回路を含む装置を提供する。

【解決手段】ハイサイドスイッチ回路10は、入力端子11と出力端子12との間に電気的に接続されるスイッチ(MOSトランジスタ15)と、ゲート制御部16と、過電流検出部20とを備える。過電流検出部20は、抵抗素子21と、比較器22とを含む。比較器22は、抵抗素子21の電圧V1がしきい電圧を超える場合に、過電流を検出する。比較器22は、過電流時の検出電圧V1がしきい電圧を上回るように、予め調整される。抵抗素子21の抵抗値の精度が高くない場合にも、比較器22の調整によって、過電流の検出精度が高められる。

(もっと読む)

パルス変調型光検出装置及び電子機器

【課題】被検出対象が無いにも関わらず、物体有りと誤って判定される誤動作が生じないパルス変調型光検出装置及び電子機器を提供する。

【解決手段】パルス変調型光検出装置50は、増幅パルス信号S5と同期タイミングパルス信号S2とが同期するか否かを判定し、増幅パルス信号S5と同期タイミングパルス信号S2とが同期していないと判定したとき、同期タイミングパルス信号S2の生成を停止させる停止信号S501を同期タイミング回路5へ出力する外乱光検知部200を備える。

(もっと読む)

データ判定回路、受信器およびデータ判定方法

【課題】 データ判定回路の回路規模を大きくすることなく、孤立パルスを確実に検出する。

【解決手段】 閾値判定部は、2値データのデータ列を表すアナログデータ信号をオーバーサンプルすることにより生成されるデジタルコードを順に受け、負のデジタルコードが連続するときに増加値を示す閾値信号を出力し、正のデジタルコードが連続するときに減少値を示す閾値信号を出力する。孤立パルス判定部は、デジタルコードに閾値信号が示す値を加えて補正デジタルコードを生成し、連続する補正デジタルコードを用いて孤立パルスを検出する。バイナリ判定部は、連続するデジタルコードの符号を用いて2値データの論理を求める。データ選択部は、孤立パルスが検出されるときに、孤立パルスの論理を2値データの論理として出力し、孤立パルスが検出されないときに、バイナリ判定部により求められた2値データの論理を出力する。

(もっと読む)

CDR回路、受信装置、および通信システム

【課題】簡易な回路構成で、高速かつジッタ入力に強く、信号エラーの発生を抑止することが可能なCDR回路、受信装置、および通信システムを提供する。

【解決手段】CDR回路310は、遅延素子312−1〜312−4を含み、定期的に信号遷移の挿入されたデータ入力をトリガとしてクロックを抽出する分周器320と、分周器で抽出されたクロックに同期して入力データ信号をラッチするラッチ315−1〜315−8とを有する。

(もっと読む)

発振回路動作状態検出回路

【課題】発振回路の動作状態を短時間で検出する。

【解決手段】VDDの電源端子とVSSの電源端子の間にノードN1を共通接続点とするトランジスタMP1,MN1を直列接続し、ノードN2を共通接続点とするトランジスタMP2,MN2を直列接続する。ノードN1,N2の間に容量C1を接続する。ノードN1,N2にNOR1の入力側を接続する。トランジスタMP1,MN1に直列に電流源I1を接続し、トランジスタMP2,MN2に直列に電流I2を接続する。トランジスタMN1,MN2のOFF抵抗をトランジスタMP1,MP2のOFF抵抗より小さくする。発振回路の発振クロック信号が第1の論理のとき、トランジスタMP1,MN2をONさせると共にトランジスタMP2,MN1をOFFさせ、第2の論理のとき逆にする。

(もっと読む)

データラッチ回路およびそれを用いた試験装置

【課題】多様な信号形式のDUTからのデータを取り込み可能なデータラッチ回路を提供する。

【解決手段】データ入力端子INは、シリアル形式のデータ信号DINが入力される。n個(nは2以上の整数)のクロック入力端子CLK1〜CLKnは、それぞれにクロック信号CLK1〜CLKnが入力される。ある入力フリップフロップFFiは、データ信号DINを対応するクロック信号CLKiに応じたタイミングでラッチする。シリアルパラレル変換器SPiは、シリアル形式のデータ信号DINを対応するクロック信号CLKiを用いてパラレル形式の中間データ信号DINTiに変換する。データセレクタMUX1は、n個の中間データ信号DINT1〜nのうち選択信号SELに応じたひとつを選択する。

(もっと読む)

誤り検出回路及び集積回路

【課題】メモリ等の入力対象に入力される信号の誤判定を行うのに好適な誤り検出回路を提供する。

【解決手段】集積回路1を、誤り検出回路2A〜2Cとメモリ回路3とを含み、誤り検出回路2A〜2Cを、クロック信号CKの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第1信号IN_A0〜IN_Anを出力するラッチ回路21A0〜21Anと、クロック信号CKを遅延時間t1だけ遅延させる遅延回路20Aと、遅延クロック信号CK_Aの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第2信号IN_B0〜IN_Bnを出力するラッチ回路21B0〜21Bnと、第1信号IN_A0〜IN_Anと第2信号IN_B0〜IN_Bnとが一致しているか否かを比較判定し、判定結果を示す第3信号COMP0〜COMPnを出力する比較回路24_0〜24_nとを含む構成とした。

(もっと読む)

半導体集積回路のクロック遅延調整回路およびその制御方法

【課題】回路規模が増大する問題があった。

【解決手段】複数の回路ブロックと、入力するクロック信号を遅延制御信号に基づいて遅延したクロック信号を対応する前記複数の回路ブロックに供給する複数のクロック遅延回路と、前記複数の回路ブロックの遅延試験を行う制御回路と、前記遅延試験の結果に応じて、前記複数の回路ブロックのうち遅延処理が必要な回路ブロックの情報を記憶する救済グループ記憶回路と、前記遅延試験の結果に応じて、前記複数の回路ブロックのうち遅延処理が必要な回路ブロックの遅延値情報を記憶する、所定数の遅延設定回路と、前記救済グループ記憶回路が記憶した回路ブロックの情報に対応したクロック遅延回路に対し、前記遅延設定回路が記憶した遅延値情報に応じた前記遅延制御信号を割り当てる遅延設定割当制御回路と、を有する半導体集積回路のクロック信号調整回路。

(もっと読む)

再送判定装置、再送判定方法、再送判定プログラム、及び再送判定システム

【課題】多様なクライアントに柔軟に対応することを課題とする。

【解決手段】再送判定サーバ10は、クライアント40を識別する識別情報に対応付けて再送判定方式を記憶する再送判定方式情報テーブル21を備える。再送判定サーバ10において、要求メッセージ受信部31は、クライアント40から要求メッセージを受信する。再送判定方式決定部32は、要求メッセージから識別情報を抽出し、該識別情報に対応付けて記憶された再送判定方式を再送判定方式情報テーブル21から取得することで、再送判定方式を決定する。再送判定実施部33は、決定された再送判定方式に従って、要求メッセージが再送されたものであるか否かを判定する。応答メッセージ送信部34は、判定結果に基づいて応答メッセージを作成し、該応答メッセージをクライアント40に送信する。

(もっと読む)

回路シミュレーション装置、回路シミュレーション方法及びプログラム

【課題】位相同期回路を含む回路シミュレーションにおいて、フィードバックループに分周器が存在している場合であっても正確にシミュレートできるようにすること。

【解決手段】フィードバックループに設けられた分周器の分周比を測定するための第1のクロック信号を生成する測定クロック生成部と、分周器が第1のクロック信号を受信して分周して出力した第2のクロック信号と、第1のクロック信号とを参照して、分周器の分周比を測定する分周比測定部と、入力クロック信号を受信し、入力クロック信号の周期と予め設定された逓倍比と測定された分周比の逆数に相当する逓倍比とに応じて、入力クロック信号を逓倍して第3のクロック信号として出力する逓倍クロック生成部と、第1のクロック信号及び第3のクロック信号を受信し、いずれかを出力クロック信号として出力するクロック出力制御部とを有する。

(もっと読む)

発振異常検出回路

【課題】発振回路の発振周波数の異常を検出することができる発振異常検出回路を提供することである。

【解決手段】クロック信号CLKを、直列接続された複数の遅延素子20〜25を用いて遅延させる遅延部2と、遅延素子20〜25の出力信号であるクロック信号CLK0〜CLK5から、全体遅延時間tda内における、クロック信号CLKの変化を示す発振信号パターンD0〜D5を取得する信号パターン取得部3と、期待信号パターンE0〜E5を予め記憶する期待値記憶部4と、発振信号パターンD0〜D5と期待信号パターンE0〜E5とを比較する比較部5と、比較部5による比較結果が一致しない場合、発振回路100に発振異常が生じていると判定する異常判定部6とを備えた。

(もっと読む)

クロック異常検出回路

【課題】クロック異常を検出する精度を向上させる技術を提供する。

【解決手段】被検査クロックを遅延させる第1の遅延回路の出力と第2の遅延回路の出力よりLow期間を決める。定められたLow期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。第1の遅延回路の出力と第2の遅延回路の出力よりHigh期間を決める。定められたHigh期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。Low期間の異常とHigh期間の異常を統合する。

(もっと読む)

1 - 20 / 131

[ Back to top ]