Fターム[5J039NN02]の内容

Fターム[5J039NN02]に分類される特許

1 - 19 / 19

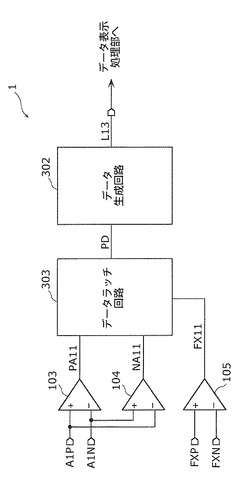

差動入力インターフェース回路、表示ドライバIC、表示パネルモジュールおよび画像表示装置

【課題】高速に伝送されてくるデータを安定して受信する差動入力インターフェース回路を提供する。

【解決手段】一対の差動信号を受信して正相データ信号PA11を出力する第1の差動アンプ103と、一対の差動信号を受信して負相データ信号NA11を出力する第2の差動アンプ104と、一対の差動クロック信号を受信して正相クロック信号FX11を出力する第3の差動アンプ105と、正相データ信号PA11と負相データ信号NA11とを正相クロック信号FX11に同期してラッチすることにより、ラッチ出力信号PDを出力するデータラッチ回路303と、ラッチ出力信号PDよりシングルエンドのデータ信号L13を生成するデータ生成回路302とを備える。

(もっと読む)

同期信号処理装置

【課題】回路の小面積化、低消費電力化を図ることが可能であり、しかも温度依存性の影響を受けない安定した位相比較が可能な同期信号処理装置を提供する。

【解決手段】水平同期信号を同期クロックで同期させ、当該同期クロックのタイミングでデジタルデータとして出力する時間デジタル変換器(TDC)と、同期クロックをカウントして参照クロックを生成する参照クロック生成部と、TDCによるデジタルデータと参照クロックの位相比較を行うことにより位相差情報を得るデジタル位相比較器と、デジタル位相比較器の位相差情報に応じて上記参照クロックとTDCによる水平同期信号のデジタルデータの位相が一致するように周波数が制御される同期クロックを生成する同期クロック生成装置と、を有する。

(もっと読む)

デジタル位相周波数検出器、それを含むデジタル位相固定ループ、及びデジタル位相周波数検出方法

【課題】デジタル位相周波数検出器、それを含むデジタル位相固定ループ、及びデジタル位相周波数検出方法を提供すること。

【解決手段】デジタル位相周波数検出器は検出部、位相比較部及びリセット部を含む。検出部は基準信号及びフィードバック入力信号のエッジを検出して基準エッジ信号及びフィードバックエッジ信号を発生する。リセット部は基準エッジ信号及びフィードバックエッジ信号に基づいてリセット信号を発生する。位相比較部は基準エッジ信号及びフィードバックエッジ信号に基づいて第1位相比較信号及び第2位相比較信号を発生し、第1フリップフロップ、第2フリップフロップ、及びラッチブロックを含む。第1フリップフロップは基準エッジ信号を受信するデータ入力端及びフィードバックエッジ信号を受信するクロック入力端を具備し、第2フリップフロップはフィードバックエッジ信号を受信するデータ入力端及び前記基準エッジ信号を受信するクロック入力端を具備する。

(もっと読む)

液晶駆動用のソースドライバのオフセットキャンセル出力回路

【課題】液晶駆動用のソースドライバのオフセットキャンセル出力回路を提供する。

【解決手段】基準電圧が非反転入力端に印加されたオペアンプと、反転入力端に各々の一端が接続された入力コンデンサ及び出力コンデンサと、反転入力端とオペアンプの出力端との間に接続された第1の電界効果トランジスタを有し、リセット動作時に入力コンデンサ及び出力コンデンサ各々にオフセット電圧を蓄電させ、通常出力動作時に入力コンデンサの他端に階調電圧を印加しかつ出力コンデンサの他端をオペアンプの出力端に接続するスイッチ素子回路と、を備え、リセット動作時及び通常出力動作時に第1の電界効果トランジスタの基盤に基準電圧に等しい第1の電位を印加し、通常出力動作中の階調電圧の切り替え時に第1の電界効果トランジスタのソース/ドレインから基盤に流れるリーク電流を防止するように基盤に第1の電位とは異なる第2の電位を第1の電位に代えて印加する。

(もっと読む)

クロック発生装置

【課題】出力するクロックの周波数を意識的に拡散して、テレビ受像機やパソコンモニタ映像受像機への電磁妨害のピークを減らすクロック発生装置を提供する。

【解決手段】周波数拡散情報発生回路90を設け、第二のDTO91と第二のDAC92にてデジタルLPF8から出力される位相誤差情報と周波数拡散情報から正弦波を発生し、アナログPLL93で逓倍することにより、クロック出力端子94から周波数拡散されたクロックを出力することができ、システムが用いる高い周波数からでる妨害を抑制するために意識的に周波数を拡散できるクロック発生装置を得ることができる。

(もっと読む)

データ送出装置、データ受信装置、及びデータ送受信システム

【課題】従来のHDMIのオーディオクロック伝送システムでは、サイクルタイムスタンプ値が変動してオーディオクロックの精度が劣化してしまう。

【解決手段】データのサンプルクロックを所定の分周比で分周してクロックを生成するクロック分周手段と、クロック分周手段で生成したクロックをカウントするカウント手段と、カウント生成手段で計測したカウント値を平均化する平均化手段と、平均化手段で取得した平均カウント値のビット数を削減するノイズシェーピング手段と、基本クロック、ノイズシェーピング手段で生成したカウント値及びクロック分周手段で使用した分周比を送出する送出手段を備える。

(もっと読む)

同期信号検出回路および半導体集積回路

【課題】水平方向の描画開始位置を決定する同期信号の検出精度を向上させることができる同期信号検出回路および半導体集積回路を提供する。

【解決手段】同期信号検出回路は、単位検出回路のうちの偶数番目の単位検出回路からなり、偶数番目の単位検出回路による単位検出結果にもとづいた偶数側検出結果を出力する偶数側検出回路と、奇数番目の単位検出回路からなり、奇数番目の単位検出回路による単位検出結果にもとづいて奇数側検出結果を出力する奇数側検出回路と、偶数側検出結果と奇数側検出結果とを比較し、比較の結果に応じて、偶数側検出結果と奇数側検出結果とのいずれかにもとづいて、有効エッジのタイミングを判定する判定回路とを有し、同期信号の有効エッジの多相クロック信号のクロックエッジに対するタイミングを判定する。

(もっと読む)

ミキサ

【課題】ダイレクトコンバージョン方式や低IF方式では局部発振器信号の高調波成分によるノイズを低減させる。

【解決手段】位相差がそれぞれ120°異なる3相信号を局部発振信号として受信信号と乗算し、それぞれの復調波の同相信号をキャンセルすることで、局部発振信号の高調波成分のうち、第3高調波によるノイズ成分をキャンセルすることができるミキサを提供する。

(もっと読む)

半導体集積回路

【課題】発振回路により作成される動作クロックによる不要な電磁輻射ノイズを低減する。

【解決手段】乱数発生回路10から出力された乱数データは、周波数可変データレジスタ12に格納される。周波数可変データレジスタ12に格納されるデータは、乱数発生回路10から順次発生される乱数データによって更新される。発振回路13はクロックを発生する回路であり、クロックは不図示の動作クロック作成回路を通して動作クロックとして、内部回路14に供給される。発振回路13のクロックの周波数は、周波数可変データレジスタ12に格納された乱数データに応じて可変制御されるようになっている。また、周波数可変データレジスタ12に格納された乱数データに応じて可変制御される周波数の幅を制御するための制御データが格納される周波数可変幅制御レジスタ15が設けられている。

(もっと読む)

周波数可変オシレータ

【課題】本発明は、入力信号の周波数が可変されも可変された入力信号の周波数により発振信号の周波数を可変する周波数可変オシレータに関するものである。

【解決手段】本発明は、入力信号の電圧レベルを事前に設定された範囲の電流レベルに変換する電圧電流変換回路と、上記電圧電流変換回路からの電流レベルにより周波数を可変して発振する発振回路を含むことを特徴とする。

(もっと読む)

比較回路

【課題】スイッチトキャパシタを利用し回路規模の小さな比較回路を得る。

【解決手段】入力INAは、スイッチSW1によりコンデンサCaを介し、コンパレータCom1,Com2の正入力端に供給される。入力INBはスイッチSW2によりコンデンサCb1を介しコンパレータCom1の負入力端に供給されると共に、スイッチ3,4によりコンデンサCb2を利用して反転されて、コンパレータCom2の負入力端に供給される。コンパレータCom1、Com2の出力は排他的論理和回路EXORに入力され、ここから入力INAが±入力INBの範囲内か否かの判定結果が出力される。

(もっと読む)

差動信号受信回路

【課題】従来の差動信号受信回路は、入力される差動信号の直流レベルや振幅の変動によって遅延時間が変動する問題があった。

【解決手段】本発明にかかる差動信号受信回路は、入力される差動信号に応じて、第1の電源電位と第1の電位差を有する上限値と、上限値と第2の電位差を有する下限値とを選択的に第1、第2の出力端子から出力する波形整形回路10と、第1、第2の出力端子の電圧を比較し、第1の電源電位と略同一の電圧と第2の電源と略同一の電圧とのいずれか一方を出力する増幅回路11とを有するものである。

(もっと読む)

半導体装置、表示装置、及び電子機器

【課題】ノイズによって誤動作することが少なく安定に動作し、消費電力が少なく、特性変動の少ない半導体装置、および前記半導体装置を有する表示装置、ならびに前記表示装置を有する電子機器を提供する。

【解決手段】出力端子を電源線に接続し、出力端子の電位変動を抑える。さらに、トランジスタの容量により、該トランジスタがオン状態となるゲート電極電位を維持する。また、逆バイアス用信号線により、トランジスタの特性変動を抑える。

(もっと読む)

信号分離回路および信号送信回路

【課題】 同一の信号線を介しての複数の信号の伝送を可能することを目的とする。

【解決手段】 同一の信号線から受信した複数のパルス信号を分離する信号分離回路21において、PCオン信号分離回路40が、信号線を介して受信したPC/TVオン信号から第1のパルス幅を有するPCオン信号を検出して対応する第1の出力信号を生成する。TVオン信号分離回路50が、PC/TVオン信号から第1のパルス幅よりも短い第2のパルス幅を有するTVオン信号を検出して対応する第2の出力信号を生成する。

(もっと読む)

ノイズ低減回路

【課題】 外部に高価なフレームメモリーを設けることなく雑音抑制を行うことができるノイズ低減回路を提供する。

【解決手段】 ノイズ低減回路は、複数の電荷蓄積手段2a〜2nと複数のスイッチ手段1a〜1nとを備えている。ノイズ成分を含む信号に応じた電荷量を複数の電荷蓄積手段2a〜2nに蓄積した後に、複数のスイッチ手段1a〜1nを導通させることによって複数の電荷蓄積手段2a〜2nを互いに並列に接続し、それによって、複数の電荷蓄積手段2a〜2nに蓄積されている電荷量を平均した電荷量と対応する信号を出力する。

(もっと読む)

クロック生成回路および映像信号合成回路

【課題】 簡単な構成で周波数変換ができるクロック生成回路を提供する。

【解決手段】 周波数13.5MHzのクロックから周波数12MHzのクロックを生成するクロック生成回路において、前記周波数13.5MHzの9個のクロック内の1個のクロックをマスクして、9個の入力クロック当り8個のクロックを出力させる。

(もっと読む)

半導体集積回路

【課題】本発明は、チャージポンプ回路で発生させた負電源を使用し、正負電圧に信号出力可能な映像出力回路を有する半導体集積回路において、負側の信号縮みを防止する半導体集積回路を提供する。

【解決手段】負電源電圧を発生するチャージポンプ回路と、映像信号の平均レベルを0Vでバイアスする入力部と映像信号出力回路を有する半導体集積回路において、映像信号出力の平均値を検波する平均レベル検波回路の出力と、映像信号出力の下限レベルを検波する下限レベル検波回路の出力とを判定し、標準映像信号入力時は0Vバイアス回路を、高輝度映像信号入力時はクランプバイアス回路を選択することにより、高輝度な映像信号入力時も出力信号の負側の歪みを防止し、正常な映像信号を出力することを可能にした。

(もっと読む)

ドライバ回路、シフトレジスタ及び液晶駆動回路

【課題】 表示部のトランジスタの動作速度を増加させ、かつこのトランジスタを駆動するa−Si TFT用の動作寿命が従来に比較して長いドライバ回路,シフトレジスタ、またこのシフトレジスタを用いた液晶駆動回路を提供する。

【解決手段】 本発明のドライバ回路は、しきい値電圧を制御するバックゲートが設けられており、ゲートに印加された電圧に対応して、ドレインから入力される電圧をソースから出力信号として出力するトランジスタが設けられている。

(もっと読む)

バッファ回路

【課題】レベルシフタバッファを効果的に構成する。

【解決手段】レベルシフタから、一対の相補的なクロック信号を出力する。各クロックは複数のインバータ14、16を介し出力されるが、一方の1段目のインバータ16−1をレベルシフタLSに近接して設け、次に他方の一段目のインバータ14−1を配置する。

(もっと読む)

1 - 19 / 19

[ Back to top ]