Fターム[5J042CA18]の内容

Fターム[5J042CA18]に分類される特許

1 - 20 / 55

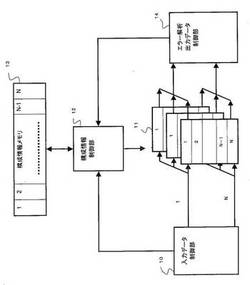

再構成可能な集積回路ユニットを備えた論理回路及びその論路回路のエラー修正方法

【課題】エラー箇所の特定を実施する際に、システムを停止しないでエラー発生前の高信頼性までシステム性能を復帰させる。

【解決手段】同一動作を行う複数個の再構成可能な集積回路ユニットを備え、複数の該集積回路ユニットのそれぞれに複数のバンクを有する論理回路において、入力されたデータを、複数個の前記集積回路ユニットの各バンクに振り分けて入力する入力データ制御部と、複数個の集積回路ユニットの各バンクから出力されるデータを比較して、データ間の不一致を検出するエラー解析部と、エラー解析部から、データ間の不一致の通知を受けた場合に、複数個の集積回路ユニットの該当するバンクの再構成を行う構成情報制御部と、を備える。

(もっと読む)

半導体集積回路

【課題】電源が遮断されてもデータが保持される新規な論理回路を提供する。また、消費電力を低減できる新規な論理回路を提供する。

【解決手段】2つの出力ノードを比較する比較器と、電荷保持部と、出力ノード電位確定部とを電気的に接続することにより、論理回路を構成する。それにより、電源が遮断されてもデータが保持される論理回路を得ることができる。また、論理回路を構成するトランジスタの総個数を低減させることができる。更に、酸化物半導体を用いたトランジスタとシリコンを用いたトランジスタを積層させることで、論理回路の面積の削減が可能になる。

(もっと読む)

論理回路、該論理回路を含む集積回路及び該集積回路の動作方法

【課題】論理回路、該論理回路を含む集積回路及び該集積回路の動作方法を提供する。

【解決手段】入力信号の電圧及び電流のうち少なくともいずれか一つによって変更される抵抗レベルを有し、抵抗レベルを記憶する少なくとも1つの可変抵抗素子を含み、少なくとも1つの可変抵抗素子に記憶された抵抗レベルに対応するマルチレベル・データをラッチする論理回路である。

(もっと読む)

半導体装置

【課題】耐タンパ性を有する、可変論理機能を実現するための記憶回路を有する半導体装置を提供する。

【解決手段】制御回路24は、記憶回路23の次の読出しアドレスを先に記憶回路23から読出した制御フィールドの情報または外部イベント入力に基づいて自律的に制御することが可能である。正規デコーダ28は、制御回路24から出力されるアドレスをデコードし、デコード結果に基づいて、データフィールドの少なくとも1つの正規メモリセルと、制御フィールドの少なくとも1つのメモリセルを選択する。冗長制御回路51は、イネーブル信号が活性化された場合に限り、制御回路24から出力されるアドレスと、所定の正規メモリセルのアドレスとが一致したときに、正規デコーダ28による選択を禁止し、データフィールドの少なくとも1つの冗長メモリセルと制御フィールドの少なくとも1つの冗長メモリセルを選択する。

(もっと読む)

ルックアップテーブル回路およびフィールドプログラマブルゲートアレイ

【課題】動作速度の速いルックアップテーブル回路およびフィールドプログラマブルゲートアレイを提供する。

【解決手段】ルックアップテーブル回路1は、入力信号に基づいて複数の抵抗変化型素子の中から一つの抵抗変化型素子を選択する抵抗変化回路2と、抵抗変化回路2の最大抵抗値と最小抵抗値との間の抵抗値を有する参照回路4と、抵抗変化回路2の他端にソースが接続された第1のnチャネルMOSFET6と、参照回路の他端にソースが接続された第2のnチャネルMOSFET8と、第1のnチャネルMOSFET6のドレインを通して抵抗変化回路2に電流を供給する第1の電流供給回路10と、第2のnチャネルMOSFET8のドレインを通して参照回路4に電流を供給する第2の電流供給回路12と、第1のnチャネルMOSFET6のドレイン電位と第2のnチャネルMOSFET8のドレイン電位を比較する比較器14と、を備える。

(もっと読む)

リコンフィギュラブル回路及びリコンフィギュラブル回路の駆動方法

【課題】単純な回路構成により演算実行のレイテンシを吸収できるリコンフィギュラブル回路を提供する。

【解決手段】リコンフィギュラブル回路は、複数のデータが全て同時に有効状態になると複数のデータに対して演算を実行し、複数のデータが全て同時に有効状態である間、演算により得られた演算結果を示す有効状態のデータを出力し続ける演算器を、複数個含むデータ演算部と、演算器間を再構成可能に接続するデータ選択部と、一連の演算を実行するようにデータ選択部により接続された一連の演算器に入力されるデータを入力データして保持するデータ入力部とを含み、データの有効及び無効状態は該データに対として付随する有効及び無効を示す信号により示され、一連の演算を実行する間はデータ入力部からデータ演算部に供給されている入力データを有効状態の同一データに固定しておく。

(もっと読む)

情報処理装置および回路再構成装置

【課題】情報処理を停止することなく、故障前と同じ情報処理を継続して実行する情報処理装置を得ること。

【解決手段】FPGAで構成されるとともに外部入力された入力情報に対して同じ情報処理を行う多重化された第1〜第3の処理系統11A〜11Cと、各処理系統から出力される処理結果の多数決を行なう多数決判定論理部15と、故障の発生した処理系統を検出する故障系統検出回路20と、故障が検出された際に、故障の発生した処理系統と同じ機能を有した処理系統をFPGAに再構成して新規な処理系統を形成する再構成部28と、を備え、各処理系統は、自身の回路状態を記憶する記憶部をそれぞれ有し、再構成部28は、故障が発生した際に、正常動作中の処理系統の記憶部に記憶させる回路状態と同じ情報を新規な処理系統の記憶部に入力し、その後、新規な処理系統に正常動作中の処理系統と同じ情報処理を行なわせる。

(もっと読む)

コンフィグレーション方法及びコンフィグレーション制御回路

【課題】コンフィグレーション方法及びコンフィグレーション制御回路において、FPGA回路のクロック周波数やスルーレート等のコンフィグレーションデータを自動調整可能にすることを目的とする。

【解決手段】FPGA回路のコンフィグレーションを行うコンフィグレーション方法において、コンフィグレーション回路からFPGA回路にコンフィグレーションデータを設定するコンフィグレーションが失敗した回数をFPGA回路内でカウントし、前記回数が上限値以下であると前記コンフィグレーションが失敗した時の前記コンフィグレーションデータを予め設定されているルールに従ってFPGA回路内で調整してコンフィグレーションを再実行し、前記コンフィグレーションが成功すると、成功した時点のコンフィグレーションデータをFPGA回路からコンフィグレーション回路に設定するように構成する。

(もっと読む)

半導体集積回路

【課題】被監視回路の動作を監視し故障している可能性がある場合にアラーム信号を出力する構成とする場合に、監視機能の喪失を招来する共通原因故障が発生しにくい監視回路を備えた半導体集積回路を提供すること。

【解決手段】処理経路に少なくとも1つ以上のフリップフロップ回路が存在する被監視回路と、処理経路に前記被監視回路のフリップフロップ回路に対応するフリップフロップ回路を有し、前記被監視回路の動作を模擬する模擬回路、および前記被監視回路の出力と前記模擬回路の出力とを比較し、比較結果に基づきアラーム信号を出力する比較回路を有する監視回路とを備え、前記被監視回路および前記模擬回路において互いに対応する前記各フリップフロップ回路は、同一のタイミングで動作するとともに、互いに論理を反転した信号をそれぞれ対応する後続回路へ出力するように制御されることを特徴とする。

(もっと読む)

通信回路、通信ネットワークおよび連結装置

【課題】信頼性の極めて高い通信を簡素な配線システムによって実現できる通信回路、通信ネットワークおよび連結装置を提供する。

【解決手段】3本以上の信号ライン2a,2b,2cからなる信号線2と、この信号線2の一端側に接続されて入力端子3iに入力された信号を各信号ライン2a,2b,2cに分配送信する信号分配部4と、前記信号線2の他端側に接続されて各信号ライン2a,2b,2cを介して受信する複数の受信信号を比較して一致数の多い受信信号を真として選択受信し出力端子3oに出力する多数決選択受信回路5とを備える。

(もっと読む)

集積回路及びコンフィギュレーション方法

【課題】同一装置内の同一品種のFPGAへの誤コンフィギュレーションを回避する。

【解決手段】FPGA特定用外部ピンとして同一品種でデバイスIDが同一の各FPGAの外部ピンK〜外部ピンNの4本の外部ピンが選択されている。FPGA1及びFPGA2は、外部ピンK〜外部ピンNの状態設定によって識別される。FPGA1及びFPGA2に対し、それぞれのコンフィグデータはFPGA特定情報として「外部ピンK=“0”、外部ピンL=“0”、外部ピンM=“0”、外部ピンN=“0”」、「外部ピンK=“0”、外部ピンL=“0”、外部ピンM=“0”、外部ピンN=“1”」の情報を含んでいる。このため、各FPGAのコンフィグデータでそれぞれコンフィギュレーションする場合、FPGA特定情報の一致により、対象とするFPGAに対応する正しいコンフィグデータをコンフィギュレーションすることが出来る。

(もっと読む)

楽音信号送信装置及び楽音信号受信装置

【課題】 部品点数が少なく、簡単な回路で構成でき、複数の楽音信号を1本の信号経路で送信又は受信できる楽音信号送信装置及び楽音信号受信装置を提供する。

【解決手段】 1ビットA/D変換部1L及び1Rにより、電子楽器などから入力された複数のアナログ楽音信号は各々1ビットデジタル信号に変換され、重み付け部2L及び2Rによりこれらの各1ビットデジタル信号は重み付け加算されて、出力部3により出力されることになると共に、受信部4により受信された重み付け加算信号は、分離部5により各1ビットデジタル信号に分離変換され、さらにD/A変換部6により、アナログ信号に復調されることになる。

(もっと読む)

ラッチ型コンパレータ及びこれを用いた多値論理復調回路

【課題】製造プロセスのマージンを削ることなく、オフセットの補正が可能なラッチ型コンパレータ、及びこれを用いた、オフセットの補正が可能な多値論理の復調回路を提供する

【解決手段】本発明によるラッチ型コンパレータは、クロスカップルされた2つのCMOSインバータからなるフリップフロップを含み、フリップフロップの4個のトランジスタの各々のソースと電源/接地間には伝達トランジスタを介して抵抗と設定電流可変の定電流源が接続され、フリップフロップの差動出力は各々伝達トランジスタを介して差動入力に接続され、全ての伝達トランジスタのゲートは、差動クロック入力のいずれかに接続されていることを特徴とする。

(もっと読む)

プログラマブルロジックデバイス、カード及び伝送装置

【課題】 冗長構成とすることなく、デバイスの運用を中断せずに機能の更新が可能となると共に、冗長分のコスト及び消費電力を削減できるプログラマブルロジックデバイス、カード及び伝送装置を提供する。

【解決手段】 FPGA10は、入力される入力信号を複数に分配し、論理ブロックに既に構成された論理回路1及び論理ブロックに新規に構成される新規な論理回路11に対して、分配された信号を出力する分配回路部2と、論理回路1及び新規な論理回路11からの各出力信号のうちいずれかを選択するセレクタ回路部3と、新規な論理回路11に出力信号を出力するように分配回路部2を制御すると共に、新規な論理回路11からの出力信号を出力するようにセレクタ回路部3を制御する切り替え制御部4と、を備える。

(もっと読む)

半導体集積回路装置及びアイ開口マージン評価方法

【課題】 高速シリアルデータ受信回路のアイ開口マージン評価として、クロック相を固定せず、クロックデータリカバリー回路の動作を含んだアイ開口マージン評価回路を提供する。また、位相情報にオフセットを与えることでジッタ成分を付加し、受信データエラー加速試験を可能にする。

【解決手段】 シリアルデータを受信するシリアライザ・デシリアライザ回路201(SerDes)と、並走クロック信号を受信する参照シリアライザ・デシリアライザ回路202(Ref_SerDes)とを有し、シリアライザ・デシリアライザ回路201(SerDes)は、参照シリアライザ・デシリアライザ回路202(SerDes)の生成した位相制御信号P_CSを用いて位相制御された再生クロックにより受信したシリアルデータの直列並列変換を行う。位相制御信号P_CSに、パルス生成回路602からのオフセット調整パルスOffset_Pulseを印加することで、アイ開口マージン評価を行う。

(もっと読む)

半導体集積回路

【課題】低消費電力化に適したAVS技術又はDVS技術を実現した半導体集積回路を提供すること。

【解決手段】半導体集積回路は、クリティカル・パスを形成する第1のフリップ・フロップ、組み合わせ回路及び第2のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第1の遅延回路及び第3のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第2の遅延回路及び第4のフリップ・フロップと、第2のフリップ・フロップの出力と第3のフリップ・フロップの出力とを比較する第1の比較回路と、第2のフリップ・フロップの出力と第4のフリップ・フロップの出力とを比較する第2の比較回路と、これら比較回路の出力に応じて、前記組み合わせ回路に供給される電源電圧を制御する制御回路とを備える。なお、第1の遅延回路による遅延時間と第2の遅延回路による遅延時間は異なる。

(もっと読む)

半導体デバイス

【課題】速度と歩留まりを向上させた半導体デバイスを実現する。

【解決手段】本発明の半導体デバイス1は、マトリックス状に配置された複数個のCLB3a〜3oと、SB4と、複数本のトラック5と配線経路変更部6とを備える。スイッチブロック4は、隣接する2個のCLB3間のトラック5のうちの1本と、隣接する他の2個のCLB間のトラック5のうちの1本とを接続し、スイッチブロック4の配線自由度は6である。

(もっと読む)

タグデータインポート方法およびプレデファインファイル用記録媒体

【課題】ラダープログラムファイルのデータに未定義のデータタイプが含まれている場合でも、画面表示プログラムファイルに読み込んで取り込めるようにする。

【解決手段】プログラマブル表示器のための画面表示プログラムファイルを作画エディタで作成する際に、PLCのためラダーエディタで作成したラダープログラムファイルのタグデータを上記画面表示プログラムファイルにインポートする方法であり、上記タグデータのデータタイプをプレデファインファイルで定義しそのプレデファインファイルを作画エディタのメモリに予め登録しておき、ラダープログラムファイルからタグデータを画面表示プログラムファイルにインポートするに際して上記プレデファインファイルを参照してインポートすることができるようにした。

(もっと読む)

リコンフィギュラブル論理回路

【課題】高集積化が可能なリコンフィギュラブル論理回路を提供する。

【解決手段】それぞれが個別の制御データを送信可能な複数の制御線と、ソースおよびドレインが磁性体を含む複数のスピンMOSFETと、複数のスピンMOSFETの中から1つのスピンMOSFETを選択する選択部と、を有するマルチプレクサと、マルチプレクサによって選択されたスピンMOSFETのソースおよびドレインにおける磁性体の磁化が第1状態か第2状態かを判別する判別回路と、選択されたスピンMOSFETに書き込み電流を流し、選択されたスピンMOSFETにおける磁性体の磁化を第2状態にする第1の書き込み回路と、マルチプレクサによって選択されたスピンMOSFETに書き込み電流を流し、選択されたスピンMOSFETにおける磁性体の磁化を第1状態にする第2の書き込み回路と、を備えている。

(もっと読む)

信号伝送システム

【課題】 信号配線数を増大させることなく、微細化等に伴う電源電圧の引き下げによる伝送品質への影響を低減できる信号伝送システムを提供する。

【解決手段】 送信回路10が、多値伝送データDCの値別に伝送データ用電流値を規定した信号変換条件に基づいて、送信対象の複数の2値電圧データを伝送データ用電流値の多値伝送データDCに変換し出力する多値伝送データ生成出力回路を備え、伝送データ用電流値の夫々が単位伝送データ用電流値の整数倍で規定され、多値伝送データ生成出力回路が、信号配線に対し単位伝送データ用電流値の電流を供給可能な単位電流駆動回路130を複数備えたデータ出力回路13と、複数の2値電圧データを多値電流データに変換した後の多値電流データの伝送データ用電流値に基づいて、単位電流駆動回路130別に、電流供給を行うか否かを設定するための駆動制御信号を生成する駆動制御信号生成回路と、を備える。

(もっと読む)

1 - 20 / 55

[ Back to top ]