Fターム[5J043AA25]の内容

Fターム[5J043AA25]の下位に属するFターム

Fターム[5J043AA25]に分類される特許

1 - 20 / 87

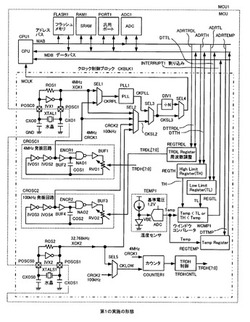

発振回路を有するマイクロコントローラ

【課題】複雑なバイアス回路を使用せず,抵抗の温度依存性を補償可能なMCU搭載に適したCR発振回路またはLC発振回路を提供する。

【解決手段】マイクロコントローラは,CPUと,CPUに供給するクロックを生成しクロックの周波数が周波数調整信号に応じて可変制御される発振回路と,温度を検知する温度センサと,温度センサにより検知される温度が所定温度変動したことに応答してCPUにより実行される周波数調整プログラムと,周波数調整信号と発振回路の発振周波数との関係を示す調整信号対周波数関係データと,温度と前記発振回路の発振周波数との関係を示す温度対周波数関係データとを格納するメモリとを有する。そして,周波数調整プログラムがCPUにより実行されることで,CPUが,温度対周波数関係データと調整信号対周波数関係データとに基づいて,温度センサにより検知される現在温度に応じて,発振回路の発振周波数を目標の周波数に制御する周波数調整信号を演算し,演算した周波数調整信号が発振回路に設定される。

(もっと読む)

リングオシュレータ回路、A/D変換回路、および固体撮像装置

【課題】偶数個(段)の反転回路をリング状に連結した構成でも、安定した発振動作を行うリングオシュレータ回路、これを用いたA/D変換回路、およびこれを用いた固体撮像装置を提供する。

【解決手段】反転回路が偶数個リング状に連結された円周上でパルス信号を周回させるリングオシュレータ回路であって、反転回路の内の一つが、制御信号に応じて第1のパルス信号を駆動する第1の起動用反転回路であり、他の一つが、第1のパルス信号の先頭エッジに基づいて第2のパルス信号を駆動する第2の起動用反転回路であり、さらに他の一つが、第2のパルス信号を駆動後の第1のパルス信号の先頭エッジに基づいて第3のパルス信号を駆動する第3の起動用反転回路であり、第1〜第3のパルス信号が円周上に同時に存在するとき、パルス信号の進行方向に対して第3、第2、第1の順になるように、第1〜第3の起動用反転回路を反転回路の円周内に配置する。

(もっと読む)

記憶回路

【課題】短時間の電源停止により消費電力を抑えることができ、電源再開時において誤動作を引き起こすことなく初期化することのできる信号処理装置の記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性記憶部に記憶していたデータ信号を、不揮発性記憶部に保持する。不揮発性記憶部では、オフ電流が極めて小さいトランジスタを用いることによって、容量素子に保持されたデータ信号は長期間にわたり保持する。こうして、不揮発性記憶部は電源の供給が停止した間も論理状態を保持する。また電源停止時に容量素子で保持されたデータ信号は、電源再開時にはリセット回路を導通状態とすることで、誤動作を引き起こすことのない電位にする。

(もっと読む)

発振回路及び発振回路を搭載した電子機器

【課題】本発明の目的は、水晶発振回路の駆動電流が100nA以下と非常に小さくなり、水晶発振回路の出力が0.1Vpp以下と小さくなっても、水晶発振回路の出力に接続する次段の種々の回路が正常に動作する出力信号を出発振回路、及びそれを搭載した電子機器を提供する。

【解決手段】水晶発振回路の出力を増幅する増幅回路を水晶発振回路の出力側に接続し、水晶発振回路の出力電圧と水晶発振回路のCMOSインバータの入力電圧との差を増幅させる。たとえば、差動アンプを水晶発振回路の出力側に接続し、水晶発振回路の出力電圧とCMOSインバータの入力電圧とを差動アンプの入力とする。あるいは、3つのオペアンプから構成されるインスツルメンテーションアンプを水晶発振回路の出力側に接続し、水晶発振回路の出力電圧信号と水晶発振回路のCMOSインバータの入力電圧信号との差を増幅させる。

(もっと読む)

電子回路

【課題】発振回路部の信号反転素子及びインターフェース回路部のインターフェース回路部のインターフェース集積回路素子で消費される電流を抑えて消費電力が少ない電子回路を提供する。

【解決手段】発振回路部とインターフェース回路部と被駆動回路部と備えた電子回路であって、発振回路部用電源電圧印加端子と発振回路部の間に発振回路部用電流制限抵抗が設けられ、インターフェース回路部用電源電圧印加端子とインターフェース回路部との間にインターフェース回路部用電流制限抵抗が設けられ、発振回路部用電流制限抵抗の両端部からグランドに接続されている第一のコンデンサが設けられ、インターフェース回路部用電流制限抵抗の両端部からグランドに接続されている第二のコンデンサが設けられ、インターフェース回路部から出力され被駆動回路部に入力される信号電圧が被駆動回路部が動作するために必要な電圧より大きいことを特徴とする。

(もっと読む)

演算およびスリープ・モード中のデータ格納回路並びに方法

【課題】スリープ・モード中に信号を格納するための回路を提供する。

【解決手段】スリープ信号を受け取るスリープ信号入力と、クロック信号を受け取るクロック信号入力と、クロック信号でクロックされる複数のラッチと、クロック信号でクロックされるトライステート素子であって、トライステート素子は1つの入力に、少なくとも1つの格納ラッチが接続され、格納ラッチは複数のラッチの1つであり、トライステート素子は格納ラッチの入力を、予め定められたクロック信号値に応答して選択的に分離するトライステート素子とを含み、回路への電源供給が、スリープ信号に応答して、回路の少なくとも1部の電圧差が低減されて回路の部分の電源が遮断され、格納ラッチに掛かる電圧差が維持され、トライステート素子で受け取られるクロック信号が予め定められた値に保持されて、格納ラッチの入力が分離される。

(もっと読む)

発振器及び半導体集積回路装置

【課題】発振器の出力端子間に直接寄生する容量Cparaの大きさが無視できない場合でも温度特性を補償する発振器及び発振器を内蔵する半導体集積回路装置を提供する。

【解決手段】インダクタンス素子Lと、容量素子Cと、増幅器30と、をそれぞれ第1の端子と第2の端子との間に並列に接続し、インダクタンス素子と容量素子とによって生じる共振を増幅器によって増幅し、第1の端子と第2の端子とから出力する発振器であって、第1の端子と第2の端子との間にインダクタンス素子の寄生抵抗RLより抵抗値の大きな第1の抵抗素子Rcが第1の端子と第2の端子との間に容量素子と直列に接続されている。

(もっと読む)

ディレイラッチ回路、および、ディレイフリップフロップ

【課題】Dラッチ回路またはDフリップフロップの消費電力の増大を抑制しつつ、低電圧におけるDラッチ回路またはDフリップフロップの誤動作を防止する。

【解決手段】内部信号出力回路320は、内部透過開始タイミングから内部透過終了タイミングまでの間においてはデータ信号を反転した信号を内部信号として出力する。内部信号出力回路320は、内部透過終了タイミングから内部透過開始タイミングまでの間においては所定値に値を固定した信号を内部信号として出力する。nMOSトランジスタ330は、保持指示遅延タイミングからデータの透過が指示されるまでの間に内部透過終了タイミングが含まれるように前記出力された内部信号を遅延させる。

(もっと読む)

半導体装置

【課題】記憶された複数のビットの内の偶数個のビットに同時にエラーを生じることを防止する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置は、マスタラッチ回路11と、マスタラッチ回路11からデータ信号を入力して保持するスレーブラッチ回路12とを有するマスタスレーブ型フリップフロップ回路(MS型FF回路)10aと、マスタラッチ回路11と、マスタラッチ回路11からデータ信号を入力して保持するスレーブラッチ回路12とを有し、MS型FF回路10aと並んで配置されるMS型FF回路10bとを備え、MS型FF回路10aのマスタラッチ回路11の隣には、MS型FF回路10bのスレーブラッチ回路12が配置され、MS型FF回路10aのスレーブラッチ回路12の隣にはMS型FF回路10bのマスタラッチ回路12が配置される。

(もっと読む)

リング発振器

【課題】LSI等の半導体集積回路に組み込まれたリング発振器は、専用の電源スイッチを有しているわけではないので、それを構成するMOSトランジスタには非発振時中も通電され続けるものがある。そのため、特性が劣化し、リング発振器の発振周期が次第に増大していた。

【解決手段】MOSトランジスタで構成され反転ゲートとして機能する奇数個のNAND回路を、その出力端子と他のNAND回路の第1の入力端子とを接続するというように順次接続し、全体としてリング状とする。発振出力は、任意の1つのNAND回路の出力端子から取り出す。そして、発振または非発振を制御する信号を入力する発振制御入力端子20を、各NAND回路の第2の入力端子と接続する。

(もっと読む)

半導体装置

【課題】 データ保持回路を備えた半導体装置において、回路面積の低減及び動作速度の向上を図ること。

【解決手段】 本半導体装置100は、少なくとも1以上の不揮発性のメモリセルFCと、メモリセルFCへの書き込みデータ又はメモリセルFCからの読み出しデータを格納するラッチ回路30とを含み、メモリセルFC及びラッチ回路30がアレイ状に配置された複数の不揮発性メモリ回路20と、複数の不揮発性メモリ回路20におけるラッチ回路30のそれぞれに接続され、データを一時的に保持する複数のデータ保持回路10と、を備える。

(もっと読む)

乱数生成回路

【課題】回路動作開始直後の初回サンプリングにおいてもランダム性の高い真性乱数を生成することのできる乱数生成回路を提供する。

【解決手段】奇数段の論理ゲートで構成されたM1個の第1のリングオシレータ10−1と、偶数段のインバータと1段の論理ゲートで構成されたM2個の第2のリングオシレータ10−2と、第1のリングオシレータ10−1の中間ノード出力と第2のリングオシレータ10−2の中間ノード出力の排他的論理和をとる(M1+M2)入力XOR21と、出力をサンプリングクロックでラッチし、乱数値として出力するD−FF22と、サンプリングクロックを生成する制御部100とを備え、第1のリングオシレータ10−1を構成する各論理ゲートの出力にそれぞれインバータが接続され、インバータのいずれか1つの出力をリングオシレータの中間ノード出力とする。

(もっと読む)

クロック発振回路及び半導体装置

【課題】起動時にTDCにキャリブレーション処理を加えることで、時間分解能のばらつきが発生することを防ぎ、合わせて、遅延用の素子の冗長度を減らすことで回路規模の増大を防ぐ手段を提供する。

【解決手段】電源投入時等に多相発振器型TDCであるPDC_c及びバーニア型TDCであるPDC_fのキャリブレーションを実行する。キャリブレーション時にはPDC_fに入力するタイミング入力を参照クロックCLK_REFからDCCOの出力信号のうち一つを選択する。またデータは、先のDCCOの出力信号に隣接し、位相が進んだ出力信号とし、その間の遅延を導出する。これを全出力信号繰り返すことで、DCCOの出力信号1周期を導出する。

(もっと読む)

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

半導体集積回路

【課題】 半導体集積回路において、ソフトエラーによるデータの破壊を抑制しつつ、回路面積の低減を図ること。

【解決手段】 本半導体集積回路は、第1入力端子Dからの入力信号を保持する第1データ保持回路30と、第1入力端子D及び第2入力端子SQからの入力信号を保持する第2データ保持回路40と、第1データ保持回路30からの出力信号及び第2データ保持回路40からの出力信号が入力され、第1データ保持回路30からの出力信号と第2データ保持回路40からの出力信号とが同じ場合に、当該出力信号に対応した信号を出力するゲート回路50と、ゲート回路50及び第2データ保持回路40のいずれかの出力信号を保持し、出力端子に出力する第3データ保持回路60と、を備える。

(もっと読む)

水晶発振器

【課題】水晶発振器の出力振幅の調整機能を簡易な構成で実現する。

【解決手段】水晶発振器は、電源に接続される電源端子(VCC)と、接地電位に維持される接地端子(GND)と、電源端子と接地端子とに接続され、電源端子と接地端子との間に印加された電源電圧に基づく振幅レベルの発振信号(V0)を出力する水晶発振回路(6)と、イネーブル信号(VEN1、VEN2)が入力されるイネーブル端子(EN1、EN2)と、イネーブル端子と接地端子とに接続され、水晶発振回路から入力される発振信号を波形整形してイネーブル端子と接地端子との間のイネーブル信号の電圧に応じた振幅レベルの基準クロック信号(CLK1、CLK2)を出力するバッファ回路(2a、2b)と、バッファ回路から出力される基準クロック信号が出力される出力端子(OUT1、OUT2)と、を備える。

(もっと読む)

半導体集積回路

【課題】回路規模及び消費電流を増加させることなく、且つ、単純な回路を用いて、出力信号の雑音成分を低減する。

【解決手段】半導体集積回路は、リング発振器10と、ノイズキャンセラ20と、を備える。リング発振器10は、入力信号Vinに基づいて、第1位相を有する第1出力信号Vout1を生成する第1信号生成部12と、入力信号Vinに基づいて、第1位相とは異なる第2位相を有する第2出力信号Vout2を生成する第2信号生成部13と、を備える。ノイズキャンセラ20は、第1増幅係数K1を用いて第1信号生成部12により生成された第1出力信号Vout1を増幅する第1増幅器21と、第2増幅係数K2を用いて第2信号生成部13により生成された第2出力信号Vout2を増幅する第2増幅器22と、第1増幅器21により増幅された第1出力信号Vout1と第2増幅器22により増幅された第2出力信号Vout2とを合成する演算器24と、を備える。

(もっと読む)

極低電圧発振回路及びそれを用いた極低電圧DCDC変換装置

【課題】太陽電池や燃料電池は単一セルでは出力電圧が0.2Vから0.6Vと非常に低くその電圧を昇圧してエネルギーを2次電池に蓄積する場合、昇圧回路が0.2V程度からの極低電圧領域から昇圧動作を開始する必要がある。

【解決手段】FETのサブスレシュオールド領域を利用して極低電圧から発振を開始するとともに周囲温度の変化に対しても安定な周波数を発生する補正機構を組み込むことにより確実に起動しかつ正確にDCDC変換装置を実現する。

(もっと読む)

パルス発生回路

【課題】極めて短いパルス幅のパルス電圧を発生するパルス発生回路を提供する。

【解決手段】パルス発生回路は、誘導エネルギーを蓄積するトランスと、トランスへの直流の供給経路と、供給経路を開閉するスイッチと、トランスの第1端と第2端とを自律的に短絡に近い状態にする補助回路と、トランスからのパルス電圧の出力経路と、直流を供給する直流電源と、直流電源からの直流の供給を安定させるキャパシタと、を備える。補助回路は、トランスに誘導起電力が発生してから短い時間が経過した後に第1端と第2端とを自律的に短絡に近い状態にする。補助回路は、短絡経路を流れる電流を直流電源へ回生する回生回路を備える。

(もっと読む)

不揮発性のラッチ回路及び論理回路及びそれを用いた半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構造を有するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半導体を用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソース電極又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータを保持することができる。これにより不揮発性のラッチ回路を構成することができる。

(もっと読む)

1 - 20 / 87

[ Back to top ]