Fターム[5J043AA26]の内容

Fターム[5J043AA26]に分類される特許

1 - 20 / 113

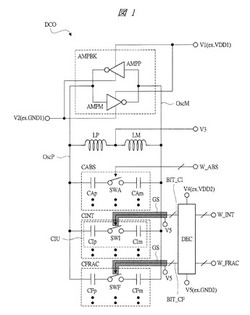

ディジタル制御発振装置および高周波信号処理装置

【課題】DNLの低減を実現可能なディジタル制御発振装置を提供する。

【解決手段】例えば、発振出力ノードOscP,OscM間に並列に結合されるアンプ回路ブロックAMPBK、コイル素子LP,LM、複数の単位容量ユニットCIU等を備え、各CIUは、容量素子CIp,CImと、当該CIp,CImを発振周波数の設定パラメータとして寄与させるか否かを選択するスイッチSWIを備える。ここで、SWIは、デコーダ回路DECからのオン・オフ制御線BIT_CIによって駆動され、当該BIT_CIは、シールド部GSによってOscP,OscMとの間でシールドされる。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に搭載されたデジタル制御発振装置が生成するクロック信号の品質を向上させる。

【解決手段】ICチップは周辺部を除く部位に位置する回路形成部位が、パルス遅延回路10からなる第1回路ブロック3と、時間/数値変換回路20及びデータ処理部30,デジタル制御発振回路40からなる第2回路ブロック5と、第1回路ブロック3及び第2回路ブロック5により形成されるデジタル制御発振装置1にて生成されたクロック信号CKOを利用した各種処理を実行するための周辺回路等からなる第3回路ブロック7とからなる。また、第1回路ブロック3は、電源パッドP1及び電源ラインL1を介して供給される第1の電源VDD1により駆動され、第2回路ブロック5及び第3回路ブロック7は、電源パッドP2及び電源ラインL2を介して供給される第2の電源VDD2により駆動されるように、レイアウトされている。

(もっと読む)

シュミットインバータ回路及び半導体装置

【課題】チャタリング抑制の特性を維持したまま、電源電圧や温度の影響による出力周波数の変化を抑制する。

【解決手段】スイッチSWH及びSWLがオフ状態で、入力信号がVthLより大きくVDD/2未満の場合、第1インバータ12の閾値電圧はVDD/2となり、出力信号OUTはハイレベルとなる。入力信号がVDD/2〜VthHとなると、出力信号OUTが立ち下がり、制御信号CSLが立ち上がって、スイッチSWLがオンされ、閾値電圧は低電位側に変化する。入力信号がVthHを超えると、信号SLHが立ち下り、入力信号が再びVthH未満となると、信号SLHが立ち上がり、制御信号CSLが立ち下がって、スイッチSWLがオフされ、閾値電圧は再びVDD/2に変化する。入力信号がVDD/2〜VthLとなると、出力信号OUTが立ち上がり、制御信号CSHが立ち上がって、スイッチSWHがオンされ、閾値電圧は高電位側に変化する。

(もっと読む)

弛張発振回路

【課題】従来技術に比較して周波数が一定のクロックを発生できる弛張発振回路を提供する。

【解決手段】クロック発生サブ回路1は、基準電圧Vrefとコンパレータ14の誤差電圧ΔV1とを含む比較電圧Vcmp1を発生して出力電圧Vsub1としてコンパレータ14の反転入力端子に出力する比較電圧発生期間と、電流電圧変換回路11からの出力電圧Vc1を比較電圧Vcmp1と比較するクロック発生期間とを交互で繰り返すように制御される。クロック発生サブ回路2も、クロック発生サブ回路1と同様のクロック発生期間とを交互で繰り返すように制御される。制御回路5は、クロック発生サブ回路1及び2を、一方の回路が比較電圧発生期間であるときに他方の回路がクロック発生期間であるように制御する。

(もっと読む)

発振回路

【課題】電流源、比較回路および外付け容量で構成される従来技術による発振回路では、外付け容量の容量値によって発振周波数の精度が悪くなる問題があった。外付け容量の放電時間は、その容量値と、電荷を引き抜く抵抗成分の時定数とで決定される。そのため、容量値が大きい場合は放電時間が長くなり、放電時間に合わせて遅延時間を長く設定する必要があった。逆に、容量値が小さい場合は、発振周波数の周期に対して遅延時間が相対的に大きくなるので、やはり発振周波数の精度が悪くなる。

【解決手段】発振回路に2つの外付け容量を設け、充電および放電を交互に行うことで、発振周波数の精度が外付け容量に溜まった電荷の放電時間に影響されない。すなわち、発振周波数の精度は外付け容量の容量値よって変わることが無い。

(もっと読む)

抵抗周波数変換回路及び電子機器

【課題】製造バラツキによる影響の少ない発振回路を有した抵抗周波数変換回路を提供する。

【解決手段】抵抗周波数変換回路が、第1のノードと第2のノードとの間に接続された第1のキャパシターと、前記第2のノードと第3のノードとの間に接続され、前記第2のノードにおける信号を反転出力する第1の反転ゲートと、前記第3のノードと前記第1のノードとの間に接続される第1の抵抗と、前記第1のノードと第4のノードとの間に接続される第2の抵抗と、前記第4のノードにおける信号を増幅して前記第2のノードに出力することができる第1の回路と、を含む。

(もっと読む)

発振器

【課題】簡単な構成で高速立ち上げが可能であり、さらに従来のリング型電圧制御発振器に比べて安定な周波数の信号を生成することができる発振器を提供する。

【解決手段】制御電圧入力端子に印加された制御電圧に従って発振周波数が変化するリング型電圧制御発振器10と、リング型電圧制御発振器10の出力信号を一定時間幅のパルス信号に変換して出力するパルス整形回路20と、参照電圧からパルス整形回路20が出力する周波数が変化するパルス信号の平均電圧を差し引いた電圧を積分してリング型電圧制御発振器10の制御電圧入力端子に出力する積分回路30とを備える。

(もっと読む)

発振装置、半導体装置、電子機器、時計、及び、振動子発振回路

【課題】発振装置において、発振安定化容量として用意されたキャパシタを有効活用する。

【解決手段】発振装置は、定電圧を生成する定電圧生成回路と、振動子発振回路と、第1のキャパシタを備える。振動子発振回路は、振動子を発振させるための回路であって、振動子の一端に接続される第1の接続ノードと、定電圧生成回路により生成された定電圧が供給される定電圧供給ノードと、を有する。第1のキャパシタは、第1の接続ノードと定電圧供給ノードのいずれかに選択的に接続される。

(もっと読む)

発振周波数補正装置

【課題】同期信号の検出が困難なときにも正確な発振周波数のクロック信号を生成できるようにした発振周波数補正装置を提供する。

【解決手段】電源投入時の劣化検出タイミングにおいて、定電流源23から抵抗器22に通電して得られたA/D変換器6のAD変換値(抵抗器22の端子電圧VR)に基づいて、CPU2が逓倍数設定値FMULRを補正する。この場合、定電流源20を用いることなく定電流源23が作動して抵抗器22に通電する。CPU2は、抵抗器22の端子電圧を測定することでCR発振器14内の抵抗器R1の抵抗値の経年変化を反映し、この変化に基づいてCR発振回路8のクロック信号CLKの逓倍数設定値FMULRを補正する。

(もっと読む)

発振器及び発振器を有する半導体装置

【課題】インバータとの接続点であるノードの最高電圧及び最低電圧が最適な電圧になるようにし、各ノードの信号の電圧の変化によって生じるクロック信号の周波数のずれを抑えることのできる発振器を提供する。

【解決手段】複数のインバータI1,I2のうちのインバータI1の接続点であるノードN1の信号S1の最高電圧及び最低電圧が、2つの容量素子C1,C2の容量値c1,c2と抵抗素子R1の抵抗値r1とによって任意の電圧になるようにする。これにより、信号S1の最高電圧及び最低電圧を、本来の最高電圧又は最低電圧にすることができ、ノードN1の信号S1の電圧v1の変化によって生じるクロック信号SOUTの周波数TOのずれを抑えることができる。

(もっと読む)

VCO回路

【課題】 位相雑音の発生や発振周波数のずれを抑制することのできるVCO回路を提供する。

【解決手段】 実施形態のVCO回路は、3個のインバータIV1〜IV3をリング状に接続したリングオシレータ1を備え、制御電流生成部2が、入力された制御電圧Vctを電圧−電流変換した制御電流Ictを生成し、リングオシレータ1へ電源電流として供給する。また、このVCO回路では、定電流生成部3が、定電流Iaを生成し、制御電流Ictに重畳する電源電流としてリングオシレータ1へ供給する。

(もっと読む)

診断回路、発振回路

【課題】リファレンスクロックを要することなく発振信号の周波数範囲を診断できる、回路規模の小さな診断回路等を提供する。

【解決手段】制御信号102に応じて周波数が変化する発振信号166の周波数範囲を診断する診断回路10であって、制御信号102を受け取り、制御信号102に基づく値である比較値と所定の限界値とを比較する比較器を含み、比較器が比較した結果に基づいて診断出力値100を生成する。所定の限界値として上限値と下限値とを定め、比較値と上限値とを比較する上限比較器と、比較値と下限値とを比較する下限比較器とを含み、上限比較器および下限比較器が比較した結果に基づいて、診断出力値100を生成する。

(もっと読む)

半導体装置

【課題】広範囲、光分解能に周波数を可変することのできるクロック信号を生成する。

【解決手段】オペアンプAMP1は、正入力部と負入力部が等しい電圧となるようフィードバックがかかり、回路ノードfbckは、参照電圧VREFIに等しい電圧となる。デコーダDECは、制御信号CNT7,CNT6をデコードし、トランジスタT2〜T5のいずれか1つをオンさせる。この構成によって、回路ノードfbckが、参照電圧VREFIと同電位となるようフィードバック制御がかかるため、トランジスタT2〜T5のON抵抗を大幅に低減することができ、周波数精度の悪化を防止することができる。

(もっと読む)

巨大磁気抵抗効果接合部を有する発振回路

【課題】巨大磁気抵抗効果接合部を有する発振回路を提供する。

【解決手段】巨大磁気抵抗効果を有する接合部を基盤とした発振器。発振器は電流が横断する巨大磁気抵抗効果を有するn個(nは、1以上の整数)の基本接合部のグループを2つ備え、2つのグループ各々における接合部は直列接続され、かつそれぞれの主電流(I0)によってエネルギーを得、両グループの端子の両端間の電圧が加算されることにより発振回路の出力Sにおいて電圧を供給する。第1のグループの1個以上の接合部の端子の両端間の電圧は位相比較器PHCの第1の入力E1に印加され、他方のグループの1個以上の接合部の端子の両端間の電圧は位相比較器の別の入力E2に印加される。位相比較器は2つの出力S1、S2において、入力に印加された電圧間の平均位相差によって決まる同じ振幅で逆符号の二次電流+i、−iを供給する。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

大きな温度変動に対する発信周波数の安定化方法

【課題】

超高温から極低温までの温度変動が極めて大きい環境に設置される無線機器に適用できる発信周波数の安定化方法を提供する。

【解決手段】

複数の発信回路を備え、筐体内の温度を測定する筐体内温度測定ステップと、測定した筐体内温度Tと予め定められた温度T0、T1、・、Tk、・Tnとの大小関係から測定した温度範囲を判定する温度範囲判定ステップと、 温度範囲判定ステップが判定した温度範囲に応じて複数の発信回路のいずれかを選択する回路選択ステップとを有し、筐体内温度TがTk−1≦T<Tkの範囲であった場合に、回路選択ステップは当該温度範囲において、発信器の発信周波数が希望の範囲に納まるように予め調整されている発信回路等を選択する。

(もっと読む)

半導体装置

【課題】クロック周波数の設定を変えた場合でも電源や温度などに変動があっても、高精度なクロック信号を生成する。

【解決手段】周波数電圧変換回路13は、スイッチSW1,SW2から構成されるスイッチ部、静電容量素子C,C10〜C13、およびスイッチCSW0〜CSW3から構成されている。静電容量素子C10〜C13は、容量の絶対値が異なるもので構成され、設計者が意図する周波数範囲をカバーするよう設ける。静電容量値は、たとえば、2の重み付けがされている静電容量素子C11〜C13は、たとえば、4ビットの周波数調整制御信号SELC0〜SELC3に基づいて、スイッチCSW0〜CSW3が選択し、周波数の切り替えを行う。

(もっと読む)

クロック発生装置

【課題】広い温度範囲で高精度なクロック信号を出力可能な、安価でかつコンパクトなサイズのクロック発生装置を提供する。

【解決手段】クロック発生装置は、基準クロック信号を生成する基準クロック生成部11と、第1のクロック信号を生成する第1の発振器12と、前記第1のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第2のクロック信号を生成する第1の精度保証部13と、温度検知部15と、第3のクロック信号を生成する第2の発振器17と、前記第3のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第4のクロック信号を生成する第2の精度保証部18と、温度が第1の発振器12の保証温度範囲内の場合には前記第2のクロック信号、保証温度範囲外の場合には前記第4のクロック信号を出力するクロック切替部20と備える。

(もっと読む)

局部発振器

【課題】PVTに依存しない安定した位相雑音特性を短時間で得ることができる局部発振器を提供する。

【解決手段】局部発振器は、デジタル制御発振器と、位相データ生成器と、減算器と、ループフィルタと、乗算器と、係数算出器と、を備える。前記デジタル制御発振器は、第1の発振器制御値により発振信号の発振周波数を制御可能である。前記発振周波数は、前記第1の発振器制御値と、前記第1の発振器制御値の単位値あたりの前記発振周波数の変化量と、の積に等しい。設定周波数データは、設定周波数を基準信号の基準周波数で除算して得られる。前記乗算器は、前記ループフィルタからの規格化制御値に第1の係数を乗算した前記第1の発振器制御値を出力する。前記係数算出器は、前記発振周波数が前記設定周波数に略等しくなった時の前記第1の発振器制御値を、前記設定周波数データで除算し、その除算結果を新たな前記第1の係数として前記乗算器に設定する。

(もっと読む)

スケルチ回路

【課題】消費電流を低減しつつ、回路面積の縮小を図ることが可能なスケルチ回路を提供する。

【解決手段】差動入力される差動入力信号と閾値とを比較して、スケルチ信号を出力するスケルチ回路は、差動入力信号が入力され、前記差動入力信号と前記閾値とを比較して得られた第1のデジタル信号を出力する第1のコンパレータ回路を有する。また、デジタル回路で構成され、前記第1のコンパレータ回路の出力を平滑化し前記スケルチ信号として出力するデジタル平滑化回路を有する。また、第1のコンパレータ回路は、第1のクロック信号により動作が制御され、前記差動入力信号と前記閾値とを比較して得られた第1の差動比較信号を出力する第1のクロックト・コンパレータと第1の差動比較信号が入力され、前記第1の差動比較信号の論理を保持して前記第1のデジタル信号として出力する第1のデータ保持回路を有する。

(もっと読む)

1 - 20 / 113

[ Back to top ]