Fターム[5J050BB21]の内容

電子的スイッチ (6,662) | スイッチの種類、機能 (1,020) | 光電リレー、フォトカプラ (95)

Fターム[5J050BB21]に分類される特許

1 - 20 / 95

駆動回路、及び、光送信装置

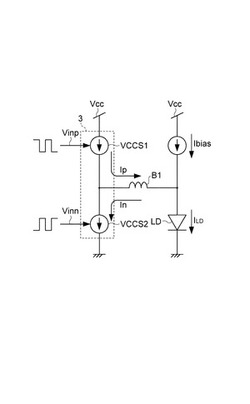

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子に接続されている逆相信号処理回路と、アノードが接続されている端子に接続されている第1及び第2の電圧制御電流源回路を備える。第1の電圧制御電流源回路には、正相信号Vinpに対応する電圧及び逆相信号Vinnの逆相に対応する電圧が入力され、第2の電圧制御電流源回路には、逆相信号Vinnに対応する電圧及び正相信号Vinpの逆相に対応する電圧が入力される。

(もっと読む)

半導体リレー装置

【課題】半導体リレー装置において、特殊なプロセスを用いることなく、充放電回路全体の耐圧を向上させることを可能にして、低コストで出力用MOSFETの低オン抵抗化を図る。

【解決手段】出力用MOSFET5のゲート・ソース間に配された複数の充放電回路7a、7bを直列に接続し、これらの充放電回路7a、7bの各々に、2つのフォトダイオードアレイ3a、3bの各々を並列に接続した。この構成においては、各フォトダイオードアレイ3a、3bの光起電力に相当する電圧が、そのフォトダイオードアレイに並列に接続された充放電回路(7a又は7b)内のMOSFET(8a又は8b)のみにかかり、それ以外の充放電回路内のMOSFETにはかからない。従って、2つの充放電回路7a、7bの全体の耐圧を、これらの充放電回路7a、7bに含まれる、複数のMOSFET8a、8bの耐圧の合計にすることができる。

(もっと読む)

半導体リレー

【課題】半導体リレーにおいて、LEDの駆動電力の低減を図る。

【解決手段】半導体リレー1は、LED2を駆動回路3により駆動して発光させ、LED2から発光された光を受光部4により受光する。駆動回路3は、バイポーラトランジスタ31と、コイル32と、ダイオード33等を有する。バイポーラトランジスタ31は、導通状態と非導通状態とに切換えられ、導通状態のときに、電源からLED2に電流が供給される状態にし、非導通状態のときに、電源からLED2に電流が供給されない状態にする。コイル32は、LED2に直列に接続されており、バイポーラトランジスタ31が導通状態から非導通状態になったときに、自己誘導作用によって誘導起電力を発生する。ダイオード33は、LED2及びコイル32に並列に接続されており、バイポーラトランジスタ31が非導通状態のときに、コイル32が発生する誘導起電力によって、LED2に電流を還流させる。

(もっと読む)

半導体スイッチ

【課題】半導体スイッチにおいて、エネルギー効率を高くする。

【解決手段】半導体スイッチ1は、LED2を駆動回路3により駆動して発光させ、LED2から発光された光を受光部4により受光する。駆動回路3は、バイポーラトランジスタ31と、コイル32と、ダイオード33等を有する。バイポーラトランジスタ31は、導通状態と非導通状態とに切換えられ、導通状態のときに、電源からLED2に電流が供給される状態にし、非導通状態のときに、電源からLED2に電流が供給されない状態にする。コイル32は、LED2に直列に接続されており、バイポーラトランジスタ31が導通状態から非導通状態になったときに、自己誘導作用によって誘導起電力を発生する。ダイオード33は、LED2及びコイル32に並列に接続されており、バイポーラトランジスタ31が非導通状態のときに、コイル32が発生する誘導起電力によって、LED2に電流を還流させる。

(もっと読む)

ソリッドステートリレー及び負荷駆動回路

【課題】簡単かつ安価な構成であるにも拘わらず、スナバ回路及び制御回路のいずれの損傷に対しても、他の電子部品の焼損を適切に防止する。

【解決手段】入力端子の間に接続される発光素子8からの光を光電変換する受光素子9と、交流電源3と負荷4とが接続される出力端子6と、受光素子9の一端と出力端子6の一方とを結ぶ第1接続ライン11と、受光素子9の他端と出力端子6の他方とを結ぶ第2接続ライン12と、第1接続ライン11と第2接続ライン12の間に接続される、受光素子9からの出力に基づいて導通するスイッチング素子12と、コンデンサと抵抗とを直列接続してなるスナバ回路14とを備える。スナバ回路14の抵抗は、第1接続ライン11の、受光素子9の一端と、スイッチング素子12の一端との間に接続し、抵抗とスイッチング素子12の一端との間に過電流防護素子21を接続する。

(もっと読む)

半導体リレー装置

【課題】半導体リレー装置において、リレーとしてのオン/オフ動作の時間を安定させ、しかも、このオン/オフ動作の速度を、従来よりも速くする。

【解決手段】出力用MOSFET5、6のソースと誘電体分離チップの10の支持基板14とを電気的に接続したことにより、誘電体分離チップ10の支持基板14の電位を、出力用MOSFET5、6のソースの電位に固定することができる。これにより、活性領域・支持基板間容量CPCに貯めることが可能な電荷の量の安定化を図れ、しかも、この容量CPCの電気的な接続先が固定される。従って、リレーとしてのオン/オフ動作の時間を安定させることができる。また、従来と異なり、上記容量CPCの全てが、出力用MOSFET5、6のゲート・ソース間に並列に配置されて寄生容量として働くことがなくなるので、リレーとしてのオン/オフ動作の時間を、従来よりも速くすることが可能になる。

(もっと読む)

半導体リレー装置

【課題】半導体リレー装置において、装置全体のチップサイズを小さくして、チップコストの低減と実装面積の縮小化を図る。

【解決手段】従来はp型単結晶シリコン島213に形成していた(充放電回路における)pチャネル型のMOSFET208(図(a)参照)を、n型単結晶シリコン島13に形成したnチャネル型のMOSFET8(図(b)参照)に変更した。これにより、n型単結晶シリコン島13のキャリアの通路の断面積を、p型単結晶シリコン島213のキャリアの通路の断面積の2分の1以下にしても、これらのキャリアの通路における抵抗値を同じにすることができる。従って、MOSFET8をn型単結晶シリコン島13にnチャネル型で形成することにより、オン抵抗を従来のMOSFET208に比べて大きくすることなく、MOSFET8のゲート幅W3を従来のMOSFET208のゲート幅W1より小さくできる。

(もっと読む)

絶縁回路の健全性確認装置

【課題】絶縁回路の発光素子の発光量を測定することなく、絶縁回路の健全性を確認することができる絶縁回路の健全性確認装置を提供する。

【解決手段】絶縁回路1に対する入力信号がオン状態のときに光を発するように設けられた発光素子1aに対し、入力信号がオフ状態のときに所定の周期で電流が流れるように制御する電流制御器11と、所定の周期T1で発光素子1aに電流が流れている際に、発光素子1aが発する光を受けた際に導通するように設けられた受光素子1bが所定の周期T1以上継続してオフ状態となる場合を発光素子1aの異常として検出する検出器18と、を備えた。

(もっと読む)

半導体リレー及び測定装置

【課題】理想的な高耐圧、低オン抵抗且つ低オフ容量の半導体リレーを提供する。

【解決手段】入力素子に発光ダイオード11を備えるとともに出力素子に二つのトランジスタ12,13を備える半導体リレー10であって、前記二つのトランジスタが、相違する耐電圧及び/又は相違する電気容量を有する。また、一方の前記トランジスタ12が、他方の前記トランジスタ13より、高耐電圧及び/高電気容量である。

(もっと読む)

接点入力回路

【課題】閾値電圧設定回路の抵抗器の開放故障に対するフェールセーフ性を確保し、且つ、検査信号がオフ制御されたときの消費電力を低減できる接点入力回路の実現。

【解決手段】接点入力回路10は、接点の開閉状態を示す入力信号が入力される正入力端子11と負入力端子12との間に、第1抵抗器R1、第3抵抗器R3及び第4抵抗器R4が直列接続されている。そして、直列接続された第3抵抗器R3及び第4抵抗器R4に対して、第2抵抗器R2、第1フォトカプラP1のフォトダイオードPd1及び第2フォトカプラP2のフォトトランジスタPt2が順方向に直列接続されてなる第2回路部16が並列接続されている。また、第4抵抗器R4に対して、第2フォトカプラP2のフォトダイオードPd2及び第3フォトカプラP3のフォトトランジスタPt3が順方向に直列接続されてなる第1回路部15が並列接続されている。

(もっと読む)

半導体装置及びそれを備えた半導体リレー装置

【課題】半導体装置及び半導体リレー装置において、製造コストを抑えつつ、CR積の値を小さくする。

【解決手段】双方向スイッチ1を構成する2つのMOSFETのうち、一方のMOSFET2に、化合物半導体で構成されたユニポーラ型化合物半導体装置を用い、他方のMOSFET3に、シリコンで構成されたSi−MOSFETを用いる。ここで、ユニポーラ型化合物半導体装置の中には、Si−MOSFETよりもCR積の値が小さいものが多く存在する。従って、一方のMOSFET2にユニポーラ型化合物半導体装置を用いたことにより、両方のMOSFET2、3にSi−MOSFETを用いた場合に比べて、装置全体のCR積の値を小さくできる蓋然性が高まる。また、Si−MOSFETよりも製造コストの高いユニポーラ型化合物半導体装置を2つ用いた場合に比べて、製造コストを抑えられる。

(もっと読む)

電流極性判別器付きスイッチ

【課題】ノイズによってインバータなどの出力電流の極性を誤って検出することなく、正確に検出する。

【解決手段】単方向の電流をスイッチングできるスイッチング素子と該スイッチング素子に逆並列に接続された還流ダイオードからなる逆導通スイッチと、直列に接続されたダイオードと抵抗とフォトカプラと直流電源で構成された電流極性判別器で、前記直流電源の電圧値を前記還流ダイオードに電流が流れた時のみ前記フォトカプラがオンするように設定し、該フォトカプラの出力を電流の極性判別とすることで電圧比較を行うことがなくノイズによる誤検知を防ぐことができる。

(もっと読む)

メモリカード切り替え装置

【課題】

メモリカードを使うデバイス側の回路に手を入れることなく、複数のメモリカードをデバイスに接続でき、それらを手動差し替えでなく電子的に切り替えることができるようにする。

【解決手段】

データバスおよび電源がメモリカード間で直結されており、クロックラインのみフォトMOSリレーで切り替え、排他的に一枚のみにクロックが共有されるようにするとともに、フォトMOSリレーの出力から2KΩ前後のダンピング抵抗と10KΩ前後のプルアップ抵抗を介してメモリカードへクロックを共有する。

(もっと読む)

信号出力装置及びロボットコントローラー

【課題】外部機器に応じてシンク型及びソース型の出力信号が出力可能であるとともに、出力信号の切替えに必要とされる構成部品の共通化を図ることの可能な信号出力装置及びロボットコントローラーを提供する。

【解決手段】出力電流をオンオフ制御するための制御信号が入力される制御端子23a,24aと、端子間の通電により一方の端子からシンク電流を出力する出力端子対であるシンク用出力端子28a及びシンク用共通端子28bと、端子間の通電により一方の端子からソース電流を出力する出力端子対であるソース用出力端子29b及びソース用共通端子29aと、一つの制御端子と一つの出力端子対との間に接続されて、該制御端子からの制御信号に基づき該出力端子対での通電をオンオフ制御するスイッチングデバイス15とを備え、制御端子23aに対する第1の出力端子対の相対位置と、制御端子24aに対する第2の出力端子対の相対位置とが互いに等しい。

(もっと読む)

データ処理装置

【課題】消費電力を抑えつつフォトカプラの耐用寿命を延ばすことができるデータ処理装置を提供すること。

【解決手段】フォトカプラの入出力データを処理するデータ処理装置は、フォトカプラの入力側と出力側の間で伝送されるデータを構成する所定ビットのパケットデータ群の過半数が「1」のビットか「0」のビットかを判断する過半数ビット判断部と、「1」のビットが過半数を占めると判断されたパケットデータ群を構成する各ビットの値を反転する入力信号処理部と、過半数ビット判断部が判断した結果に応じた制御情報を、過半数を「0」のビットが占めるパケットデータ群又は各ビットの値が反転されたパケットデータ群に付加して、フォトカプラに出力する制御情報付加部と、フォトカプラの受光部で得られた制御情報に応じて、受光部が受信したパケットデータ群を構成する各ビットの値を反転し、制御情報を除くデータを出力する出力信号処理部とを備える。

(もっと読む)

半導体リレー

【課題】半導体リレーを小型化すること。

【解決手段】半導体リレー1は、発光ダイオードLD、フォトダイオードPD、スイッチ素子Q、および抵抗Rを備える。フォトダイオードPDのアノードには、スイッチ素子Qのソースと、端子P4と、が接続される。フォトダイオードPDのカソードには、スイッチ素子Qのゲートと、抵抗Rの一端と、が接続される。抵抗Rの他端には、スイッチ素子Qのドレインと、端子P3と、が接続される。

(もっと読む)

半導体リレー

【課題】専有面積が小さくかつ多数の半導体リレーを搭載可能な半導体リレーを提供する。

【解決手段】半導体リレー1の発振回路10と、昇圧回路20と、充放電回路30とが1チップで構成されている。この半導体リレー1は、第1及び第2の入力端子Ti1、Ti2に接続され、入力信号に応答して発振し、信号を生成する発振回路10と、この発振回路10の信号を受信して電圧を発生する昇圧回路20と、この昇圧回路20によって発生した電圧を充放電する充放電回路30と、充放電回路30にゲート及びソースが接続された出力用MOSFET41a、41bからなる出力部40とを具備している。そして、この出力用MOSFET41a、41bのドレイン端子を第1及び第2の出力端子To1、To2とする構成である。

(もっと読む)

半導体リレー

【課題】低電流下で使用可能であり、高温側での使用が可能で安全でかつ駆動電力効率の高い半導体リレーを提供する。

【解決手段】半導体リレー1は、第1及び第2の入力端子Ti1、Ti2に接続され、入力信号に応答して発振し、信号を生成する発振回路10と、この発振回路10の信号を受信して電圧を発生する昇圧回路20と、この昇圧回路20によって発生した電圧を充放電する充放電回路30と、充放電回路30にゲート及びソースが接続された出力用MOSFET41a、41bからなる出力部40とを具備している。そして、この出力用MOSFET41a、41bのドレイン端子を第1及び第2の出力端子To1、To2とする構成である。

(もっと読む)

近接センサ及び電子機器

【課題】従来の近接センサよりも応答性が向上した近接センサ及び電子機器を提供する。

【解決手段】近接センサ1は、電流信号S3の電流値が第2閾値電流以下になったとき、記憶部21に格納されている状態情報を状態ST1に更新し、状態情報が状態ST1であって、かつ、上記電流値が第2閾値電流を越えたとき、状態情報を状態ST2に更新し、上記電流値が第1閾値電流以上になったとき、状態情報を状態ST3に更新し、状態情報が状態ST3であって、かつ、上記電流値が第1閾値電流を下回ったとき、状態情報を状態ST4に更新する状態更新部22と、状態情報が状態ST1または状態ST4に更新されたとき、被検出対象Bが近接していないことを示す信号S6を外部に出力するとともに、状態情報が状態ST2または状態ST3に更新されたとき、被検出対象Bが近接していることを示す信号S6を外部に出力する制御部5とを備える。

(もっと読む)

外部アダプター

【課題】 消費電力の少ない回路によって2線式電子スイッチのON/OFF状態を的確に検出できる外部アダプターを提供する。

【解決手段】 外部アダプター11は、電子スイッチ1に接続される2つの入力端子12,13を備える。分圧抵抗器R1,R2は入力電圧を分圧し、分圧抵抗器R2の両端電圧に基づいて、フォトカプラー14が電子スイッチ1のON/OFF状態を検出する。インピーダンス調整回路19は、入力端子12,13間に介装された調整抵抗器R3、フォトカプラー14の出力に応答して調整抵抗器R3への通電/遮断を切り替えるトランジスタQ1およびフォトMOSリレー18を備え、アダプター11の入力インピーダンスを電子スイッチ1の接点導通状態で相対的に高く、接点非導通状態で相対的に低く調整する。

(もっと読む)

1 - 20 / 95

[ Back to top ]