Fターム[5J055AX11]の内容

Fターム[5J055AX11]の下位に属するFターム

低消費電力化 (382)

低電圧化、低電圧駆動 (45)

Fターム[5J055AX11]に分類される特許

1 - 20 / 55

電圧検出回路

負荷制御装置

【課題】高デューティ領域においてデューティ比が不正確になるのを防止することにより、デューティ比の精度を向上させた負荷制御装置を提供する。

【解決手段】三角波生成回路5が、負荷2に供給される電源電圧VIから三角波VC1を生成する。パルス駆動回路6が、三角波生成回路5により生成される三角波VC1と基準電圧Vkとの比較に応じたデューティ比の駆動パルスを負荷2に供給する。基準電圧生成回路7が、電源電圧VIが増加するに従って基準電圧Vkを増加または減少させて駆動パルスのデューティ比を減少させる。周波数調整回路8が、電源電圧VIが所定電圧以下のときに、三角波生成回路5により生成される三角波VC1の周波数を低くして駆動パルスの周波数を低くする。

(もっと読む)

半導体スイッチ回路

【課題】入出力端子におけるアイソレーション劣化を抑制可能とする。

【解決手段】

第1の入出力端子51と第2の入出力端子52間に第1の単位スイッチ101が、第1の入出力端子51と第3の入出力端子間53に第2の単位スイッチ102が、それぞれ設けられ、第2の入出力端子52とグランドとの間に第1のシャントスイッチ103及び第1のDCカットコンデンサ49が、第3の入出力端子53とグランドとの間に第2のシャントスイッチ104及び第2のDCカットコンデンサ50が、それぞれ直列接続され、第1及び第2の単位スイッチ101,102を構成する第1乃至第4のFET1〜4のゲート・ドレイン間には、それぞれ付加容量41〜44が接続されると共に、第1の単位スイッチ101に対して第1の端子間連絡用抵抗器31が、第2の単位スイッチ102に対して第2の端子間連絡用抵抗器32が、それぞれ並列接続されたものとなっている。

(もっと読む)

電圧駆動型素子を駆動するための駆動回路

【課題】ゲートコレクタ間容量が大きい場合でも、キャパシタンスを大きくすることなく、ターンオン損失を低減することができる電圧駆動型素子を駆動するための駆動回路を提供することにある。

【解決手段】本発明では、駆動回路の最終段トランジスタTr1の出力点とIGBTのゲート端子Gとの間を、ゲート抵抗Rg1を介して接続し、ゲート抵抗Rg1にコンデンサCexの一端を接続し、コンデンサCexの他端を駆動回路の電源Vccへ接続している。IGBTのゲートエミッタ間容量Cgeに蓄積された電荷が、IGBTのゲートコレクタ間容量Cgcへ放電された後、コンデンサCexを介して、電源Vccから少なくともゲートエミッタ間容量Cgeを充電する。

(もっと読む)

半導体装置、およびそれを用いた超音波診断装置

【課題】良好な線形性を有し、かつ電力損失の少ない双方向アナログスイッチの半導体装置を提供する。また、検出精度の高い超音波診断装置を提供する。

【解決手段】双方向にオンまたはオフ可能なスイッチ回路と、前記スイッチ回路の駆動回路を内蔵した双方向アナログスイッチの半導体装置であって、前記駆動回路は第一および第二の電源に接続され、前記第一の電源電圧は、前記スイッチ回路の入出力端子に印加される信号の最大電圧値以上であり、前記第二の電源電圧は、前記スイッチ回路の入出力端子に印加される信号の最小電圧値以下であり、さらに前記駆動回路は前記第一の電源と前記スイッチ回路との間に、直列に接続されたツェナダイオードとP型MOSFETを備えている。また、超音波診断装置であって、前記半導体装置を備える。

(もっと読む)

カレントミラー回路、電流生成回路及び発光装置

【課題】負荷に供給する電流を精度よく出力する。

【解決手段】ゲート電極とドレイン電極が短絡されている第1トランジスタTr1と、第1トランジスタTr1のゲート電極に、ゲート電極が接続された第2トランジスタTr2と、を備えるカレントミラー回路10において、第1トランジスタTr1と第2トランジスタTr2は、絶縁膜12を介してゲート電極1の上部に設けられてチャネル領域が形成される半導体膜2と、半導体膜2上のチャネル領域を覆う領域に設けられる保護膜3と、半導体膜2のチャネル領域を挟む一対の端部に離間して設けられるとともに保護膜3の一部に重なって設けられソース電極6及びドレイン電極7とをそれぞれ有するとともに、少なくとも第2トランジスタTr2は、ソース電極6の保護膜3に対するチャネル長方向への重なり長がドレイン電極7の保護膜3に対する重なり長より長い構造を有する。

(もっと読む)

スイッチング素子駆動回路

【課題】電力伝送効率が良く、より小型化できるスイッチング素子駆動回路を提供する。

【解決手段】スイッチング素子102のゲート信号を発生させる制御演算装置101と、スイッチング素子と制御演算装置との絶縁を確保するトランス110と、第1の周波数とより速い第2の周波数の信号を発生する発振装置105,107と、ゲート信号の立ち上がり及び立ち下りの瞬間に一定時間だけ第1の周波数から第2の周波数に変化させた交流信号を出力する交流周波数変更手段111と、第1の周波数を第1のゲインにて変圧し、第2の周波数をより大きな第2のゲインで変圧して出力する共振回路110,109と、交流信号の振幅変化に従ってゲート信号の立ち上がり及び立ち下がりを復調して復調ゲート信号を出力する復調回路132,133,134と、復調ゲート信号によりスイッチング素子のゲートをオン/オフ駆動するゲートドライブ回路142,143を備えている。

(もっと読む)

ゲート駆動回路

【課題】本発明は、レベルシフト高圧トランジスタのゲートに接続される電源の電圧が高い場合にも低い場合にも弊害なく稼動するゲート駆動回路を提供することを目的とする。

【解決手段】ゲート電圧の波形がパルス信号で制御されるレベルシフト高圧トランジスタと、該レベルシフト高圧トランジスタのゲートと電源を接続する抵抗と、該レベルシフト高圧トランジスタのドレインと接続され、該レベルシフト高圧トランジスタのドレイン電流に応じてゲート駆動信号を出力する高電圧回路と、該レベルシフト高圧トランジスタのソース及びゲートと接続され、該ドレイン電流が増大すると該抵抗を流れる電流を増大させるように構成されたカレントミラー回路と、該電源の電源電圧が低い場合は該抵抗の抵抗値を低減させ、該電源の電源電圧が高い場合は該抵抗の抵抗値を維持する抵抗調整手段とを有する。

(もっと読む)

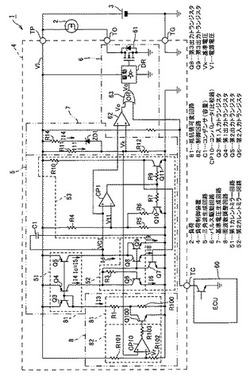

電磁誘導負荷の制御装置

【課題】演算器等によりデューティー比を求めることなく、目標電流値に応じたデューティー比を自動で調整できる電磁誘導負荷の制御装置を提供する。

【解決手段】直流電源と接地間に、スイッチングデバイスQおよび電磁誘導負荷100を直列に接続した回路において、スイッチングデバイスQのPWM駆動中のオフ時の回生電流を検出する電流センサ11と、検出された検出電流が目標電流値よりも小さくなったときに電流検知信号Idetectを出力する電流検知回路12と、所定周波数のクロック信号と前記電流検知信号Idetectを入力とし、前記Idetectが立ち上がってから前記クロック信号が立ち下がるまでの期間ハイレベル又はローレベルとなるPWM信号Vpwmを生成するPWM信号生成回路13と、前記PWM信号VpwmによってスイッチングデバイスQを駆動制御するドライブ回路14と、を備えた。

(もっと読む)

トランスミッションゲート及び半導体装置

【課題】様々な入力電圧に対応して高S/N特性を実現できるトランスミッションゲートを提供する。

【解決手段】入力電圧Vinをドレインから入力され、電圧(Vin−Vs1)をゲートに入力されるとオンし、入力電圧Vinを出力電圧Voutとしてソースから出力するPMOSトランジスタ11と、PMOSトランジスタ11と等しいゲート長とゲート幅とゲート酸化膜厚と閾値電圧の絶対値とを有し、入力電圧Vinをドレインから入力され、電圧(Vin+Vs1)をゲートに入力されるとオンし、入力電圧Vinを出力電圧Voutとしてソースから出力するNMOSトランジスタ12と、を備える。

(もっと読む)

信号切替装置および周波数特性補償方法

【課題】信号の経路長が変化する場合、その信号における周波数特性に起因する歪みを補償することができないという問題を解決する信号切替装置を提供する。

【解決手段】信号切替回路2は、入力コネクタ1‐0〜1‐(m−1)と出力コネクタ5‐0〜5‐(n−1)との接続関係を切り替える。また、補償回路3‐0〜3‐(n−1)および制御回路8を含む補償部は、入力コネクタ1‐0〜1‐(m−1)のそれぞれに入力された各信号の周波数特性のそれぞれを、信号切替回路2にて切り替えられた接続関係に応じて補償する。

(もっと読む)

入力回路

【課題】ヒステリシス電圧や応答速度の電源電圧依存性を緩和し、幅広い範囲の電源電圧条件下で動作するヒステリシス特性を有する入力回路を提供すること。

【解決手段】低電源電圧条件下でヒステリシス電圧が小さくなる回路(PMOSトランジスタ101〜103及び、インバータ501)と、低電源電圧条件下でヒステリシス電圧が大きくなる回路(PMOSトランジスタ101、104及び、インバータ501)とを設けた。

(もっと読む)

スイッチング素子の駆動回路、コンバータ

【課題】 FETを駆動する駆動回路の動作を安定化する。

【解決手段】 FETを駆動する駆動回路であって、FETのオン時にFETに印加される電圧を保持するコンデンサと、FETのオフ期間に、コンデンサに保持された電圧が供給されてFETをオフさせるトランジスタを有する。

(もっと読む)

CV変換回路

【課題】コストおよび消費電力の増大をともなう高速の演算増幅器に依存することなく、IC化に適した回路でもって、高い周波数領域での静電容量挙動を高感度かつ高確度に検出できるようにし、これにより、高周波領域での誘電率挙動による物性の検査や分析を的確に行うことを可能にする。

【解決手段】2つのセンサ容量素子Cx1,Cx2を高周波クロック信号+Φ1に同期して相補的に充放電させる通電回路50と、その2つのセンサ容量素子の通電電流差分ΔIxと上記高周波クロック信号+Φ1とのアナログ乗算操作によって、上記通電電流差分に応じた直流成分を有する電圧Vo1を出力する同期検波回路10と、この同期検波回路10の検波出力電圧を平滑処理しながら増幅する演算増幅器30とを備え、この演算増幅器30の出力から上記2つのセンサ容量素子の静電容量差分ΔCxに対応する直流出力電圧を得る。

(もっと読む)

CV変換回路

【課題】超小型に形成されて容量値および容量変化が非常に微小なセンサ容量素子の容量変化を、高効率かつ高精度に電圧変化に変換させて検出する。

【解決手段】センサ容量素子Csの静電容量を、スイッチドキャパシタ型負帰還回路を有する演算増幅器11によって電圧変換するCV変換回路であって、その負帰還回路は、演算増幅器11の出力端子と反転入力端子間に直列に接続された第1,第2の容量素子C1,C2と、その容量素子C1,C2の中間接続点bに一方の電極端子が接続された第3の容量素子C3と、この容量素子C3の他方の電極端子を演算増幅器11の出力端子または基準電位に接続する切り換えスイッチ回路Sw1,Sw2を有し、このスイッチ回路の接続位置によって等価的な帰還容量値を可変設定する。

(もっと読む)

ドループ補正ピークホールド回路

【課題】ピークホールド回路において、ドループを抑制してピーク電圧を長時間保持できるドループ補正ピークホールド回路を提供すること。

【解決手段】ピークホールド回路のホールドコンデンサC1は、一端をダイオードD1のカソードに接続し、他端をドループ補正回路20に接続してある。ドループ補正回路20は、ホールドコンデンサC2の保持電圧を、増幅回路A3において極性を反転してホールドコンデンサC1に印加する。即ちドループ補正回路20は、ホールドコンデンサC1にその保持電圧と逆極性のドループ補正電圧を印加する。ドループ補正電圧の印加によりホールドコンデンサC1のドループを長時間抑制できる。

(もっと読む)

半導体装置

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】TXシリーズトランジスタSE(TX),RXシリーズトランジスタSE(RX)およびRXシャントトランジスタSH(RX)を低耐圧MISFETQNから構成する一方、TXシャントトランジスタを高耐圧MISFETQHから構成する。これにより、TXシャントトランジスタSH(TX)を構成する高耐圧MISFETQHの直列接続数を少なくすることで、直列接続された各高耐圧MISFETQHに印加される電圧振幅の不均一性を抑制する。この結果、高次高調波の発生を抑制することができる。

(もっと読む)

カウンタ回路およびタイマー回路ならびにカウント方法および計時方法

【課題】最大カウント値を大きくすると、カウンタ回路の規模が増大する。

【解決手段】駆動部20は、所定のイベントが発生するごとに、所定回数、極性を交互に反転させながら強誘電体10に駆動電圧Vdrv1、Vdrv2を印加する。判定部30は、強誘電体10の分極量を測定し、イベントの発生回数を判定する。この判定部30は、電気的信号が印加されたことに起因する強誘電体10の疲労特性を利用して、経過時間が所定のしきい値を超えたか否かを判定する。

(もっと読む)

チャージポンプ回路

【課題】チャージポンプ回路の出力電圧と所望の電圧との差を小さくすることにより、回路の電力効率を向上させる。

【解決手段】このチャージポンプ回路は、入力端子と出力端子の間に直列接続された複数のスイッチング素子と、前記入力端子に入力電圧を供給する電圧源と、前記複数のスイッチング素子の接続点に一端が接続されたコンデンサと、前記コンデンサの他端にクロックパルスを供給するクロックドライバーと、を具備し、前記出力端子から正の昇圧電圧を出力するチャージポンプ回路であって、前記クロックドライバーの中でクロックドライバーCDV1が前記入力電圧を供給する電圧源と、当該入力電圧より低い電圧からなる電圧源の間に接続されており、他のクロックドライバーが前記入力電圧を供給する電圧源と接地電位との間に接続されている事を特徴とする。

(もっと読む)

半導体装置

【課題】半導体集積回路にDAコンバータが内蔵され、且つ、上記DAコンバータとデジタル回路とでパッドが共有される場合のアナログ電源電圧の動作範囲を改善する。

【解決手段】複数の抵抗が結合されて成るラダー抵抗回路を含むR−2R型DAコンバータ(106)と、デジタル信号の入出力を可能とするデジタル回路(601)と、上記DAコンバータの出力ポートと上記デジタル回路の入出力ポートとの間で共有されるパッド(602)とを設ける。そして、上記R−2R型DAコンバータが非アクティブ状態とされるとき、上記ラダー抵抗回路を上記R−2R型DAコンバータから切り放すためのスイッチ制御回路(20)を設け、上記DAコンバータのアナログ信号出力ポートを導電ライン(320)によって上記パッドに直結することで、アナログ電源電圧の動作範囲を拡大する。

(もっと読む)

1 - 20 / 55

[ Back to top ]