Fターム[5J055BX01]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | 切り換えスイッチ (661)

Fターム[5J055BX01]の下位に属するFターム

複数接続の切り換え (528)

スイッチの接続の形態 (70)

入出力の切り換え (13)

自動切り換え回路 (27)

択一動作のみではないもの(合成等) (2)

Fターム[5J055BX01]に分類される特許

1 - 20 / 21

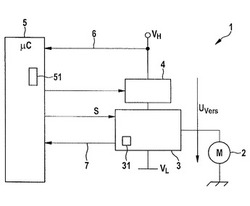

駆動回路のための供給電圧スイッチの性能を検査する方法、および装置

【課題】駆動回路の供給電圧スイッチの性能を検査する方法及び装置を提供する。

【解決手段】ポジショナシステム1は、アクチュエータ2と、アクチュエータ2を駆動する駆動回路3と、駆動回路3に電気的エネルギーが供給されるように駆動回路3に直列に接続された供給電圧スイッチ4と、供給電圧スイッチ4が閉じるよう駆動される場合に、アクチュエータ2の駆動のために十分な電圧が駆動回路3内で検出されるかによって、供給電圧スイッチ4の性能を確認するための制御ユニット5を具備する。

(もっと読む)

サンプルホールド回路

【課題】インバータなどの遅延が無視できない高速動作時において、クロックフィールドスルーの影響を改善するのが困難

【解決手段】MOST4はソース端子に入力されるアナログ入力信号を矩形波パルスのサンプル信号によりオンオフしてサンプリングする。MOST5はMOST4のドレイン端子にソース端子およびドレイン端子が接続されサンプル信号の極性を反転した反転サンプル信号によりオンオフしてMOST4の寄生容量を補償する。論理回路10,11はサンプル信号と反転サンプル信号の位相差を検出して誤差信号を出力する。MOST6,7はMOST5のソース端子およびドレイン端子にソース端子およびドレイン端子が接続され、位相差を補償する。

(もっと読む)

特に自動車で使用するための制御回路を作動する方法

第1および第2出力部と、第1および第2切換手段とを備える制御回路の作動方法に関し、負荷を作動するために出力部の間に印加される制御電圧を次にように形成する。切換手段によって第1出力部を第1または第2電位に選択的に接続し、切換手段によって第2出力部を第1または第2電位に選択的に接続することによって形成し、制御電圧が少なくとも短時間少なくともほぼゼロとなる状態を、第1の場合には2つの出力部を2つの切換手段によって同時に前記第1電位に接続することによって誘起し、第2の場合には2つの出力部を2つの切換手段によって同時に第2電位に接続することによって誘起し、制御回路の作動時に、2つの場合を少なくとも1回誘起し、いずれの場合にも、出力部に印加された制御電圧を特徴づける変数または出力部/スイッチに対して直列に配置した少なくとも1つのシャント抵抗器を介して流れる電流を特徴づける変数を検出し、比較を行う。 (もっと読む)

半導体集積回路装置及び半導体集積回路装置の試験方法

【課題】配線領域の増大を抑制しつつも、電源遮断回路が正常に機能しているかを試験することのできる半導体集積回路装置を提供する。

【解決手段】内部回路10と電源遮断回路20との間のノードAの仮想電源電圧VD1を比較電圧Vnに変換する電圧シフト回路40と、電源遮断回路20の電源通電動作時に高電位基準電圧を生成し、電源遮断動作時に低電位基準電圧を生成する基準電圧生成回路50が備えられる。また、電圧シフト回路40からの比較電圧Vnと、基準電圧生成回路50からの基準電圧VRとを比較して判定信号JSを生成し、その判定信号JSを出力パッド75に出力する電圧比較回路60が備えられる。

(もっと読む)

動作ロジック切替装置

【課題】従来の動作ロジック切替装置は、機器コネクタに外部コネクタを接続するだけでなく、スイッチの切替操作等を行わなければ所望の動作ロジックでの動作が行われず、信頼性及び整備性が低くなっている。

【解決手段】本発明による動作ロジック切替装置は、接続体73により各外部端子部71,72を選択的に閉成又は開成することにより、外部コネクタ7が機器コネクタ2に接続された際に第1及び第2の開放入力端子部21,22が各外部端子部71,72の前記閉成及び開成に対応して閉成又は開成され、入力信号生成部5は、前記第1及び第2の開放入力端子部21,22の閉成及び開成の組み合わせに応じて第1〜第4の入力信号5aのいずれかを生成する

(もっと読む)

インターフェース回路

【課題】入力部3の入力信号S1を制御部2に入力するものにあって、入力部3と制御部2との間に接続された抵抗素子R3の発熱を防止することで、抵抗素子R3の耐久性を向上させる。

【解決手段】制御部2に接続された入力部3の入力信号S1を入力インターフェース部4を介して制御部2に入力するようにした入力インターフェース回路1において、入力部3と制御部2との間に接続された抵抗素子R1の発熱を防止すべく、入力部3からの入力信号S1を間欠的に制御部2に入力させる間欠入力手段5が設けられている。

(もっと読む)

高周波スイッチ回路、高周波スイッチ装置、及び送信モジュール装置

【課題】広帯域で高周波特性に優れ、かつ静電サージ等の高電圧信号が流れ込んだ場合の耐破壊性に優れた、安価な高周波スイッチ回路を提供する。

【解決手段】FET11〜18及びFET21〜28を駆動する制御端子V11及びV12に負バイアス電圧及び0V以上かつショットキー順方向電圧以下の正バイアス電圧のいずれかを用いて、第1の入出力端子P11から第2の入出力端子P12へ伝達される経路、及び第1の入出力端子P11から第3の入出力端子P13へ伝達される経路の、ON/OFFを切り替える。これにより、DCカット用のコンデンサが不要となる。

(もっと読む)

ON側を危険側とするフェールセーフ性を有するスイッチ回路

【課題】半導体スイッチ素子と電流・電圧検知素子とを使用してON側を危険側とするフェールセーフ性を有するスイッチ回路を構成する。

【解決手段】半導体スイッチ素子と電流・電圧検知素子とを配置して、複数の半導体スイッチ素子の一つがON故障しても出力側に電流が流れないよう構成し、出力側に電流を流さないままで各スイッチ素子のON故障を検知することを可能とした。

(もっと読む)

半導体集積回路

【課題】環状配線から電力の供給を受けるマクロセルを有し、消費電力を低減することが可能な半導体集積回路を提供する。

【解決手段】この半導体集積回路は、所定の機能を実現するためのマクロセルMC1と、マクロセルMC1を囲むように配置され、マクロセルMC1に接続された環状配線L1と、環状配線L1を囲むように配置され、電源電位VDDに接続された環状配線L2と、環状配線L2を囲むように配置され、電源電位VSSに接続されるとともにマクロセルMC1に接続された環状配線L3と、制御信号に従って環状電源L1と環状電源L2との間又は環状配線L1と環状配線L3との間を接続するためのスイッチ回路としてのCMOSインバータINV1,INV2とを具備する。

(もっと読む)

電気回路装置

【課題】 ウィスカが発生して一旦電気的に短絡した状態になっても、この短絡状態を除去することができる電気回路装置を得る。

【解決手段】 切替制御部98からの制御信号に従って、各切替スイッチ部92A、92Bが点線で示される第2の位置、各オンオフスイッチ部100が点線で示されるオフの位置に切り替えられ、隣り合う端子部76C間及び隣り合う端子部78C間に大きな電位差を生じさせることで、隣り合う端子部76C間、又は、隣り合う端子部78C間の少なくともいずれかの箇所にウィスカによる短絡部102が発生した状態となっている場合には、短絡部102を溶かして切断する。

(もっと読む)

可動素子、ならびにその可動素子を内蔵する半導体デバイス、モジュールおよび電子機器

【課題】パッケージサイズの縮小化を妨げることがなく、しかも低電圧・低消費電力系の素子と一体的に形成することが可能な程度に低電圧・低消費電力の可動素子、ならびにその可動素子を内蔵する半導体デバイス、モジュールおよび電子機器を提供する。

【解決手段】半導体基板10上に、信号を伝送するための信号線路11と、信号線路を機械的に継断するための継断部12と、継断部12を切り替えるための切替部13と、継断部12の切り替え後の状態を保持するための保持部14とを備える。継断部12および保持部14は互いに対向配置された一組の固定子12A,14Aおよび可動子12B,14Bを、切替部13は保持部14の可動子14Bと対向配置された可動子13Bをそれぞれ有する。切替部13の可動子13Bおよび保持部14の可動子14Bの少なくとも一方が、弾性部15を介して継断部12の可動子12Bと接続されている。

(もっと読む)

化合物半導体スイッチ回路装置

【課題】スイッチMMICにおいて、第1ソース電極13および第2ソース電極とドレイン配線または第1ドレイン電極14および第2ドレイン電極とソース配線が近接している箇所において、高周波信号の漏れがあり、電気的特性が劣化する問題があった。

【解決手段】2つのゲート電極の櫛歯の一端を窒化膜上のゲート接続金属層に接続する。ゲート接続金属層は第1ソース電極および第2ソース電極とドレイン配線間、または第1ドレイン電極および第2ドレイン電極とソース配線間に配置する。オフ側FETのゲート電極は高周波信号としてGND電位であるので、ドレイン−ソース間の高周波信号の漏れを防止できる。ゲート接続金属層と2つのゲート電極(櫛歯)により、1つのソース電極(ドレイン電極)の櫛歯を包囲し、高周波信号の漏れを防止する。ゲート電極形成時にはレジスト除去液が隣接するゲート電極間に十分滲入するのでリフトオフが容易となる。

(もっと読む)

半導体集積回路

【課題】 オプション機能の切り替えをパワーオン期間に実施し、半導体集積回路がパワーオンから通常動作を開始するまでの期間を短縮する。

【解決手段】 機能切替部14は、互いに異なる論理値にプログラムされる一対のプログラム素子MC1、MC2を有する。機能切替部14の判定回路LTは、パワーオン時の電源電圧が上昇する期間に、プログラム素子MC1、MC2にそれぞれ流れる電流値の差に応じた論理レベルを出力する。オプション機能部16は、判定回路LTが出力する論理レベルに応じて、動作仕様が切り替わる。すなわち、プログラム素子MC1、MC2のプログラム状態に応じて、パワーオンが完了するまでにオプション機能部16の動作仕様が自動的に決定される。オプション機能部16の動作仕様を決定するために、プログラム素子MC1、MC2に対する読み出し動作を実行する必要はない。パワーオン後の初期化処理が簡易になるため、パワーオンから通常動作を開始するまでの期間を短縮できる。

(もっと読む)

半導体装置及びその冗長救済方法

【課題】 大規模化した半導体装置の歩留向上および信頼性向上が容易に図れるようにすること。

【解決手段】 制御回路108からの制御信号S(i)によって電流測定タイミングになると、各分割論理回路ブロック1051〜r−1の静止電源電流値が測定される。そして制御回路108は、分割論理回路ブロック1051〜r−1の静止電源電流値と基準値とを比較して、静止電源電流が基準値を超える場合、判定信号(i)をLoレベルに設定する一方、静止電源電流が基準値を超えないときは判定信号(i)をHiレベルに設定する。そして、判定信号(i)がLoレベルである不良ブロックを冗長回路ブロック105rと置換するように、セレクタ1062〜r,1071〜r−1に切替え制御信号R(1)〜R(r)を出力し、入出力バスの接続を切り替え、その不良ブロックへの電源供給も停止する。

(もっと読む)

レベルシフタ回路

【課題】CMOSゲートのみで貫通電流を防止するレベルシフタ回路を提供する。

【解決手段】入力端子50からの入力信号Vinと遅延部21で遅延させた入力信号Vin’を、第1の電源電圧の低電位電圧VDDLが供給されるNORゲート22とANDゲート23に入力、各々出力をゲート電圧VG1とゲート電圧VG2とする。レベルシフト部10用で、第2の電源電圧の高電位電圧VDDHが供給される第2の電源電圧端子30に接続されたPMOSトランジスタ1,2のゲートとドレインを交差接続し、各々のドレインとソースが接地端子40に接続されたNMOSトランジスタ4,5のドレインとを接続する。NMOSトランジスタ4,5のゲートにはNORゲート22出力とANDゲート23出力を接続する。NMOSトランジスタ5のドレイン電圧VD2をPMOSトランジスタ3とNMOSトランジスタ6に接続し、出力信号Voutを出力端子70から出力する。

(もっと読む)

信号入力装置

【課題】スイッチ手段の開閉状態により信号ラインの電圧が変化するような信号入力装置において、経時的に生成される酸化皮膜を除去できるとともに消費電力の低減を実現する。

【解決手段】スイッチ手段SW*(*は0〜7)を介して電源電圧VDに接続される8つの信号ラインL*の電圧をマイコン3に入力させる回路5は、各信号ライン毎の通電量増減回路ZK*と、一端が接地電位(=0V)に接続された抵抗25とを備えている。そして、各通電量増減回路ZK*では、抵抗25よりも抵抗値が大きい抵抗R*で信号ラインL*を常時プルダウンするが、スイッチ手段SW*がオンされてからある時間までは、スイッチCT*がオンとなって信号ラインL*を小抵抗値の抵抗25でもプルダウンする。ある時間だけスイッチ手段SW*に生じた酸化皮膜を除去する大きな電流が流れることになる。

(もっと読む)

増幅回路

【課題】入力信号を増幅して出力する増幅回路に関し、簡単な構成で、確実にミュートをアンプに先行して駆動させることが可能な増幅回路を提供することを目的とする。

【解決手段】本発明は、入力信号を増幅して出力する増幅回路において、入力信号を増幅して出力する第1のアンプ(11、12)と、出力をミュート状態にする第2のアンプ(13、14)と、第1のアンプ(11、12)への駆動電源を供給する第1の電源回路(15、16)と、第2のアンプ(13、14)への駆動電源を供給する第2の電源回路(17、18)と、切換パルスに応じた非反転入力と非反転入力を反転した反転入力とを比較し、比較結果に応じて第1の電源回路(15、16)及び第2の電源回路(17、18)を制御するコンパレータ(32)と、非反転入力と反転入力とに第1のアンプ(11、12)をオンさせずに第2のアンプ(13、14)がオンするように、オフセットを持たせる入力回路(31、131、231)とを有することを特徴とする。

(もっと読む)

入力回路およびそれを備える電子制御装置

【課題】 マイクロコンピュータなどのマイクロコンピュータの入力ポートを、スイッチなどの接地との間の複数の接点入力端で共用するために介在される入力回路において、前記接点入力端の接地電位からの浮きに対しても、正確に接点状態を判定できるようにする。

【解決手段】 各接点入力端IN1〜IN8に対して、ベースが接続されるトランジスタQ1〜Q8を設け、たとえば奇数番目と偶数番目とのように、複数のトランジスタをマイコン12のI/OポートP01,P02からの選択出力で纏めて選択/非選択し、かつ同時に選択されない複数のトランジスタQ1とQ2.Q3とQ4,Q5とQ6、Q7とQ8のコレクタ電流を共通の抵抗R1〜R4を用いて電圧変換し、I/OポートP1〜P4に与える。したがって、スイッチSW1〜SW8のオン抵抗などで、接地電位時に接点入力に浮きが生じても、正確に接点状態を判定することができる。

(もっと読む)

インタフェース回路

【課題】 P1形およびP2形のうちの所望の形式で使用することができ、応答速度が速いインタフェース回路を提供する。

【解決手段】 インタフェース回路をP1形で使用する場合は端子T4とT6を接続し、P2形で使用する場合は端子T5とT6,T7とT8をそれぞれ接続する。車両感知信号/Dが活性化レベルの「L」レベルになると、P1形の場合はフォトトランジスタ6が導通せず、出力端子T2,T3間が非導通状態になり、P2形の場合はフォトトランジスタ6が導通し、出力端子T2,T3間が導通状態になる。従来のフォトMOSトランジスタの代わりにフォトトランジスタ6を使用したので、応答速度が速くなる。

(もっと読む)

半導体集積回路

【課題】 高精度で内蔵発振を行うことができる半導体集積回路を提供する。

【解決手段】 半導体集積回路は、記憶回路(6)と、記憶回路に保持された制御情報に基いて内部クロック信号(VCLK)を生成する発振回路(23)と、外部クロック信号(RCLK)の周波数に内部クロック信号の周波数を一致させる制御情報を生成する論理回路(2)と、上記論理回路で生成された制御情報を記憶可能な電気ヒューズ回路又は溶断ヒューズ回路(6cd)を有し、上記内部クロック信号を内部回路の同期動作に用いる。プロセスばらつきにより発振回路の発振周特性(発振周波数)に誤差(不所望な変動)を生じても、水晶振動子の外付けや外部クロック信号の入力を必要とせずに、内部クロック信号周波数を目的周波数の外部クロック信号周波数に一致させることができる。

(もっと読む)

1 - 20 / 21

[ Back to top ]