Fターム[5J055EZ02]の内容

Fターム[5J055EZ02]に分類される特許

1 - 16 / 16

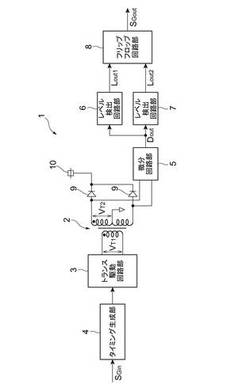

ゲート駆動回路

【課題】ゲート駆動信号の伝達遅延時間のばらつきを低減することができるゲート駆動回路を提供する。

【解決手段】ゲート駆動回路1は、トランス2を駆動するトランス駆動回路部3と、トランス2の一次側の駆動タイミングを生成すると共に、入力ゲート駆動信号のON状態時とOFF状態時とでトランス2の一次側駆動電圧変化率を異なるように設定するタイミング生成部4と、トランス2の二次側電圧を微分することで、トランス2の二次側電圧変化率を検出する微分回路部5と、入力ゲート駆動信号のOFF状態時の微分値レベルを検出するレベル検出回路部6と、入力ゲート駆動信号のON状態時の微分値レベルを検出するレベル検出回路部7と、検出レベル検出回路部6,7と接続されたR端子及びS端子を有し、出力ゲート駆動信号を生成・保持するフリップフロップ回路部8とを有している。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】di/dt帰還部23は、IGBT11Uがターンオフするときに、IGBT11のコレクタ電流Icの時間変化に基づいて、帰還電圧VFBを生成する。また、di/dt帰還部23は、IGBT11がターンオンするときに、図示せぬFWDの転流電流IFWDに基づいて、帰還電圧VFBを生成する。このようなdi/dt帰還部23は、帰還電圧VFBを駆動信号の電圧の一部として印加するタイミングを遅延させる遅延フィルタとして、LPF回路201を備えている。LPF201の遅延量、即ちインダクタンスLdを適度に調整することで、還流ダイオードの電圧におけるサージ電圧を低減させることができる。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】電子回路1は、IGBT11と、FWD12と、半導体素子駆動回路13と、を備えている。半導体素子駆動回路13は、IGBT11のゲート−エミッタ間の電圧Vgeを可変することによって、IGBT11のターンオン及びターンオフを制御する。半導体素子駆動回路13のdi/dt帰還部23は、電子回路1の主電流であるIGBT11のコレクタ電流Icの時間的変化、即ち時間微分値dIc/dtに基づき帰還電圧VFBを生成し、IGBT11のゲート−エミッタ間の電圧Vgeの一部として加算する。

(もっと読む)

駆動装置

【課題】駆動回路やトランジスタにおいてばらつきがあっても、PWM駆動信号の駆動デューティ成分が小さい場合にも、上側トランジスタと下側トランジスタのシュート・スルー(貫通状態)を防止する。

【解決手段】入力端子の第2レベルまたは第1レベル信号に応じてスイッチングデバイスの制御端子に駆動電流をシンク出力するシンク回路と、スイッチングデバイスのオフ期間中に制御端子を経て容量性の電流をシンクする電流シンクトランジスタと、入力端子の信号に応じてソース回路の入力駆動信号と、シンク回路あるいは前記シンクトランジスタへの入力駆動信号とを生成するI/F回路と、シンク回路または前記シンクトランジスタへの入力駆動信号をシンク回路かあるいはシンクトランジスタのどちらに入力駆動信号として出力するかを選択するセレクタと、この選択動作を制御するセレクタへの選択信号を受ける入力端子とを備える。

(もっと読む)

負荷駆動装置及び負荷駆動制御装置

【課題】パワーオンリセット以外のリセットの場合に負荷を駆動し続け、パワーオンリセットの場合には、例えば負荷を駆動するための信号が与えられるまで、負荷を駆動しないようにすることが可能な負荷駆動装置、及び該負荷駆動装置を備える負荷駆動制御装置を提供する。

【解決手段】電源ラインBL側と接地電位との間に直列に接続されたコンデンサC1及び抵抗R1からなる微分器が電源ラインBLの電圧の立ち上がりを微分した微分電圧に基づいて、入力端子221,231を電源ラインBLに夫々プルアップする抵抗R4,R14の入力端子221,231側と接地電位との間にダイオードD3,D13を介して接続されたFETQ1が、少なくとも入力端子221,231に入出力ポート35,36より負荷L1,L2を駆動するための信号を与えられるまで導通する。

(もっと読む)

ラッチ型コンパレータ及びこれを用いた多値論理復調回路

【課題】製造プロセスのマージンを削ることなく、オフセットの補正が可能なラッチ型コンパレータ、及びこれを用いた、オフセットの補正が可能な多値論理の復調回路を提供する

【解決手段】本発明によるラッチ型コンパレータは、クロスカップルされた2つのCMOSインバータからなるフリップフロップを含み、フリップフロップの4個のトランジスタの各々のソースと電源/接地間には伝達トランジスタを介して抵抗と設定電流可変の定電流源が接続され、フリップフロップの差動出力は各々伝達トランジスタを介して差動入力に接続され、全ての伝達トランジスタのゲートは、差動クロック入力のいずれかに接続されていることを特徴とする。

(もっと読む)

二重絶縁ゲート型電界効果トランジスタを用いたゲート回路、SRAMセル回路、多入力CMOSゲート回路、CMOS−SRAMセル回路、集積回路

【課題】高速動作と消費電力の減少を両立させた二重絶縁ゲート型電界効果トランジスタを用いた回路を提供する。

【解決手段】第一の四端子二重絶縁ゲート電界効果トランジスタは、一方のゲートを入力端子、ソースを第一の電源に接続し、ドレインを出力端子、該ドレインを負荷素子を介して第四の電源に接続し、他方のゲートに第一の三端子絶縁ゲート電界効果トランジスタのドレインを接続し、前記第一の三端子絶縁ゲート電界効果トランジスタは、ソースを第二の電源に接続し、ゲートを第三の電源に接続し、前記三端子絶縁ゲート電界効果トランジスタのドレインとソースの間の抵抗と前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートと他方のゲートの間のゲート絶縁膜容量と前記両ゲートに挟まれた半導体の容量で微分回路を構成したゲート回路で、前記第一の四端子二重絶縁ゲート電界効果トランジスタの一方のゲートと他方のゲート間を容量で接続する。

(もっと読む)

出力バッファ回路

【課題】伝送路にノイズが入った場合でも正常に通信ができる通信装置を提供する。

【解決手段】帰還増幅回路(2)と、帰還増幅回路(2)から供給される内部信号に応答して出力ノード(N1)に外部出力信号を供給する出力回路(3)と、帰還増幅回路(2)に対する帰還信号の供給を禁止する帰還遮断回路(4)とを具備する出力バッファ回路(1)を構成する。ここで、帰還増幅回路(2)は、入力端(N2)に入力される送信信号(TXD)と外部出力信号を帰還した帰還信号とに基づいて、内部信号の波形を制御する。そして、帰還遮断回路(4)は、出力ノード(N1)のノイズに基づいて生成される帰還遮断命令に応答して、帰還増幅回路(2)への帰還信号の供給を禁止する。

(もっと読む)

ノイズ低減回路

【課題】面積効率が高く、応答性およびESD耐性も問題が生じないノイズ低減回路を提供する。

【解決手段】ノイズ低減回路は、電源とグランドとの間に配置された容量素子および抵抗素子を含むデカップリング容量回路と、容量素子と抵抗素子との接続点とグランドもしくは電源との間に接続されたダイオード素子とを備える。電源とグランドとの間の電位差が小さくなった場合、ダイオード素子がオン状態になると、グランドからグランド、または、電源から電源へ向かって電流が流れることで、電源ノイズを瞬時に低減できる。

(もっと読む)

電流を調整するための監視及び制御回路

【課題】電流を調整するための監視及び制御回路を提供する。

【解決手段】監視及び制御回路は、検知ブロックと、第1及び第2の比較器と、制御モジュールとを備える。電流検知ブロックは、スイッチを流れる電流を表している監視信号を生成するために、スイッチに連結される。検知ブロックに連結された第1の比較器は、監視信号を第1のしきい値と比較すると共に、監視信号と第1のしきい値との間の第1の比較結果に従って第1の信号を提供するように動作可能である。検知ブロックに連結された第2の比較器は、監視信号を第2のしきい値と比較すると共に、監視信号と第2のしきい値との間の第2の比較結果に従って第2の信号を提供するように動作可能である。第1の比較器及び第2の比較器に連結された制御モジュールは、電流を調整するために、第1の信号及び第2の信号に従ってスイッチを制御する制御信号を提供する。

(もっと読む)

電流ドライバ装置

【目的】被駆動回路に寄生容量がする存在する場合であっても、高速で電流書き込みが可能な電流駆動ドライバ装置を提供する。

【解決手段】電流駆動回路の各々は、データ信号に応じた電流値のデータ電流を供給する第1の電流源と、データ線の電圧の微分値を生成する微分回路を含み、上記微分値に応じた電流値のブースト電流を上記データ線に供給する第2の電流源と、を有している。

(もっと読む)

駆動回路

【課題】負荷のリアクタンス成分の変動によって負荷を駆動するための出力の立上り時間が変動した場合であっても負荷の動作が変動するのを抑制する。

【解決手段】負荷Aの容量値が変動した場合、駆動回路1の傾き調整回路6は、電流制御回路50,51のpMOS52及びnMOS53に印加するゲート電圧を調整し、pMOS52及びnMOS53の各ソース−ドレイン間に流れる電流を調整する。つまり、出力ドライバ4のCMOS回路40を構成するpMOS41及びnMOS42のそれぞれのオン時にpMOS41及びnMOS42の各ソース−ドレイン間に流れる電流を調整する。これにより、出力ドライバ4と負荷Aとの間に流れる電流を制御し、負荷Aの容量成分を充放電させる時間を制御するため、負荷Aの駆動電圧の立上り及び立下りの傾きを補正し、上記駆動電圧の立上り時間及び立下り時間を一定時間にする。

(もっと読む)

容量性負荷駆動回路

【課題】本発明は、印加電圧の変化幅に応じた放電制御を行って容量性負荷に印加する多値の電圧を高速に可変制御できる容量性負荷駆動回路を提供することを目的とする。

【解決手段】容量性負荷に多値の電圧を印加して駆動する容量性負荷駆動回路において、電圧制御信号を生成して出力する電圧制御信号生成手段と、前記電圧制御信号を電圧増幅する電圧増幅手段と、前記電圧増幅手段の出力を電流増幅して前記容量性負荷の充電を行う電流増幅手段と、前記電圧制御信号の立ち下がりの幅が所定値を超えるとき所定パルス幅の立ち下がりパルスを発生する立ち下がり制御信号発生手段と、前記立ち下がりパルスの供給により前記容量性負荷の放電を行うスイッチ手段とを有する。

(もっと読む)

電圧出力回路

【課題】急峻な出力変化を抑制し、出力重畳ノイズを有効に除去する。

【解決手段】例えば2値の電圧出力回路を例にとると、中レベル電圧VMと出力端子Toとの間に接続され、制御ノードに印加される入力電圧INMに応じて動作するNチャネル型の第1出力トランジスタN1と、出力端子Toと低レベル電圧VLとの間に接続され、入力電圧INMと逆相の入力電圧INLに応じて動作するNチャネル型の第2出力トランジスタN2と、出力端子Toに電位変化が生じている間は当該電位変化の制動力を第1出力トランジスタN1の制御ノードに付与し、電位変化がなくなるにしたがって制御ノードを高レベル電圧VHに電気的に接続する駆動制御回路3とを有する。

(もっと読む)

スイッチング装置

【課題】高圧側と低圧側の間に一対以上のノーマリ・オンの半導体スイッチング素子が直列に接続されている場合、ゲート駆動回路の異常動作時に各半導体スイッチング素子に流れる過電流を抑制する。

【解決手段】ノーマリ・オン(ディプレッション型)のハイアーム側半導体スイッチング素子15a〜15cと、同じくノーマリ・オンのローアーム側半導体スイッチング素子17a〜17cとを直列に接続している場合に、各半導体スイッチング素子15a〜15c,17a〜17cの各ゲートを、抵抗19a〜19c,21a〜21cを介してそれぞれ電源Bのマイナス(−)側に接続する。

(もっと読む)

高速変化耐性微分レベルシフトデバイス

【課題】高周波で作動でき、電力散逸量が少なく、共通モードの変化に対して耐性を有するレベルシフトデバイスを提供する。

【解決手段】第1電圧レベル(13)で作動する入力側(14)と、第2電圧レベル(53)で作動する出力側(54)と、入力側と出力側とを接続するレベルシフト回路(48)とを備え、入力回路は、第1電圧レベルを基準とする入力信号(14)を受信し、入力信号の変化に対応する出力信号を発生する。レベルシフト回路は、MOSFET(28)を備え、MOSFETのゲートは、入力回路の各出力に接続され、ソース−ドレインパスは、第2電圧と第1電圧の基準との間に結合されている。出力側は、微分回路トポロジー(50)を有し、入力信号の変化を対応する信号をサンプリングし、その変化の間のサンプルをホールドする第1回路(56)と、微分された形態でホールドされたサンプル信号を受信して、シングルエンド形態に変換する出力回路(54)を有している。

(もっと読む)

1 - 16 / 16

[ Back to top ]