Fターム[5J055EZ03]の内容

Fターム[5J055EZ03]に分類される特許

121 - 140 / 454

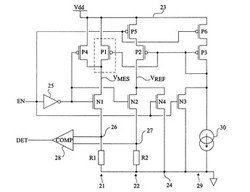

電子回路の作動の監視

【課題】本発明は、電子回路の所与の機能又は動作の実行を監視するための方法及び回路を提供する。

【解決手段】デジタル信号(EN)を監視する方法は、第1のP チャネルMOS トランジスタ(P1)を、監視されるべき前記信号が第1の状態にある期間に負バイアス温度不安定性(NBTI)タイプの劣化状態に置くステップと、前記第1のP チャネルMOS トランジスタ(P1)の飽和電流を表す第1の量(VMES)を、監視されるべき前記信号が第2の状態に切り替わるとき測定するステップと、前記第1の量が閾値(TH)を超えるとき、監視結果を示す検出信号(DET) を与えるステップとを備えている。

(もっと読む)

電気負荷の駆動回路及びこの回路を具えた電気システム

【課題】誤って接続された負荷状態の検出が可能な、電気負荷用の駆動回路を提供する。

【解決手段】電子回路(100)を開示し、この電子回路は、駆動する負荷(LD)に接続可能なノード(EX)、及びこのノードに接続された第1端子を有し、活性状態と非活性状態との間で切り替えることができるパワーデバイス(PD)を具えている。この回路はさらに:上記ノードに接続された出力端子を有し、少なくとも上記パワーデバイスが非活性状態にされている際にイネーブル状態にすることのできる電流発生器(I)と;上記ノードの電圧(V(EX))と基準電圧(V(REF))との比較器(CP)を具え、この比較器は比較結果(RESETN)を得るように構成され、この比較結果から、負荷の上記ノードへの電気接続の異なる状態を検出することができる。

(もっと読む)

半導体回路

【課題】低消費電流でノイズ耐性に優れた高圧側パワートランジスタを駆動する回路を提供する。

【解決手段】低圧側入力信号(HIN)に従って短い期間活性状態となるワンショットパルス(ON_B)を生成するワンショット回路(11)を設ける。第1および第2の電流供給部(14,16)により、入力信号およびワンショットパルスの発生するワンショットパルス信号に従って内部ノード(15)に電流を供給する。第1の内部ノードを流れる電流をウイルソンカレントミラー回路(20)で受け、電流検出部(R3)により電圧信号に変換し、ゲートドライバ(DRV)により、スイッチングパワートランジスタの駆動信号を生成する。

(もっと読む)

半導体集積回路

【課題】ゲート面積を増大させることなく、電界効果トランジスタ間のしきい値電圧のバラツキを自律的に補正させる。

【解決手段】補正回路12は、電子回路11に含まれる半導体素子間の電気的特性の差が所定の周期内の電気的特性の劣化量より大きい場合、その電気的特性の劣化量の小さい方の半導体素子の劣化を進行させ、電子回路11に含まれる半導体素子間の電気的特性の差が所定の周期内の電気的特性の劣化量より小さい場合、その電気的特性に差のある半導体素子の劣化を所定の周期ごとに交互に進行させる。

(もっと読む)

パルス幅変調回路および電圧帰還型D級増幅回路

【課題】出力負荷を駆動する電圧帰還型D級増幅回路の周波数特性を改善する。

【解決手段】入力信号のPWM変調を行なう比較回路(26A,26B)に、PWMキャリアとなる三角波(TOSC)を与える三角波信号発生器(30)に対し、三角波の勾配を補正する三角波補正回路(32)を設ける。三角波(TOSC)のスルーレート(勾配)を出力回路駆動用指令値(COMPOUTP,COMPOUTM)のデューティが50%近傍となる領域において小さくする。

(もっと読む)

ドライバ回路

【課題】ドライバ回路、特にメインドライバに過電圧がかからないようにして、回路を過電圧による破壊から保護する。

【解決手段】第1電源VDDIから動作電源を得て動作するプリドライバB1と、第2電源VDDEから動作電源を得るとともにプリドライバB1からの出力信号を増幅して出力するメインドライバB2と、を備える。第1電源VDDIとプリドライバB1との間に第1スイッチB4を備える。第2電源VDDEとメインドライバB2との間に第2スイッチB5を備える。過電圧保護シーケンス回路B3は、第1スイッチB4および第2スイッチB5のオンオフ制御をして、プリドライバB1とメインドライバB2のオンオフ順序を制御し、ドライバ回路、特にメインドライバB2に過電圧がかかるのを防ぐ。

(もっと読む)

スイッチト出力段のための短絡保護

デバイスのダメージを引き起こしうる短絡条件における過度の出力電流からスイッチング出力段を保護するための、スイッチ型出力段における短絡保護が説明される。この目的を達成するための設計技術は、ドレイン電圧を実質的に等しくするための回路と組み合わせて、スケールされたトランジスタをスイッチングトランジスタと並列に置くことによって、それらスイッチングトランジスタにおける電流を測定することを含む。短絡保護のための様々な技術は、(a)トランジスタと演算増幅器とを組み合わせて使用すること、(b)演算増幅器の代わりに単一のトランジスタを使用すること、(c)過電流検出信号を生成するための回路を使用すること、(d)出力電流を低減するために、ドライバに過電流検出信号を提供すること、(e)出力電流をフィードバック調整するためにインバータを使用すること、(f)通常動作中に電流調整器をバイパスするためにスイッチを使用すること、および(g)過電流状態において、このスイッチを自動的に開くこと、を具備する。  (もっと読む)

(もっと読む)

電子回路

【課題】 充電回路の動作を安定化させる。

【解決手段】 充電回路(100)は、第1出力信号を出力するTr制御回路(24)と、第1出力信号が入力されて動作するトランジスタ(Tr)及びコンデンサ(C1)と、その状態を検出し、その結果としての第2出力信号を出力するコンパレータ(21)と、第2出力信号に基づいて、Tr制御回路をして前記第1出力信号を出力させるかどうかを決定する第3出力信号をTr制御回路に供給するフリップフロップ(24)と、を備え、フリップフロップの入出力特性の遷移帯は、Tr制御回路の入出力特性の遷移帯と重ならない。

(もっと読む)

リセット回路及びリセット用半導体集積回路

【課題】リセット信号の遅延時間の変更が可能なリセット回路及びリセット用半導体集積回路を提供する。

【解決手段】クロック信号を計数する複数のカウンタ回路(カウンタC1〜C3)を有する遅延回路(タイマー部12)を備えたリセット回路において、所定の外部端子(端子P4)に印加される電圧に応じて、前記クロック信号を計数する前記カウンタ回路の段数を変更させ、リセット解除を示すリセット信号の遅延時間を変更可能に構成した。

(もっと読む)

電流スイッチ回路及びそれを用いたD/Aコンバータ、半導体集積回路及び通信機器

【課題】電流加算型D/Aコンバータに用いられる電流スイッチ回路において、低電源電圧時にしきい値電圧の低いトランジスタを用いた際に課題となるダイナミックレンジの低下を改善し、出力電圧範囲を大きく取る。

【解決手段】電流スイッチ回路1は、差動スイッチ12を構成する第1及び第2のトランジスタTr121、Tr122を有する。しきい値電圧制御回路5は、その出力端子Vboutから前記差動スイッチ12を構成する2個のトランジスタTr121、Tr122のサブストレート端子に出力するサブストレート電圧を制御して、前記差動スイッチの2個のトランジスタのしきい値電圧を制御する。従って、電流スイッチ回路1の電源電圧を低減させても、特性劣化を生じることなく、差動スイッチ12内の2個のトランジスタのしきい値に依存する電流スイッチ回路1の出力電圧範囲を大きく取ることができる。

(もっと読む)

閾値回路

【課題】閾値回路を低消費電力化する。

【解決手段】閾値回路は、ゲート端子が入力端子INに接続され、ソース端子が電源電位VDDに接続された第1のPMOSトランジスタQ1と、ゲート端子が入力端子INに接続され、ソース端子がトランジスタQ1のドレイン端子に接続され、ドレイン端子が出力端子OUTに接続された第2のPMOSトランジスタQ2と、ゲート端子が出力端子OUTに接続され、ソース端子がトランジスタQ1のドレイン端子とトランジスタQ2のソース端子との接続点に接続され、ドレイン端子が接地電位に接続された第3のPMOSトランジスタQ3と、第1の端子が出力端子OUTに接続され、第2の端子が接地電位に接続された電流制限部I1とから構成される。

(もっと読む)

出力回路

【課題】出力回路の出力バッファに備えるMOSトランジスタの閾値電圧がばらついても、このMOSトランジスタのoff動作時における出力信号のスルーレートのばらつきを抑制する。

【解決手段】出力回路は、出力バッファ8のNMOSトランジスタ15と、このトランジスタ15をon動作させるためのトランジスタon動作駆動回路51と、このトランジスタ15をoff動作させるためのSW機能付電流源52と、前記トランジスタon動作駆動回路51と前記SW機能付電流源52との各々を制御する駆動制御回路50とにより構成される。前記SW機能付電流源52の電流は、前記出力バッファ8のNMOSトランジスタ15のゲート電圧が閾値電圧Vthのばらつき範囲内でばらついても、一定の電流値でゲート端子の電荷を引き抜く。

(もっと読む)

半導体集積回路

【課題】従来の半導体集積回路は、クロスオーバー電圧の変動幅が増大するという問題があった。

【解決手段】本発明にかかる半導体集積回路は、差動入力の一方に基づいて第1及び第2の信号を生成するプリドライバ4cと、差動入力の他方に基づいて第3及び第4の信号を生成するプリドライバ回路4dと、VDDとVSSとの間に設けられ、第1の信号に基づいて制御されるMN4と、第2の信号に基づいて制御されるMP4と、からなる出力回路5aと、VDDとVSSとの間に設けられ、第3の信号に基づいて制御されるMN8と、第4の信号に基づいて制御されるMP8と、からなる出力回路5bと、VDDに応じた第1の制御信号を生成する制御信号生成回路6と、を備える。さらに、プリドライバ4cは、第1の制御信号に基づいて第1の信号を制御し、第2のプリドライバ4dは、第1の制御信号に基づいて第3の信号を制御する。

(もっと読む)

閾値回路

【課題】閾値回路を低消費電力化する。

【解決手段】閾値回路は、ゲート端子が入力端子INに接続され、ソース端子が電源電位VDDに接続され、ドレイン端子が出力端子OUTに接続された第1のPMOSトランジスタQ1と、第1の端子が第1のPMOSトランジスタQ1のドレイン端子および出力端子OUTに接続され、第2の端子が接地された電流制限部I1と、第1の端子が第1のPMOSトランジスタQ1のドレイン端子および出力端子OUTに接続され、第2の端子が接地された電荷蓄積部C1とから構成される。電流制限部I1の電流値は、サブマイクロアンペア以下に設定される。

(もっと読む)

半導体集積回路

【課題】専用回路部が誤動作を起こすことを防止する半導体集積回路を提供することを目的とする。

【解決手段】電源部11と、制御回路部12と、専用回路部13を有する半導体集積回路であって、前記電源部に設けられ第1電源を生成して前記専用回路部に供給する第1電源回路11aと、前記電源部に設けられ前記第1電源より電圧の低い第2電源を生成して前記制御回路部に供給する第2電源回路11bと、前記電源部に設けられ前記第2電源が立ち上がったのちリセット解除を指示するリセット信号を生成して前記専用回路部に供給するリセット回路11cとを有し、前記制御回路部が動作を開始したのち前記専用回路部のリセットを解除する。

(もっと読む)

CV変換回路

【課題】コストおよび消費電力の増大をともなう高速の演算増幅器に依存することなく、IC化に適した回路でもって、高い周波数領域での静電容量挙動を高感度かつ高確度に検出できるようにし、これにより、高周波領域での誘電率挙動による物性の検査や分析を的確に行うことを可能にする。

【解決手段】2つのセンサ容量素子Cx1,Cx2を高周波クロック信号+Φ1に同期して相補的に充放電させる通電回路50と、その2つのセンサ容量素子の通電電流差分ΔIxと上記高周波クロック信号+Φ1とのアナログ乗算操作によって、上記通電電流差分に応じた直流成分を有する電圧Vo1を出力する同期検波回路10と、この同期検波回路10の検波出力電圧を平滑処理しながら増幅する演算増幅器30とを備え、この演算増幅器30の出力から上記2つのセンサ容量素子の静電容量差分ΔCxに対応する直流出力電圧を得る。

(もっと読む)

電圧検知回路

【課題】nA級の微少電力発電器からの電荷を蓄電する蓄電システムの電荷電位をnA以下の動作電流で電圧検知する。

【解決手段】ダイオード接続した複数のMOSトランジスタを直列接続して2つの電源端子間に接続し、電源電圧の分圧により生成された各電位を直列接続された複数の電流源MOSトランジスタのゲート端子にそれぞれ入力し、電流源トランジスタからの電流を電源電圧の分圧により生成された電位の1つが各ゲート端子に入力された第1のMOSトランジスタペアで2つに分流し、分流された電流をクロスカップル接続された第2のMOSトランジスタペアで電位に変換し、第1のMOSトランジスタペアの一方のゲート端子とドレイン端子をそれぞれ2つの出力端子に接続し、2組のMOSトランジスタペアのうち少なくとも1方のトランジスタペアのゲートのサイズを不揃いにする。

(もっと読む)

半導体装置

【課題】逆接保護機能を有する半導体装置の実装面積を縮小する。

【解決手段】半導体装置50には逆接保護回路1と信号処理部2が設けられる。逆接保護回路1には制御部3、逆接保護ダイオードD1、及びPchパワーMOSトランジスタPMT1が設けられる。逆接保護ダイオードD1はPchパワーMOSトランジスタPMT1の寄生ダイオードである。PchパワーMOSトランジスタPMT1はドレインがノードN1に接続され、ソースがノードN2に接続され、ゲートに制御部3から出力される信号が入力される。制御部3は電源11、電流源12、コンパレータCMP1、抵抗R1、及びスイッチSW1が設けられ、PchパワーMOSトランジスタPMT1のオン・オフ動作を制御する。PchパワーMOSトランジスタPMT1は電源30の瞬停時や逆接続時にオフし、電源30が正常にセットされたときにオンする。

(もっと読む)

ドライバ装置

【課題】UVLO機能を内蔵したドライバ装置を提供する。

【解決手段】電源に接続された第1のスイッチ素子と、前記第1のスイッチ素子と直列接続された第2と、第3と、前記第3のスイッチ素子と並列接続された第4のスイッチ素子と、一端が前記第3及び第4のスイッチ素子に接続され、他端が前記第1のスイッチ素子の制御電極に接続された第1の抵抗と、前記第1の抵抗を介して前記第3のスイッチ素子の負荷となるカレントミラーと、前記カレントミラーに電流を流す放電回路と、外部から入力信号を受けて、前記第2と第3のスイッチ素子を介して前記第1のスイッチ素子と、を交互にオン、オフするように制御し、かつ、前記放電回路及び前記第4のスイッチ素子を、前記電源が立ち上がるときにオンさせて前記カレントミラーに電流を流すことにより、電源が立ち上がった後は前記第4のスイッチ素子をオフする制御回路を備える。

(もっと読む)

過電流保護装置

【課題】過電流検出値が出力電圧によって増大しない保護装置を提供する。

【解決手段】外部入力端子と外部出力端子との間に接続されたドライバトランジスタ3を制御することにより、過電流を制限する過電流保護装置であって、ドライバトランジスタと並列に接続されて所定の比率の電流を流す第1センストランジスタ4と、第1センストランジスタと外部入力端子との間に接続されたセンス抵抗5と、センス抵抗の電圧値を所定の第1バイアス電圧と比較する比較器6とを備え、比較器の出力に基づいてドライバトランジスタのゲート電圧を制御する過電流制限回路100と、ドライバトランジスタのドレイン−ソース間の電位差と、所定の第2バイアス電圧とを比較することにより、ドライバトランジスタのゲート電圧を制御する過電流検出回路101と、を有する。

(もっと読む)

121 - 140 / 454

[ Back to top ]