Fターム[5J055EZ03]の内容

Fターム[5J055EZ03]に分類される特許

161 - 180 / 454

ドライバ回路及びドライバIC

【課題】クロスポイントが50%からずれた電気波形を出力する際も、良好な出力波形を維持することができるドライバ回路を得る。

【解決手段】初段増幅段A1、2段目増幅段A2及び最終増幅段A3の3段の差動増幅段が直列に接続されている。初段増幅段A1及び2段目増幅段A2に、クロスポイント調整回路CP1,CP2がそれぞれ接続されている。クロスポイント調整回路CP1は、初段増幅段A1の正相と逆相のDCレベルの少なくとも一方を制御して、初段増幅段A1の出力信号のクロスポイントを調整する。また、クロスポイント調整回路CP2は、2段目増幅段A2の正相と逆相のDCレベルの少なくとも一方を制御して、2段目増幅段A2の出力信号のクロスポイントを調整する。

(もっと読む)

出力ドライバ回路

【課題】本発明の目的は、被駆動部の確実な駆動を維持しつつも、より高速に被駆動部を駆動することができる、出力信号を得ることができる、出力ドライバ回路を提供することにある。

【解決手段】本発明の一態様にかかる出力ドライバ回路は、入力信号が加えられる入力端子と、前記入力信号を受けてバッファ信号を出力する、第1電源から給電されて動作する、入力バッファと、前記バッファ信号を受けて出力信号を出力端子から出力する、第2電源から給電されて動作する、出力バッファと、前記出力バッファに、前記第2電源の電位が前記第1電源の電位と同等である第1状態時に、前記バッファ信号をそのまま前記出力バッファに加えさせる第1の動作と、前記第2電源の電位が前記第1電源の電位に比して高くなった第2状態時に、前記バッファ信号を前記第2電源の電位に対応するレベルまでレベルシフトしてレベルシフト済信号として前記出力バッファに加えさせる第2の動作とを、切り替えて行わせる、制御部と、を備える。

(もっと読む)

半導体装置

【課題】最大通信距離を維持しつつ、通信距離が極端に短い場合でも半導体装置が正常に動作し、かつ、大きい電力が供給された場合に保護回路が動作したときにも応答波形の振幅を大きくすることができる半導体装置を提供することを課題とする。

【解決手段】入力される信号によって負荷変調を行う第1の変調回路及び第2の変調回路と、外部から供給される電力により出力信号を決定する検出回路と、検出回路の出力信号により動作が制御される保護回路と、検出回路の出力信号により第1の変調回路と第2の変調回路の選択を切り替える変調選択回路と、を有することにより上記課題を解決する。

(もっと読む)

温度補償回路及び電流源回路

【課題】 簡単な構成で電流源回路を温度補償することができる温度補償回路及び電流源回路を提供する。

【解決手段】 温度補償回路1は、第1トランジスタM1と同チャネル型のMOSFETにて構成した第2トランジスタM2を設けて構成してあり、ゲート電圧生成手段たる第2トランジスタM2のソースは前記第1トランジスタM1のゲートに接続してある。また、温度補償回路1にはスイッチング素子として動作させる第3トランジスタM3が設けてあり、第3トランジスタM3のドレインと第2トランジスタM2のソースとを直列接続してある。

(もっと読む)

半導体集積回路

【課題】発振回路において発振動作が行われているか否かを判定する発振停止検出回路を内蔵した半導体集積回路において、電源電位が立ち上がる際の誤検出を防止する。

【解決手段】この半導体集積回路は、クロック信号又は反転クロック信号がゲートに印加されて交互にオン/オフする複数のトランジスタが直列に接続され、第1の電源電位から正の電荷を移送するトランジスタ列と、複数のトランジスタによって移送される電荷を蓄積する複数のコンデンサと、最終段のコンデンサの端子をプルダウンするプルダウン素子と、最終段のコンデンサの端子の電位がゲートに印加され、第2の電源電位がソースに供給されるNチャネルMOSトランジスタと、該NチャネルMOSトランジスタのドレインをプルアップするプルアップ素子と、該NチャネルMOSトランジスタのドレイン電位に基づいて出力信号を生成する論理回路とを具備する。

(もっと読む)

負荷駆動回路

【課題】温度変動が生じた場合においても、適切な電流制御を行い、設定電流値と同じ値の電流を負荷に流す負荷駆動回路を提供する。

【解決手段】電源15から負荷2への電力供給経路に直列に接続されオン/オフ動作により負荷2に流れる電流を制御する出力半導体素子8と、PWM調整回路12と、PWM信号に基づき出力半導体素子8を駆動する駆動回路13と、負荷2に流れる電流を検出するための検出抵抗1と、周囲の温度環境の変化に影響されることなく検出抵抗1に流れる電流に応じたモニター電流を出力する電流出力増幅器6と、モニター電流を電圧に変換して出力する抵抗16と、周囲の温度環境の変化に影響されることなく一定の電流を出力する電流源7と、電流源7により出力された電流に基づき基準電圧を出力する抵抗17と、基準電圧を基準としモニター電圧をA/D変換して負荷2に流れる電流の検出電流値を出力するA/D変換器10とを備える。

(もっと読む)

送信装置

【課題】スルーレートを改善することができる送信装置を提供する。

【解決手段】送信装置1は、データ変換回路11,駆動回路20,主出力バッファ回路31および副出力バッファ回路32を備える。駆動回路20は、EN信号が非有意値であるときにスイッチSW31,SW32,SW41,SW42,SW30及びSW40をオフ状態とし、EN信号が有意値であるときにスイッチSW30およびスイッチSW40をオン状態とし、DIN信号がHレベルであってEN信号が有意値であるときにスイッチSW31及びSW42をオン状態とするとともにスイッチSW32及びSW41をオフ状態とし、DIN信号がLレベルであってEN信号が有意値であるときにスイッチSW31及びSW42をオフ状態とするとともにスイッチSW32及びSW41をオン状態とする。

(もっと読む)

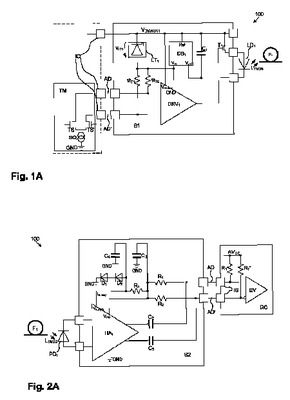

TMDS符号化信号を伝送する回路装置及び方法

少なくとも部分的に、特に少なくともタイムスロット方式でTMDS符号化され、且つ特に少なくとも1つのDVIデータ接続、及び/又は、少なくとも1つのHDMIデータ接続に割り当てられた信号を、少なくとも1つのデータソースから少なくとも1つのデータシンクへ安価に伝送する回路装置(100;100’)及び方法を提供するために、

駆動回路(S1;S1’)は、上流に接続され且つ前記データソースに割り当てられた少なくとも1つの接続インターフェース(IQ)によって、約5ボルトの供給電圧を含み、特に約55ミリアンペア以下でチャージすることができる、供給電圧(VDVI/HDMI)を供給されること、

前記駆動回路(S1;S1’)の下流に接続された少なくとも1つの発光素子(LD1)、特に少なくとも1つの光ダイオード、少なくとも1つの発光ダイオード、少なくとも1つのレーザダイオード、あるいは少なくとも1つの半導体レーザを含む少なくとも1つのレーザによって、電気的なTMDS符号化信号を電気−光変換して、前記TMDS符号化信号を与えられた光(LTMDS)として、少なくとも1つの光ファイバー(F1)、特に少なくとも1つのガラス繊維又は少なくとも1つのプラスチックファイバーを含む少なくとも1つのプラスチック材料繊維に、連結すること、

少なくとも1つのTMDSトランスミッタ(TM)からデータソースに割り当てられた前記接続インターフェース(IQ)へ供給される直流電流部分は、前記駆動回路(S1;S1’)によって前記発光素子(LD1)を制御する変調信号電流に変換されること、

前記TMDS符号化信号を与えられた前記光(LTMDS)は、少なくとも1つの光吸収素子(PD1)、特に少なくとも1つのフォトダイオードによって、前記光ファイバー(F1)から取り出されて、光−電気変換され、前記光吸収素子(PD1)の下流且つ前記データシンクに割り当てられた少なくとも1つの接続インターフェース(IS)の上流に接続された少なくとも1つのトランスインピーダンス変換回路(S2;S2’)に供給され、前記トランスインピーダンス変換回路(S2;S2’)は、少なくとも1つの差動ペア配線(AD、AD’)によって印加される直流電圧部分によって提供されることが提案される。  (もっと読む)

(もっと読む)

スイッチング制御回路

【課題】ハーフブリッジ回路を構成する2つのスイッチング素子を共にオンさせるような2つのパルス信号が入力された場合であっても、2つのスイッチング素子が同時にオンすることを確実に防止すること。

【解決手段】第1パルス信号と第2パルス信号に基づいて、第1出力端子(DRV1)4からP型MOSFET(MOS1)10に第1駆動信号が出力され、第1パルス信号と第2パルス信号に基づいて、第2出力端子(DRV2)5から第2スイッチング素子であるN型MOSFET(MOS2)11に第2駆動信号が出力されるように構成され、保護回路20によりP型MOSFET(MOS1)10及びN型MOSFET(MOS2)11のうちの少なくとも一方がオフされるようにした。

(もっと読む)

スイッチング制御回路及びスイッチング電源装置

【課題】スイッチング電源装置の入力リップルを特に操作することなくPWM基本周波数を変動させる。

【解決手段】スイッチング素子(201)は、スイッチング電源装置における変圧器(13)への一次電流の供給を制御する。増幅回路(202)は、変圧器(13)の補助巻線の出力リップルを増幅する。ゆらぎ生成回路(203)は、増幅回路(202)の出力に基づいてゆらぎ信号を生成する。基本信号発生回路(204)は、周波数がゆらぎ信号に応じて変動するPWM基本信号を生成する。制御回路(210)は、PWM基本信号を受けたとき、スイッチング素子(201)をオン制御し、スイッチング電源装置の出力帰還に基づくオフ信号を受けたとき、スイッチング素子(201)をオフ制御する。

(もっと読む)

ドライバ回路、及び電子回路装置

【課題】基準電流に対して所定の比の負荷電流を高い精度で得るドライバ回路を提供する。

【解決手段】MOSトランジスタM3のドレイン端子には二つの抵抗R1及びR2が接続されており、その他端には夫々電流発生装置IREF、負荷LOADが接続されている。両抵抗値は同値であるとする。またトランジスタM3のドレイン端子と両抵抗との接続部を接続点Aとする。この電子回路装置は抵抗R1と電流発生装置IREFとの接続部を接続点B、抵抗R2と負荷LOADとの接続部を接続点Cとして、夫々差動増幅器A1の入力端子へ接続したものである。該差動増幅器において、トランジスタM3のゲート端子に出力端子、つまり制御入力端子が接続されることを特徴とする。その接続部を接続点Gとする。該差動増幅器は接続点BおよびCの電位差を帰還する回路として機能する。

(もっと読む)

サンプルホールド集積回路、サンプルホールド回路において漏れを補償する方法、および集積回路で用いられるサンプリング回路

【課題】サンプリングされた値を長時間キャパシタに保持し、かつ蓄積された値に対するスイッチ漏れ電流の影響を実質的に減少させるための方法および装置を提供する。

【解決手段】サンプルホールド回路は、一局面において、第1および第2のスイッチを含む。第1のスイッチは、入力信号を受けて、第1のキャパシタを用いて入力信号をサンプリングするために結合されることができる。第1の漏れ電流は、第1のスイッチの第1および第2の導電性端子の間を流れ、第1の漏れ電荷として第1のキャパシタに蓄えられる。第2の漏れ電流は、第2のスイッチの第1および第2の導電性端子の間を流れ、第2の漏れ電荷として第2のキャパシタに蓄えられる。オフセット回路は、保持されサンプリングされた信号に応答して発生する信号および第1のスイッチを介して蓄えられた電荷からある量を減算することによって、補償されサンプリングされた値を生成し、ある量は、第2のキャパシタの蓄えられた漏れ電荷に応答して発生する。

(もっと読む)

半導体集積回路装置

【課題】本発明は、コストアップを抑制でき、かつ、異常履歴を得ることができる半導体集積回路装置を提供することを目的とする。

【解決手段】発振を行って発振信号を出力すると共に発振停止を検出したとき発振停止検出信号を出力し発振を再開する発振回路と、発振回路が出力する発振停止検出信号をエラーフラグとして保持するレジスタと、発振回路が出力する発振停止検出信号からリセット信号を生成して機能モジュールをリセットするリセット制御部と、機能モジュールのリセット後、レジスタからエラーフラグを読み出して不揮発性メモリに記憶する記憶制御手段を有する。

(もっと読む)

過電流検出回路

【課題】過電流検出値の誤差が小さい過電流検出回路を提供すること。

【解決手段】本発明にかかる過電流検出回路は、負荷への電源供給を制御するトランジスタQ1の制御電圧に応じて電流値が制御されるトランジスタQ2と、Q2の電流値に応じて電位差が制御される電位差設定部と、電位差設定部により制御されるゲート−ソース間の電位差に応じて電流値が制御されるトランジスタQ4を備える。さらに電位差設定部は、電源電圧がドレインに印加され、ゲート及びソースがQ4のゲートに接続されたデプレション型トランジスタQ6と、ドレイン及びゲートがQ6のゲート及びソースとQ4のゲートとの接続点に接続されたトランジスタQ3と、Q4のソースとQ3のソースの電流経路上に設けられ、ゲート及びドレインがQ2のソースに接続され、ソースが外部出力端子に接続されたデプレション型トランジスタQ5を有する。それにより過電流検出値の誤差を小さくできる。

(もっと読む)

ヒューズ装置

【課題】切断したヒューズにグローバックが発生した場合にも、正確なヒューズデータを生成し得るヒューズ装置を提供する。

【解決手段】切断したグローバック検出用ヒューズf0の抵抗値と、第一の基準抵抗R0の抵抗値の差に基づく検出信号Xを生成するグローバック検出部11と、検出信号Xに基づいて抵抗値が変化する第二の基準抵抗TN9の抵抗値と、ヒューズデータ生成用ヒューズf1,f2,fnの抵抗値との比較結果をヒューズデータDAとして出力するヒューズ部13aとを備えた。

(もっと読む)

サンプルホールド回路、ドライバ、電気光学装置、及び電子機器

【課題】回路の大規模化を抑えながら適正な位相補償を実現する。

【解決手段】演算増幅器OP1と、サンプルホールド回路の入力ノードNIと、接続ノードNSとの間に設けられたサンプリング用スイッチ素子SSと、接続ノードと、演算増幅器の第1の入力端子のノードであるサミングノードNEGとの間に設けられたサンプリング用キャパシタCSと、演算増幅器の出力端子とサミングノードとの間に設けられた帰還用スイッチ素子SFと、接続ノードと、演算増幅器の出力端子との間に設けられたフリップアラウンド用スイッチ素子SAと、サンプリング用キャパシタのサミングノード側の端子NCと演算増幅器の出力端子との間に設けられた位相補償用抵抗素子RPと、を含む。

(もっと読む)

レベルシフト回路、スイッチング素子駆動回路及びインバータ装置

【課題】レベルシフト回路のdv/dt等に起因するコモンモードノイズによる誤判定を抑制し、ロバスト性の高いスイッチング素子駆動回路及びインバータ装置を提供する。

【解決手段】レベルシフト回路のオフセットが設けられたセット用負荷の信号レベルとリセット用負荷との信号レベルとを比較し、セット用負荷のレベルがリセット用負荷のレベルに比べ前記オフセットより低くなったことを判定して前記セットパルスを検出する

(もっと読む)

電流駆動回路

【課題】各画素において負荷のばらつきがあっても、各画素の負荷に対して速やかに所望の駆動電流値を書き込む。

【解決手段】定電流源回路20は、負荷10に駆動電流Idataを供給する。出力電圧差増幅回路30は、所定期間内において負荷駆動端に生ずる電圧変化量を検出し、該電圧変化量に対応した電流または電圧を所定期間とは別の期間において負荷10に供給する。出力電圧差増幅回路30は、電圧変化量の検出と、電流または電圧の負荷10への供給とを時間的に繰り返す。

(もっと読む)

サンプル・ホールド回路及びデジタルアナログ変換回路

【課題】電荷分配を行う容量の容量値が小さくても、アンプの入力容量による出力誤差が小さい、高精度出力のサンプル・ホールド回路、シリアルDACの提供。

【解決手段】第1のスイッチ110を介して接続された第1及び第2の容量素子C11,C12と、差動回路と、を備え、前記差動回路は、差動入力対の第1入力が、前記第1の容量素子の一端N11に第2のスイッチ121を介して接続され、第2入力が、前記第2の容量素子の一端N8に接続された差動入力段と、前記差動入力段の出力を入力に受け、出力がサンプル・ホールド回路の出力端子N9に接続されるとともに、第3のスイッチ122を介して、前記差動入力段の前記第1入力に接続される増幅段16と、を備えている。

(もっと読む)

リセット信号生成回路

【課題】電源電圧が変動したときに不完全な短いパルスのリセット信号が出力されることを防止するリセット信号生成回路を提供する。

【解決手段】ノードBはパワーオンリセット時にはハイレベル、動作時にはローレベルである。動作時に電源(Vcc)が変動してノードCが一瞬でもハイレベルになるとスイッチ素子MN50がオンし、ノードBをローレベルに引き下げ、安定したローレベルのリセット信号RST1を出力する。ノードBがローレベルになるとスイッチ素子MN51は遅延してオフになり、容量104と105は充電回路112により徐々に充電される。ノードBの電位がインバータ回路106のスレッシュホールドレベルを超えるとリセット信号RST1はハイレベルに戻りリセットが解除され、スイッチ素子MN50はオフ、スイッチ素子MN51はオン状態に戻る。

(もっと読む)

161 - 180 / 454

[ Back to top ]