Fターム[5J055EZ03]の内容

Fターム[5J055EZ03]に分類される特許

101 - 120 / 454

半導体装置

【課題】省電力化および信頼性の向上、または小面積化を実現可能な半導体装置を提供する。

【解決手段】電源遮断が行われない内部電源Vint0と電源遮断が行われる内部電源Vint1との間を接続する電源スイッチSWと、電源遮断が行われる内部電源Vint1の電圧を判定する内部電圧判定回路VINTDETを設ける。電源遮断が行われる内部電源Vint1は、外部電源Vextからレギュレータ回路VREGを用いて生成する。Vint1の電源遮断時は、SWをオフにし、VREGのオフおよびVREG出力の接地電位GNDへのショートを行い、Vint1の電源復帰時は、VREGのオンおよびショートの解除を行い、上昇したVint1の電圧をVINTDETで判定した上で回路ブロックBLK1の動作開始およびSWのオンを行う。

(もっと読む)

負荷駆動制御装置

【課題】消費電力を抑えつつ、高輝度で安定した駆動を得るとともに駆動制御回路全体の寿命を向上させる。

【解決手段】負荷20に接続される駆動制御部10を備え、駆動制御部10は、負荷20の定格電流値IFと、パルス駆動したときの絶対最大定格電流値Imaxから予め設定されたピーク電流値Ipに基づいてパルス幅変調することで、負荷20のオン期間を規定した第1のオン/オフ周期による第1駆動パルスP1を生成し、第1のオン/オフ周期のオン期間の中でさらにスイッチングさせることで、パルスの最大振幅がIpとなるように、第2のオン/オフ周期による第2駆動パルスP2を生成する定電流パルス駆動部14とを備え、第2駆動パルスP2によって駆動された電流を前記負荷20に印加することによって、負荷20を連続的に駆動させるとともに、充放電制御部15のキャパシタンスC1を信頼性寿命の高いセラミックコンデンサーを使用した。

(もっと読む)

電子回路

【課題】

内部電源回路からの内部電源電圧が安定状態となり、レベルシフタの入力が適正となった後に、レベルシフタを活性化させるパワーダウンモードの復帰シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧からシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する内部回路30と、入出力回路24と、内部回路からの信号を入力し、電源電圧の電圧レベルに変換し入出力回路へ出力するレベルシフタ23と、レベルシフタを制御する制御回路40とを備え、システム電圧発生回路10が停止状態から動作状態へ移行するとき、制御回路は内部回路が動作状態であることを判定する第1の判定手段41と、システム電圧が所定値に達したか、または所定値に収束したかを判定する第2の判定手段42とを備え、双方の判定手段の結果に基づいてレベルシフタを活性化する構成とした。

(もっと読む)

高電圧差動信号方式のためのドライバ回路

高電圧差動信号方式のためのドライバ回路(200)。この回路は、入力に応答して第1の出力で第1の正の遷移を生成する第1の正のドライバ(205A)を含む。この回路は更に、第1の正のドライバに結合され、電流の生成を可能にする第1の電流要素(210A)を含む。更に、この回路は、第1の電流要素(210A)に結合され、第1の電流要素に起因して、入力及び電流に応答して、第1の正の遷移の速度に類似する速度で、第2の出力で第1の負の遷移を生成する、第1の負のドライバ(215A)を含む。  (もっと読む)

(もっと読む)

出力バッファ回路

【課題】出力遅延を短縮できる出力バッファ回路を提供する。

【解決手段】信号PenがLレベルからHレベルに切り替わり信号NenがHレベルからLレベルに切り替わった直後において、定電流源Is1が追従しきれずまた切り替わっていない場合には、ノードPは未だHレベルのままであるので、ノードOUTはLレベルのままである。この状態で、切り替え前にHレベルのノードNに接続されていたノードAは、切り替えによりHレベルのノードPへ接続される。これと同時に、インバータinv3の出力部がHレベルからLレベルに切り替わっているので、キャパシタC2を介して、ノードAもHレベルからLレベルに切り替えられる。このとき、ノードPの電位はノードAと等しくなるまで引き下げられ、Lレベルへ遷移する。

(もっと読む)

駆動電圧制御装置

【課題】演算増幅器の能力を高めても、液晶パネルの負荷回路の時定数以上の速度で駆動できない。

【解決手段】出力切替スイッチSxが、負荷回路2に正極側の負荷駆動電圧を供給する正極側のバッファの出力を選択したとき、負極側のバッファの出力端子と負極側の負荷駆動電圧よりも低い負極側のブースト電圧の電源との間に介挿された負極側の昇圧制御スイッチTR2がオンする一方、負極側の入力信号をインピーダンス変換して負荷回路2に負極側の負荷駆動電圧を供給する負極側のバッファの出力を選択したとき、正極側のバッファの出力端子と正極側の負荷駆動電圧よりも高い正極側のブースト電圧の電源との間に介挿された正極側の昇圧制御スイッチTR1がオンするように、タイミング制御部3が制御する。

(もっと読む)

プリエンファシス機能を含む出力回路と半導体装置

【課題】プリエンファシス機能を有する出力回路において、デエンファシス時における差動出力信号のコモンモード電圧のプリエンファシス時のコモンモード電圧からの変動を抑制する。

【解決手段】入力信号とその相補信号とを差動入力して差動出力し、差動出力信号のうち高電位側の出力信号にデエンファシスをかける際に、当該デエンファシス電流を供給するトランジスタ(N3、N4)に流れる電流を絞る回路(N5、N6、R3)を備え、デエンファシス時の前記出力信号のハイレベルの前記出力信号のプリエンファシス時のハイレベルからの変化量を縮減させ、デエンファシス時の前記差動出力信号のコモンモード電圧をプリエンファシス時のコモンモード電圧に近づける。

(もっと読む)

送信ドライバ回路

【課題】フリーホイールダイオードを用いることなく、より低い電圧のアンダーシュートでも低減できる送信ドライバ回路を提供する。

【解決手段】PチャネルMOSFET22のドレインをグランドに接続して、NチャネルMOSFET21,PチャネルMOSFET22のソースをそれぞれ信号線3H,3Lに接続する。第1データ電圧設定部41は、信号出力部がハイレベル信号を出力すると、ゲート21G,22G間の電位差を(2・R1・Iref)にする電圧信号を設定し、第2データ電圧設定部42は、信号出力部がロウレベル信号を出力すると、ゲート21G,22G間の電位差をゼロにする電圧信号を設定する。これらの作用により、伝送線路3を構成する信号線3H,3L間の電圧を変化させて差動信号を伝送する。

(もっと読む)

液晶表示装置のソースドライバー回路

【課題】 本発明は、液晶表示装置のソースドライバー集積素子でパワードロップに対する復帰時間を縮める技術を提供する。

【解決手段】本発明によってソースドライバーに適用されるガンマバッファー回路では、差動増幅部と電流ミラー部のモストランジスターらを直接連結しないでダイオード結合型モストランジスターを通じて連結した。これによって、出力端のモストランジスターのゲートの動作範囲がダイオード結合型モストランジスターのドレッシーホールド電圧程度減るようになる。これによって電源端子電圧ドロップ後復帰時間及び接地端子電圧バウンシング後に復帰時間が減って、入力トランジスターのマッチング特性が改善されて、これによってランダムオフセットが低減される。

(もっと読む)

電圧変化検知装置

【課題】電界効果トランジスタの閾値電圧がばらついた場合にも、検知電圧のばらつきを低減でき、所望の電圧検知範囲で電圧変化を検知することができる電圧変化検知装置を提供する。

【解決手段】ドレインが電源電位に接続され且つソースが第1のノードにおいて第1の定電流源又は第1の抵抗に接続され且つゲートが固定電位に接続されている第1の電界効果トランジスタと、ドレイン及びゲートが電源電位に接続され且つソースが第2のノードにおいて第2の定電流源又は第2の抵抗に接続されている第2の電界効果トランジスタと、当該第1のノードの電位と当該第2のノードの電位との比較結果に応じて電源電位が所定の検知電位を跨いで変化したことを検知した旨の検知信号を生成する検知信号生成部と、を含む電圧変化検知装置。

(もっと読む)

出力バッファ回路、入力バッファ回路、及び入出力バッファ回路

【課題】スルーレートを適切に調整可能なバッファ回路を提供する。

【解決手段】

CMOS出力バッファ回路は、バッファ回路Buffer[1]〜[4]を備えている。各バッファ回路は、電源電圧端子又は接地端子と出力端子との間にトランジスタPO及びNOを有している。各バッファ回路中の複数個のトランジスタPO及びNOは、外部からの制御信号に従い選択的に動作可能な状態とされる。各バッファ回路中の3個のトランジスタPOは、所定のサイズ比を有するように形成されている。

(もっと読む)

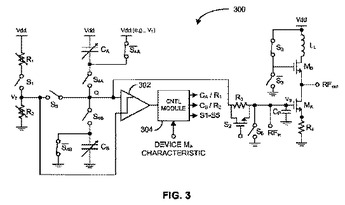

アクティブデバイスをバイアスするシステム及び方法

アクティブデバイスに対するバイアス電圧を発生する装置が開示され、第1の電圧源と、第1の電圧源に応答してチャージを発生するように適応されたキャパシティブエレメントと、アクティブデバイスに対するバイアス電圧を発生するためにチャージを供給するように適応された第1のスイッチングエレメントとを備える。本装置は、アクティブデバイスの1以上の特性に基づいてキャパシティブエレメントをコントロールするように適応されコントローラを備えるかもしれない。コントローラは、リファレンス電圧に基づいて、すなわちアクティブデバイスの1以上の特性に基づいて前記キャパシティブエレメントのキャパシタンスをコントロールかもしれない。  (もっと読む)

(もっと読む)

スイッチトキャパシタ型積分器

【課題】待機電流を抑制することによって、低消費電力のスイッチトキャパシタ型積分器を実現する。

【解決手段】φ1において入力信号の電荷をサンプリングするサンプルキャパシタC1と、φ2においてサンプルキャパシタC1の電荷を仮想ノード4を介して累積する蓄積キャパシタC2と、蓄積キャパシタC2にサンプルキャパシタC1の電荷を供給する主トランジスタMP1,MN1と、主トランジスタMP1,MN1のゲート端子と仮想接地ノード4の間に挿入された校正キャパシタC3,C4と、φ1において校正キャパシタC3,C4に対して、仮想ノード4が基準電位Vcmにあるときの主トランジスタMP1,MN1のゲート・ソース間電圧が略閾値電圧となる電位差が生じるように電荷を供給する校正装置12と、を有する。

(もっと読む)

電圧検出回路

【課題】コンパレータの動作電圧と抵抗で分圧して生成した電圧の立ち上げ順序の制約をなくすることができる電圧検出回路を提供すること。

【解決手段】第一監視端子の電圧(VIN)が低下して第一の検出電圧より小さい場合に出力が反転する第一の電圧検出回路1と、第二監視端子の電圧VDD2が低下して第二の検出電圧より小さい場合に出力が反転する第二の電圧検出回路2とを有する電圧検出回路4であって、第一の検出電圧は第二の検出電圧よりも高く、第二の検出電圧は第一の電圧検出回路の最低動作電圧よりも大きく、かつ、第二の電圧検出回路により第二監視端子の電圧が第二の検出電圧より小さいことを検出した場合に、第二の電圧検出回路の出力信号(検出信号)により第一の検出回路の出力端子の出力の論理を固定する手段(Nchトランジスタ19)を設けた。

(もっと読む)

ドライバ回路

【課題】差動入力信号の振幅中心電圧が高い場合でも、差動出力信号の振幅変動やジッタを抑制することができるドライバ回路を提供することである。

【解決手段】本発明にかかるドライバ回路は、トランジスタM1と、トランジスタM1のソースと電源端子との間に接続された負荷素子R1と、トランジスタM1とカレントミラー回路を構成するトランジスタM2と、入力された差動入力信号に応じた差動出力信号を出力すると共に、トランジスタM2によりソースにバイアス電流が供給される一対のトランジスタを備える差動対と、トランジスタM2のソースと電源端子との間に接続された負荷素子R2と、非反転入力端子がトランジスタM1のソースと接続され、反転入力端子がトランジスタM2のソースと接続され、出力が差動対を構成する一対のトランジスタのバックゲートに接続されたオペアンプAMP1と、を有する。

(もっと読む)

電流制御用半導体素子およびそれを用いた制御装置

【課題】電流検出回路におけるゲインaおよびオフセットbの変動を補正して、1チップのIC内で高精度な電流検出が可能な電流制御用半導体素子およびそれを用いた制御装置を提供することにある。

【解決手段】電流制御用半導体素子100は、同一半導体チップ上に、MOSFET100Hと、2つの定電流源Ic1,Ic2と、MOSFETの電流および定電流源の電流を検出する電流検出回路120とを備える。さらに、定電流源は、その電流値を計測するための外部接続端子T5を備える。補正用測定値保持レジスタ145は、外部から測定した定電流源の電流値を保持する。

(もっと読む)

チャージポンプ回路

【課題】短時間で出力電圧が昇圧規定電圧に達し、その後は小さいリップル幅を有するチャージポンプ回路を提供する。

【解決手段】チャージポンプ回路100は、制御部10と発振回路20と昇圧部30とを有する。発振回路20は、予め定められた周期のパルス信号を出力する。昇圧部30は、電圧を昇圧する複数個の昇圧回路を備え、制御部10が出力する昇圧信号に応じて電荷量を出力する。制御部10におけるコンパレータ回路13は、昇圧部30から出力される電圧と、予め定められた規定電圧とを比較し、比較結果に応じて昇圧信号Cont4〜Cont1を出力し、昇圧部30からの供給電荷量を制御する。

(もっと読む)

半導体集積回路

【課題】PKGの設計期間を遅延させることなくクロストーク耐性を向上させることが可能な半導体集積回路を提供する。

【解決手段】複数の信号配線を有するChip20において、一の信号配線と前記一の信号配線に隣接する一方の隣接信号配線と前記一の信号配線に隣接する他方の隣接信号配線との間で生じるクロストークの発生量を抑制するための補正係数31と、前記一の信号配線に送出される一の信号、前記一方の隣接信号配線に送出される一方の隣接信号、および前記他方の隣接信号配線に送出される他方の隣接信号の組み合わせパターンと、に基づいて、前記一の信号のスルーレートの低減度合を示す補正量を演算する補正量演算部42a〜42cと、前記補正量に基づいて、前記一の信号のスルーレートを調整するドライバ41a〜41cと、を備える。

(もっと読む)

駆動装置、及び表示装置

【課題】並列接続された複数の出力アンプ回路において所望の駆動能力を実現することができる駆動装置、及び表示装置を提供すること。

【解決手段】本発明に係る駆動装置(ソースドライバ1)は、並列接続された複数の出力アンプ回路10と、複数の出力アンプ回路10に、バイアス電圧供給源25からバイアス電圧を供給するバイアス配線(幹バイアス配線22)と、複数の出力アンプ回路10に、電源電圧供給源35から電源電圧を供給する電源配線31と、複数の出力アンプ回路10に供給される電源電圧とバイアス電圧との差が所望となるように、バイアス電圧にオフセット電圧を重畳する補正手段(バッファ26)とを備えた。

(もっと読む)

サンプリングミキサ回路

【課題】サンプリングパルスの周波数を高めたりデューティ比を特別に絞り込むことなく実効的にデューティ比の小さいサンプリングパルスを得ることができ、従って、高域までの周波数特性に関する要求水準が緩和されたサンプリングミキサ回路を提供する。

【解決手段】サンプリングに適用する各キャパシタC1〜C4の充電経路となる各電流パス113−1,113−2,113−3,113−4を第1スイッチおよび第2スイッチの直列接続回路を含むように構成し、これら各電流パスが所定の各位相差で順次周期的に導通すると共に各電流パス毎の第1および第2スイッチが所定の位相差でオンになる多相のサンプリングパルスを各対応する第1スイッチおよび第2スイッチに供給することによって、各電流パスにおける導通状態の繰り返しに関するデューティ比が上記サンプリングパルスのデューティ比よりも小さくなるようにする。

(もっと読む)

101 - 120 / 454

[ Back to top ]