Fターム[5J055GX06]の内容

Fターム[5J055GX06]に分類される特許

101 - 120 / 559

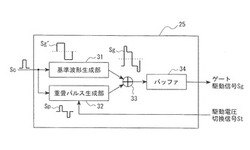

ゲート駆動回路及びゲート駆動方法

【課題】トランジスタの駆動電力の損失を防ぎ且つスイッチング時間の高速化を図る。

【解決手段】接合型トランジスタ2の駆動に必要な基準駆動能力レベル電圧からなる基準波形Sg′及び駆動能力のより高い高駆動能力レベル電圧からなる重畳パルスSpを生成し、重畳パルスSpのパルス幅を、接合型トランジスタ2のスイッチング時間に、若しくはドレイン電位VDの遷移収束タイミングを表す閾値により設定する。基準波形Sg′と重畳パルスSpとを重畳しこれを、接合型トランジスタ2のゲート駆動信号Sgとする。ゲート駆動信号Sgは、接合型トランジスタ2の遷移終了とみなすことの可能なタイミングで基準駆動能力レベル電圧に切り換わることになるため、遷移終了後も高駆動能力レベル電圧で駆動されることにより、接合型トランジスタ2に形成されるダイオードに順方向電流が流れることに伴う電力損失の発生を回避することができる。

(もっと読む)

高周波半導体スイッチ装置

【課題】スイッチの切替時間を短縮できる高周波半導体スイッチ装置を提供する。

【解決手段】制御回路は、負電圧発生回路に接続されるとともに、出力ノードが高周波スイッチ回路に接続され、高周波スイッチ回路に供給するローレベルの制御信号として負電位の信号を供給するレベルシフト回路を有し、出力ノードに蓄積されている電荷を、レベルシフト回路が動作する前に放電させる。

(もっと読む)

スイッチ素子駆動回路

【課題】小型化及びコストダウンを図ることができるスイッチ素子駆動回路を提供する。

【解決手段】スイッチ素子駆動回路10は、スイッチ素子1のゲート電極1gに二次巻線n2が接続されたトランス11と、トランス11の一次巻線n1に電流が流れるオン期間と一次巻線n1に電流が流れないオフ期間を交互に設けて、スイッチ素子1をオン/オフさせる制御回路12を備える。制御回路12は、オン期間に一次巻線n1に流れる電流に基づいて、スイッチ素子1に接続された負荷状態をモニタし、負荷状態に応じて二次側に供給する出力を制御する。

(もっと読む)

スイッチ素子駆動回路

【課題】小型化及びコストダウンを図ることができ、且つ、スイッチ素子のオン状態が不十分な状態となるのを抑制できるスイッチ素子駆動回路を提供する。

【解決手段】スイッチ素子駆動回路10は、スイッチ素子1のゲートが二次巻線n2の両端間に接続されたトランス11と、トランス11の一次巻線n1に電流が流れるオン期間と一次巻線n1に電流が流れないオフ期間を交互に設けて、スイッチ素子1をオン/オフさせる第1制御回路12と、スイッチ素子1に流れる電流が、二次巻線n2の両端電圧に対応する設定値に等しくなるように、ゲートに印加する印加電圧を制御する第2制御回路13を備える。

(もっと読む)

高周波回路、高周波部品及び通信装置

【課題】 異なる通信システムに対応可能で、受信感度が高く送信電力の損失が抑制された高周波回路、高周波部品及びこれを用いた通信装置を提供する。

【解決手段】 第1及び第2のアンテナ端子と、第1の通信システム用の送信端子並びに第1及び第2の受信端子と、前記第1及び第2のアンテナ端子を選択して前記送信端子と接続するスイッチ回路を少なくとも備えた高周波回路であって、前記スイッチ回路と第1のアンテナ端子をつなぐ信号経路と、前記スイッチ回路と第2のアンテナ端子をつなぐ信号経路のそれぞれに整合回路を配置したことを特徴とする。

(もっと読む)

負荷駆動回路の保護装置

【課題】FET(T1)のドレイン電流IDが急激に増加し、電圧Vdsが増加する過渡期間であっても、FET(T1)の温度上昇量を忠実に示す信号を生成することが可能な負荷回路の保護装置を提供する。

【解決手段】FET(T1)の両端に生じる電圧Vdsに比例する電流Iaを流す電流変換回路21と、この電流Iaを通電するインピーダンス回路22を備える。そして、FET(T1)の過渡熱抵抗の時間に対する変化を示す関数を過渡熱関数Rth(t)としたとき、FET(T1)に、ゼロから階段状に増加する電流を通電した際に、インピーダンス回路22の点P2に生じる電圧V5が、過渡熱関数Rth(t)の平方根に比例した電圧となるように、前記インピーダンス回路のインピーダンスを設定する。そして、電圧V5が判定電圧V6を上回った場合に、FET(T1)を遮断して負荷駆動回路を過熱から保護する。

(もっと読む)

スイッチ回路装置

【課題】従来技術によるスイッチ回路装置では、ドライバ回路がアンテナ端子とポートとの間に振幅の大きい高周波信号を入力した際に、ドライバ回路内部でリーク電流が発生し、スイッチ回路装置の消費電力が増大する、という問題がある。

【解決手段】ドライバ回路の出力部に、リーク電流抑制回路部を設ける。本発明のスイッチ回路装置によれば、リーク電流抑制回路部が高周波信号の侵入を抑制するので、ドライバ回路は出力状態を保持することが出来て、リーク電流の問題が解決される。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】ターンオフ用di/dt帰還部23OFFは、IGBT11Uがターンオフするときに、IGBT11Uのコレクタ電流Icの時間変化に基づいて、帰還電圧VFBを生成する。ターンオン用di/dt帰還部23ONは、IGBT11Uがターンオンするときに、FWD12Dの転流電流IFWDに基づいて、帰還電圧VFBを生成する。この場合、ターンオン用di/dt帰還部23ONは、転流電流IFWの方向が、リバースリカバリー区間に対応する方向、即ち図13に示すFWD12Dのカソードからモータ等の負荷L側に流れる方向である場合、帰還電圧VFBを生成し、それ以外の場合、帰還電圧VFBの生成を禁止する。

(もっと読む)

負荷制御装置

【課題】ノイズ対策用のコンデンサC1を設置した場合であっても過電流を検出するための回路を正常に作動させることが可能な負荷制御装置を提供する。

【解決手段】プラス端子P11とマイナス端子P12より電力が供給されて駆動する制御回路10により、FET(T1)のオン、オフを切り替えて、負荷RLの駆動、停止を制御する場合に、マイナス端子P12とグランドとを接続するアース線に、抵抗R5とダイオードD1の並列接続回路を設ける。従って、入力スイッチSW1の投入時にプラス端子11とマイナス端子12の間に配置されたコンデンサC1の放電電流I2が流れる場合であっても、抵抗R5の電圧降下VR5によりマイナス端子P12の電圧をグランドレベルよりも相対的に低くすることができ、コンデンサC1の両端電圧VC1を拡大させて、放電電流I2を抑制し、電圧V1の低下を抑えることができる。

(もっと読む)

負荷制御装置

【課題】ノイズ対策用のコンデンサC1を設置した場合であっても過電流を検出するための回路を正常に作動させることが可能な負荷制御装置を提供する。

【解決手段】FET(T1)のゲートとドレインとの間に第2のコンデンサC2を設けることにより、点P1の電圧V1が減少した場合に、FET(T1)のゲート電流がコンデンサC2側にバイパスしてFET(T1)に流れ、FET(T1)のゲートに供給される電荷量が低減する。このため、FET(T1)のドレイン電流の増加を抑制でき、電圧V1の急激な変動を防止できる。その結果、比較器CMP1が作動不能となる程度まで電圧V1が低下することを防止でき、比較器CMP1が誤動作することを防止できる。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】di/dt帰還部23は、IGBT11Uがターンオフするときに、IGBT11のコレクタ電流Icの時間変化に基づいて、帰還電圧VFBを生成する。また、di/dt帰還部23は、IGBT11がターンオンするときに、図示せぬFWDの転流電流IFWDに基づいて、帰還電圧VFBを生成する。このようなdi/dt帰還部23は、帰還電圧VFBを駆動信号の電圧の一部として印加するタイミングを遅延させる遅延フィルタとして、LPF回路201を備えている。LPF201の遅延量、即ちインダクタンスLdを適度に調整することで、還流ダイオードの電圧におけるサージ電圧を低減させることができる。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】電子回路1は、IGBT11と、FWD12と、半導体素子駆動回路13と、を備えている。半導体素子駆動回路13は、IGBT11のゲート−エミッタ間の電圧Vgeを可変することによって、IGBT11のターンオン及びターンオフを制御する。半導体素子駆動回路13のdi/dt帰還部23は、電子回路1の主電流であるIGBT11のコレクタ電流Icの時間的変化、即ち時間微分値dIc/dtに基づき帰還電圧VFBを生成し、IGBT11のゲート−エミッタ間の電圧Vgeの一部として加算する。

(もっと読む)

負荷制御装置

【課題】FET(T1)のドレイン電圧の低下量が大きくなった場合であっても過電流を検出するための回路を正常に作動させることが可能な負荷制御装置を提供する。

【解決手段】FET(T1)のゲートとドレインとの間にコンデンサC1を設けることにより、点P1の電圧V1が減少した場合に、FET(T1)のゲート電流がコンデンサC1側にバイパスしてFET(T1)に流れ、FET(T1)のゲートに供給される電荷量が低減する。このため、FET(T1)のドレイン電流の増加を抑制でき、電圧V1の急激な変動を防止できる。その結果、比較器CMP1が作動不能となる程度まで電圧V1が低下することを防止でき、比較器CMP1が誤動作することを防止できる。

(もっと読む)

半導体装置

【課題】従来よりも低消費電力かつ小面積であるとともに設計性のよいパワーオンリセット回路またはスタートアップ回路を備えた半導体装置を提供する。

【解決手段】半導体装置1は、出力部10と、第1および第2の電位設定部8,9とを備える。出力部10は、電源投入時に、中間電位ノードN1の電位に応じた制御信号RSを内部回路3に出力する。第1の電位設定部8は、第1の基準電位ノードVDDと中間電位ノードN1との間に接続された第1の導電型を有するエンハンスメント型の第1のMOSトランジスタEPを含む。第2の電位設定部9は、第2の基準電位ノードGNDと中間電位ノードN1との間に直列接続された第2の導電型を有するディプレッション型の複数の第2のMOSトランジスタDN1_〜DN_nを含む。複数の第2のMOSトランジスタDN1_〜DN_nの各々において、ソースとウェルとが互いに接続される。

(もっと読む)

スイッチ装置

【課題】トランジスタのチャネル部の異常を簡易且つ正確に検出できるスイッチ装置を提供する。

【解決手段】複数の半導体層で形成されて、ゲート電極にゲート電圧を印加されることによってドレイン電極−ソース電極間が導通し、ゲート電圧によって半導体層内で正孔と電子とが結合して発光する電界効果トランジスタ11,12と、ゲート電圧を制御する駆動部21と、トランジスタ11,12の発光量を検出する光検出部231,232とを備え、駆動部21は、光検出部231,232の検出結果に基づいて、トランジスタ11,12の異常を判定し、この判定結果に基づいてゲート電圧を制御する。

(もっと読む)

小型電気機器

【課題】モータの起動時のうなり音を回避し、使用者に不快感を与えることなく使用できる小型電気機器を提供することを課題とする。

【解決手段】DCモータ11の起動時に、DCモータ11の回転数が安定した安定動作時のスイッチングパルス幅と同等のスイッチングパルス幅でスイッチング素子13をスイッチング制御し、DCモータ11が安定動作しているときと同等の駆動電圧をDCモータ11に供給してDCモータ11を起動するように構成される。

(もっと読む)

半導体装置

【課題】ダイオード内蔵IGBTを備えた半導体装置において、ダイオード素子とIGBT素子のゲート信号との干渉を回避してダイオードの順方向損失増加を防止する。

【解決手段】メイン用のダイオード素子22aに流れる電流を電流検出用のダイオードセンス素子22bおよびセンス抵抗30にて検出する。他方、フィードバック回路部40にてセンス抵抗30の両端の電位差Vsがモニタされると共に、当該電位差Vsに基づいてダイオード素子22aに電流が流れているか否かが判定される。そして、ダイオード素子22aに電流が流れていると判定された場合、フィードバック回路部40からIGBT素子21aの駆動を停止させる停止信号がAND回路10に入力され、AND回路10にてIGBT素子21aの駆動が停止される。

(もっと読む)

半導体装置

【課題】コモンノイズを低減する。

【解決手段】半導体装置10は、直列に接続された半導体スイッチング素子11,12と、正極端子13と、負極端子14と、出力端子15とを具備する半導体モジュール16と、半導体モジュール16に絶縁されたボディ17とを備える。ボディ17と、各端子13,15,14およびデバイスとの間の各浮遊容量C1,C2,C3,C0と、ボディ17の浮遊インダクタンスLbと、コモンノイズの電流経路に応じた角速度ωとに対して、

[1/(ω・C1)<{ω・Lb+1/(ω・C0)}]と、[1/(ω・C3)<{ω・Lb+1/(ω・C0)}]と、(C2<C1)と、(C2<C3)とを満たす。

(もっと読む)

半導体装置

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】直列に複数個接続されたそれぞれのMISFETQN1〜QN5のソース領域とドレイン領域の間に、ソース領域の電位を基準としてドレイン領域に正電圧を印加する場合と、ソース領域の電位を基準としてドレイン領域に負電圧を印加する場合のいずれの状態においても、ソース領域の電位とドレイン電極の電位が同電位の状態よりも容量が減少する電圧依存性を持つ歪補償用容量回路CAPC2が接続されている。

(もっと読む)

PWM電力変換装置のデッドタイム補償装置

【課題】デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減することで遅延誤差TDLYを短縮する。

【解決手段】デッドタイム補償部30は、PWMゲート指令Gate_UとPWM出力Vce_Uとの位相差に応じて求めるデッドタイム補償分Vcmp_UでPWM電圧指令Vcmd_Uの電圧値を増減し、この補償後のPWM電圧指令Vcmd_U’をPWM波形発生部20でPWMゲート指令に変換することで、デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減する。

(もっと読む)

101 - 120 / 559

[ Back to top ]