Fターム[5J055GX06]の内容

Fターム[5J055GX06]に分類される特許

61 - 80 / 559

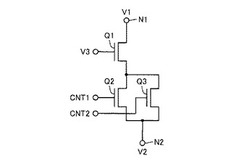

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】ターンオン時間のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された高耐圧、高GmのトランジスタQ1および低耐圧、低GmのトランジスタQ2と、トランジスタQ2に並列接続された低耐圧、高GmのトランジスタQ3とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、低耐圧のトランジスタQ2をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

負荷駆動装置

【課題】クランプ回路が未使用状態なのか断線状態なのかを判別する。

【解決手段】温度センサ1hの出力が入力される温度検出端子14a〜14cを利用し、クランプ回路5a〜5cや温度検出回路7a〜7cの一部がパワーモジュール1に接続されないときには温度検出端子14a〜14cの電位に基づいて温度センサ1hが接続されていない断線無効状態を検出する。例えば、温度検出端子14a〜14cのうち温度センサ1hに接続されない端子に断線検出無効化閾値Vth3以上の電圧を印加することで、温度検出端子14a〜14cが温度センサ1hに接続されていないことを検出する。これにより、クランプ回路5a〜5cに接続されるクランプ端子11a〜11cの電位に基づいて断線検出を行う際に、断線状態なのか断線無効状態なのかを温度検出端子14a〜14cの電位に応じて判定できる。

(もっと読む)

半導体スイッチング素子駆動装置

【課題】半導体スイッチング素子の温度変化によるサージ電圧の発生および変動を抑制すると共にスイッチング損失を低下させることができる半導体スイッチング素子駆動装置を提供する。

【解決手段】各切替スイッチ42a、42bが駆動信号に従ってオン/オフすることにより、駆動手段40が半導体スイッチング素子10の制御端子11に駆動電流を供給する。一方、温度検出手段20によって半導体スイッチング素子10の素子温度または半導体スイッチング素子10の動作環境温度を検出する。そして、駆動手段40は、温度検出手段20によって検出された素子温度または動作環境温度に従って制御端子11に印加する駆動電流の大きさを変更する。これにより、半導体スイッチング素子10の温度変化によるサージ電圧の発生および変動が抑制され、スイッチング損失が低下する。

(もっと読む)

高周波スイッチモジュール

【課題】スイッチポート切替時間が短く、かつ低消費電力、低面積を同時に満たす高周波スイッチモジュールを提供する。

【解決手段】デコーダ3は、前記スイッチポートを切替える制御信号CNTに応答し、スイッチ7を制御するためのスイッチ制御信号SWCNTを生成して、スイッチ切替タイミング検出器は、スイッチ制御信号SWCNTに応答し、スイッチ切替え検出信号t_swを生成し、周波数制御信号生成器は、スイッチ切替え検出信号t_swに応答し、周波数制御信号ICONT、CCONTを生成し、負電圧発生回路は、周波数制御信号ICONT、CCONTに応答し、前記負電圧発生回路内で生成したクロック信号の周波数を2つ以上のそれぞれ異なる周波数に切替つつ、負電圧出力信号NVG_OUTを生成し、スイッチ7は、スイッチ制御信号SWCNTと前記負電圧出力信号NVG_OUTに応答し、複数の高周波信号ポート間の経路を切替える。

(もっと読む)

デジタル入力回路およびシステム監視回路

【課題】消費電力を低減させることを目的とする。

【解決手段】デジタル入力回路の分圧回路11において、システム4からの入力信号が伝搬する信号ラインL1から分岐される分岐ラインL2にスイッチング素子23を設け、このスイッチング素子23をマイクロコントローラ3の動作タイミングに応じてオンオフ制御する。これにより、スイッチング素子23がオフとされている期間において、分圧回路11に流れる電流を遮断でき、消費電力を低減させることが可能となる。

(もっと読む)

ゲートドライブ回路

【課題】簡単な構成で、ワイドバンドギャップ半導体からなるスイッチ素子を駆動するゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体からなるスイッチ素子Q1であって、ドレインとソースとゲートとを有し、ゲートをドライブする信号とゲートとの間にコンデンサと抵抗の並列接続回路を介して接続され、オフ信号期間は、スイッチ素子Q1のゲート・ソース間を短絡するスイッチSW1とを備えることを特徴とするゲートドライブ回路。

(もっと読む)

パワーオンリセット回路

【課題】パワーオン時における回路電源電圧の変化の緩急に拘らず、非動作電圧から動作電圧へ変化時にリセット信号を確実に出力するパワーオンリセット回路を提供する。

【解決手段】本発明に係るパワーオンリセット回路は、回路電源電圧を受けて充電を行う充電回路と、回路電源電圧を受けて出力電圧を出力する動作電圧設定回路と、前記充電回路の出力する充電電圧、及び、前記動作電圧設定回路の出力する出力電圧を判定して、パワーオンリセット信号を出力する電圧判定回路とを備える。

(もっと読む)

窒化物半導体装置

【課題】駆動回路への要求を緩和した使いやすい高速動作の窒化物半導体装置を提供する。

【解決手段】実施形態によれば、窒化物半導体を含む、nチャンネル型の第1〜第4トランジスタと、抵抗と、を備えた窒化物半導体装置が提供される。第1トランジスタは、第1ゲートと、第1ソースと、第1ドレインと、を有する。第2トランジスタは、第2ゲートと、第1ゲートと接続された第2ソースと、第2ドレインと、を有する。第3トランジスタは、第3ゲートと、第1ソースと接続された第3ソースと、第1ゲート及び第2ソースと接続された第3ドレインと、を有する。第4トランジスタは、第3ゲートと接続された第4ゲートと、第1ソース及び第3ソースと接続された第4ソースと、第2ゲートと接続された第4ドレインと、を有する。抵抗の一端は第2ドレインと接続され、他端は第2ゲート及び第4ドレインと接続される。

(もっと読む)

半導体スイッチ回路

【課題】入出力端子におけるアイソレーション劣化を抑制可能とする。

【解決手段】

第1の入出力端子51と第2の入出力端子52間に第1の単位スイッチ101が、第1の入出力端子51と第3の入出力端子間53に第2の単位スイッチ102が、それぞれ設けられ、第2の入出力端子52とグランドとの間に第1のシャントスイッチ103及び第1のDCカットコンデンサ49が、第3の入出力端子53とグランドとの間に第2のシャントスイッチ104及び第2のDCカットコンデンサ50が、それぞれ直列接続され、第1及び第2の単位スイッチ101,102を構成する第1乃至第4のFET1〜4のゲート・ドレイン間には、それぞれ付加容量41〜44が接続されると共に、第1の単位スイッチ101に対して第1の端子間連絡用抵抗器31が、第2の単位スイッチ102に対して第2の端子間連絡用抵抗器32が、それぞれ並列接続されたものとなっている。

(もっと読む)

ゲート駆動回路

【課題】本発明は素子のスイッチング特性を改善したゲート駆動回路に係り、素子のスイッチング特性を任意に決定でき、十分な短絡耐量と、定常損失の抑制ができるゲート駆動回路を提供することを目的とする。

【解決手段】パワースイッチング素子のゲートのオン動作を行うオン動作回路を備える。該オン動作回路は、該ゲートへの入力を第一所定値以下に保つ上限リミット部を備えることを特徴とする。

(もっと読む)

半導体スイッチ及び無線機器

【課題】端子切替時の歪みの増加を抑制した半導体スイッチ及び無線機器を提供する。

【解決手段】実施形態によれば、電源回路と、駆動回路と、スイッチ部と、補正回路と、を備えた半導体スイッチが供給される。前記電源回路は、電源電位と異なる第1の電位を生成する。前記駆動回路は、前記第1の電位と異なる第2の電位と前記第1の電位とが供給され、端子切替信号に基づいて前記第1の電位及び前記第2の電位の少なくとも一方を出力する。前記スイッチ部は、前記駆動回路の出力に応じて共通端子と高周波端子との接続を切り替える。前記補正回路は、前記端子切替信号の変化を検出し、前記第1の電位の極性と等しい極性の電荷を前記駆動回路に供給して前記第1の電位を補正する。

(もっと読む)

トランジスタの制御回路、トランジスタの制御システム、およびトランジスタの制御方法

【課題】ゲートとフィールドプレートとを有するトランジスタのスイッチング速度を速くする。

【解決手段】ゲートとフィールドプレートとを有するトランジスタ4を制御する制御回路2であって、トランジスタを駆動するタイミングを検出する検出回路38と、駆動するタイミングに応答してゲートを駆動する第1の駆動タイミングとフィールドプレートを駆動する第2の駆動タイミングとを制御するタイミング制御回路40と、第1の駆動タイミングに応答してゲートを駆動し第2の駆動タイミングに応答してフィールドプレートを駆動する駆動回路42とを有する。

(もっと読む)

容量性負荷駆動回路および流体噴射装置

【課題】上限あるいは下限付近のデューティー比でも効率よく容量性負荷を駆動する。

【解決手段】駆動波形信号をパルス変調して変調信号を生成し、電力増幅した後に平滑フ

ィルターを通すことによって生成した駆動信号を容量性負荷に印加する。デジタル電力増

幅器から平滑フィルターに流れる電流の方向が一変調周期内で逆転する条件下では、その

一変調周期内での電流の最大値および最小値の絶対値が所定の閾値以上となるようにキャ

リア周波数を変更する。一変調周期内で平滑フィルターを流れる電流の最大値および最小

値の絶対値が所定の閾値を下回ると、電力増幅時に大きな損失が発生する。従って、所定

の閾値を下回らないようにキャリア周波数を変更してやれば、効率よく電力増幅を行って

容量性負荷を駆動することが可能となる。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

負荷駆動回路

【課題】複数の電源電圧条件に対して電流制限特性が追従し、負荷特性に適した電流制限を行なう負荷駆動回路を提供する。

【解決手段】図1に示す負荷駆動回路は、電源及び負荷に接続された出力MOSトランジスタと、出力MOSトランジスタの出力電圧に応じて、出力MOSトランジスタに流れる出力電流を複数段階の制限電流に制限すると共に、制限電流が切り替わる際の出力電圧を電源電圧の変化に基づいて切り替える電流制限値切り替え回路と、を備える。その結果、段階的に電流制限を行い、過剰な電流制限となることを妨げ、負荷条件の拡大を図る。さらに、電流制限値の切り替えを電源電圧に対応させて行なうため、当初の電源電圧条件とはことなる電源電圧で使用したとしても、電流制限特性が電源電圧の変動に追従し、全体として負荷特性に適した電流制限を行なうことができる。

(もっと読む)

複合半導体装置

【課題】電子回路の誤動作を防止でき、かつ、電力変換装置の小型化に寄与する複合半導体装置を提供する。

【解決手段】複合半導体装置10は、第1の端子G1から入力される信号に応じて第2の端子C1から第3の端子E1へ電流を流す第1のパワー半導体素子13と、第1の端子G2から入力される信号に応じて第2の端子C2から第3の端子E2へ電流を流す第2のパワー半導体素子16が同一基板(チップ)20内に形成された半導体装置であって、第2のパワー半導体素子16の第3の端子E2は、第1のパワー半導体素子13の第1の端子G1に電気的に接続されており、第1のパワー半導体素子13の第2の端子C1の電位が時間経過とともに増加したとき、第2のパワー半導体素子16の第3の端子E2を介して第1のパワー半導体素子13の第1の端子G1に電荷をチャージする電流路を備えた。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

インジケータ駆動回路

【課題】電源電圧の変動によるインジケータの光源のちらつきを抑制するインジケータ駆動回路を提供する。

【解決手段】インジケータ駆動回路1は、2つのnpnトランジスタQ2,Q6からなるカレントミラー回路200と、カレントミラー回路200の制御側のトランジスタQ2に制御電流を供給する電流源であるpMOSトランジスタQ3,Q4と、被制御側のpMOSトランジスタQ6に流れる電流により駆動され、インジケータのLED30をオンオフさせるpMOSトランジスタQ5を備える。電流源100からカレントミラー回路200へ流す制御電流は、外部からの制御信号によりnMOSトランジスタQ1を介して切り換えられる。電流源100を構成する2つのトランジスタQ3,Q4をカスコード接続で構成することで、カレントミラー回路200に流れる電流に対する電源VCCの変動の影響を小さくする。

(もっと読む)

高周波モジュールおよび無線通信システム

【課題】低コスト化または小型化を実現可能なマルチバンド対応の高周波モジュールおよび無線通信システムを提供する。

【解決手段】例えば、高周波電力増幅装置HPAIC1は、GSM用のパワーアンプ回路部PABK_LB(PABK_HB)と、GSMかW−CDMAかを選択するモード設定信号Mctlを受けて、アンテナスイッチ制御信号SctlをVSW1レベルかVSW2レベルで出力する制御回路を備える。VSW2は、発振回路OSCからのクロック信号を用いてVSW1を昇圧することで生成される。HPAIC1は、MctlによってGSMが選択された際には、OSCを停止させると共にVSW1レベルのSctlをアンテナスイッチ装置ANTSWに出力し、MctlによってW−CDMAが選択された際には、OSCを用いてVSW2レベルのSctlをANTSWに出力する。

(もっと読む)

スイッチ装置および試験装置

【課題】入力電圧範囲の大きな半導体スイッチ装置を提供する。

【解決手段】外部から入力される制御電圧に応じて第1端子および第2端子間を電気的に接続または切断するスイッチ装置であって、第1端子および第2端子の間にソースおよびドレインが接続され、当該スイッチ装置に入力される入力電圧とゲート電圧との差に応じてオンまたはオフとなるメインスイッチと、制御電圧および入力電圧に応じて第1基準電圧を電圧シフトさせた駆動電圧をメインスイッチのゲートに供給する制御部と、を備えるスイッチ装置を提供する。

(もっと読む)

61 - 80 / 559

[ Back to top ]