Fターム[5J055GX06]の内容

Fターム[5J055GX06]に分類される特許

121 - 140 / 559

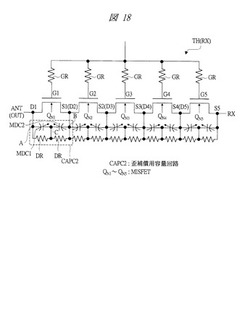

半導体装置

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】直列に複数個接続されたそれぞれのMISFETQN1〜QN5のソース領域とドレイン領域の間に、ソース領域の電位を基準としてドレイン領域に正電圧を印加する場合と、ソース領域の電位を基準としてドレイン領域に負電圧を印加する場合のいずれの状態においても、ソース領域の電位とドレイン電極の電位が同電位の状態よりも容量が減少する電圧依存性を持つ歪補償用容量回路CAPC2が接続されている。

(もっと読む)

ゲート駆動回路

【課題】トランジスタの遮断遅延を抑制し、絶縁ゲート型トランジスタ(IGBT)の保護動作を向上できるゲート駆動回路を提供する。

【解決手段】絶縁ゲート型トランジスタ31のゲートに、相補型の対のトランジスタ41A,41Bを接続し、対のトランジスタ41A,41Bのベースライン42の電流制御により絶縁ゲート型トランジスタ31を駆動するゲート駆動回路25において、トランジスタ41A,41Bのベースライン42に、ターンオン時にベースライン電流で充電されるコンデンサCsと、ターンオフ時にコンデンサCsに充電された電荷を消費すると共に、絶縁ゲート型トランジスタ31のゲート電位上昇によりトランジスタ41Aのベースに供給された電荷を消費する抵抗Rb2とを並列接続した電荷消費回路43Aを設けた。

(もっと読む)

切替回路及び受信回路

【課題】2つのクロック信号を切り替えて出力する切替回路において、出力信号のデューティ比を、入力されるクロック信号のデューティ比に保つこと。

【解決手段】切替回路100は、制御信号CONTに応じて、入力信号IN1,IN2を切り替えて出力信号OUTとして出力する。具体的には、制御信号CONTが「Lレベル」のときには、クロックドインバーターX2が動作し、信号IN1が信号OUTとして出力され、制御信号CONTが「Hレベル」のときには、クロックドインバーターX4が動作し、信号IN2が信号OUTとして出力される。

(もっと読む)

半導体スイッチ回路

【課題】一つの切替信号によってスイッチ動作を制御可能とする。

【解決手段】デプレッション型電界効果トランジスタ201とエンハンスメント型電界効果トランジスタ301が直列接続されて設けられ、デプレッション型電界効果トランジスタ201のゲートが第1のゲート抵抗器を介して接地される一方、エンハンスメント型電界効果トランジスタ301のゲートには、第2のゲート抵抗器を介して外部から切替信号が印加可能とされ、前記切替信号の電圧レベルを変化させることで、デプレッション型電界効果トランジスタ201とエンハンスメント型電界効果トランジスタ301の導通、非導通を相補的に切替可能にし、第1乃至第3の高周波入出力端子101〜103における高周波信号の入出力を制御可能としてなるものである。

(もっと読む)

電源検知回路

【課題】電源検知回路において、BT劣化によって比較回路のミスマッチが増大することに起因する電源検知信号の精度の劣化を抑制する。

【解決手段】検知用比較回路104は、入力切替信号生成回路112によって、その出力の活性状態と非活性状態との切替時付近では、入力信号102と基準電圧103とを入力して、その両者の比較を行う。一方、前記切替時付近以外では、比較回路非使用時入力電圧110が検知用比較回路104に入力されて、その差動入力が同電位に固定される。従って、BT劣化による電源検知精度の経年劣化が有効に抑制される。

(もっと読む)

長期間タイマー

【課題】 低価格で誤差が少ない長期間タイマーを提供する。

【解決手段】 一次電池10を所定時間高放電させる高放電回路20と、一次電池10を長期間連続して低放電させる低放電回路30と、高放電回路20による放電が終了した後に一次電池の初期出力電圧を検出する電圧検出部40と、一次電池の出力電圧が前記初期出力電圧に基づいて設定された基準電圧以下になったことを検知して報知する手段とを備えることを特徴。

(もっと読む)

半導体スイッチ回路

【課題】低周波帯域において線形性劣化のない半導体スイッチ回路を提供する。

【解決手段】入出力端子間に直列にソースおよびドレインを接続した1又は2以上の電界効果トランジスタと、電界効果トランジスタのゲートに接続した抵抗を備えた半導体スイッチ回路において、電界効果トランジスタのゲート−ドレイン間およびゲート−ソース間に、キャパシタをそれぞれ接続可能とした。

【効果】FETのゲート−ドレイン間およびゲート−ソース間すべてにキャパシタを接続したことにより、従来より低い周波数帯域においてゲート電極に接続する抵抗よりFETのインピーダンスが十分低くなるため、線形性を向上させることが可能となる。

(もっと読む)

ミリメートル波減衰器及びシャントスイッチング回路

【課題】ミリメートル波周波数において有効な切替え可能減衰器を提供する。

【解決手段】入力減衰器22は、直列結合されているRF_IN+端子、第1のノード、伝送線路TL3、直流遮断キャパシタCbl3、第2のノード、第3のノード、及び出力端子を有する第1の入力回路215を有する。第1のノードは、直列結合されているキャパシタCm3及び第1のシリコンゲルマニウムヘテロ接合バイポーラトランジスタQ9を介して選択的に接地へ結合される。第2のノードは、キャパシタCm1を介して接地へ結合されている。第3のノードは、直列結合されている直流遮断キャパシタCbl1、抵抗Ratt1及び第2のシリコンゲルマニウムヘテロ接合バイポーラトランジスタQ7を介して選択的に接地へ結合される。入力減衰器22は、更に、第1の入力回路215と並列に、第1の入力回路215と同じ構造を有する第2の入力回路216を有する。

(もっと読む)

レギュレータ用半導体集積回路

【課題】 外部から回路をオン、オフ制御するための制御端子を有するレギュレータ用ICにおいて、制御信号による起動直後に出力端子に向かってラッシュ電流が流れるのを防止できるようにする。

【解決手段】 制御回路のオン、オフを指示する制御信号が入力される外部制御端子(CE)とを備えたレギュレータ用ICにおいて、電圧入力端子または出力端子と接地電位端子との間に直列に接続された電流源(Tr0,R3)と基準電圧回路(Tr2,Tr3)を設け、該電流源と基準電圧回路との接続ノードは外付けのコンデンサが接続される外部端子(CS)に接続し、基準電圧回路はデプレッション型MOSトランジスタとエンハンスメント型MOSトランジスタが直列に接続され、それらのトランジスタのしきい値電圧の差に相当する電圧を出力するように構成した。

(もっと読む)

半導体集積回路および高周波モジュール

【課題】出力波形のリップルを低減可能な半導体集積回路を提供する。

【解決手段】例えば、高周波スイッチ回路RFSWと、そのオン・オフを制御するスイッチ制御回路SWCTLを備え、SWCTLは、2個のダウンコンバータ回路VGEN1,VGEN2と、レベルシフト回路LS[1]〜LS[4]を備える。各LS[n]は、レベルシフト段LSSG[n]とその後段に接続された出力段OTSG[n]を持ち、RFSWは、OTSG[n]からの制御信号OUT[n]によって制御される。LSSG[n]は、VGEN1からの負の電源電圧(−VSS1)を用いて動作し、OTSG[n]は、VGEN2からの負の電源電圧(−VSS2)を用いて動作する。−VSS1では、LSSG[n]のレベルシフト動作に伴いリップルが生じ得るが、−VSS2ではOTSG[n]の動作がスイッチング動作であるためリップルが生じ難い。

(もっと読む)

高周波スイッチ回路

【課題】2次高調波歪みの発生を抑制することができる高周波スイッチ回路を提供することである。

【解決手段】本発明にかかる高周波スイッチ回路は、共通端子と第1の端子との間に配置された第1のスイッチ(T11〜T14)と、共通端子と第2の端子との間に配置された第2のスイッチ(T21〜T24)と、を少なくとも備える。第1のスイッチが備える電界効果トランジスタには、第1のスイッチがオフ状態の時に生成される寄生容量を相殺する補償容量(Cdb11〜Cdb14)がドレインとボディとの間、またはソースとボディとの間に形成されている。また、第2のスイッチが備える電界効果トランジスタには、第2のスイッチがオフ状態の時に生成される寄生容量を相殺する補償容量(Cdb21〜Cdb24)が、ドレインとボディとの間、またはソースとボディとの間に形成されている。

(もっと読む)

パワーモジュール

【課題】過電流保護の判定を高精度に行うパワーモジュールの提供を目的とする。

【解決手段】本発明のパワーモジュールは、主電極及びセンス電極を有する半導体デバイス1と、一端が半導体デバイス1のセンス電極Sに接続され、半導体デバイス1の主電流に応じたセンス電流を電圧変換するセンス抵抗Rsと、センス抵抗Rsの他端を制御グランドに接続する第1配線4と、主電極を主端子Eに接続する第2配線5と、第2配線5の主電極側を第1配線4のセンス抵抗Rs側に接続する第1電流経路6と、第1配線4の制御グランド側を第2配線5の主端子E側に接続する第2電流経路7と、を備える。

(もっと読む)

可変ゲート電界効果トランジスタ(FET)及びこのFETを備える電気電子装置

【課題】可変ゲート電界効果トランジスタ(FET)及びこのFETを備える電気電子装置を提供する。

【解決手段】熱によるFETのソース及びドレイン間の電流減少の問題を効果的に解決し、またFETの温度を低めることができる可変ゲートFET及びこのFETを備える電気電子装置を提供し、可変ゲートFETは、FETと、FETの表面または発熱部分に取り付けられ、回路的には、FETのゲート端子に連結されておりゲート端子の電圧を変化させるゲート制御素子と、を備え、FETの温度が所定温度以上に上昇しているときに、ゲート制御素子が、ゲート端子の電圧を変化させて、FETのソース及びドレイン間のチャンネル電流を制御する。

(もっと読む)

電子回路、パワーオンリセット回路、集積回路装置及び電子機器

【課題】電源投入時に初期状態を確実に設定できる電子回路、パワーオンリセット回路、集積回路装置及び電子機器等を提供すること。

【解決手段】電子回路は、各回路素子がトランジスターで構成される複数の回路素子XA1〜XB2と、第1の高電位電源電圧VDDが供給され、VDDが所定の電圧レベルになるまでは、低電位電圧レベルに設定され、VDDが所定の電圧レベルを越えると、VDDに追従して電圧レベルが上昇する第2の高電位電源電圧VINTを出力する電源出力回路100とを含む。複数の回路素子のうち、初期状態においてその出力ノードが高電位電圧レベルになる回路素子である第1のグループの回路素子XA1、XA2には、VDDが供給され、初期状態においてその出力ノードが低電位電圧レベルになる回路素子である第2のグループの回路素子XB1、XB2には、VINTが供給される。

(もっと読む)

電力増幅器の過電流検出回路及びその方法

【課題】 しきい値を的確に可変して過電流検出の誤作動を防止する。

【解決手段】 過電流検出回路6Bは、Q2のエミッタと出力端子Oの間の電流検出抵抗R11の両端間に抵抗R21、R31が接続されている。R31の両端が過電流検出トランジスタQ5のベース−エミッタ間に接続されており、出力端子Oと−VB の間にダイオードD21、抵抗R61が接続されており、D21のカソードがQ5のエミッタと接続されている。R21とR31の接続点とグランド間には抵抗R51とD11が接続されており、R51とD11の接続点とQ2のエミッタの間にコンデンサC21が接続されている。R51、D11、C21のしきい値可変回路9Aは出力電圧の大きさが大きくなるとしきい値を大きくし、出力電圧の大きさが小さくなるとしきい値を小さくするが、C21とD11により、出力電圧の大きさが増加するときはしきい値を早く増大変化させ、減少するときはしきい値をゆっくり減少変化させる。

(もっと読む)

半導体装置

【課題】信号経路に挿入されたフローティングボディ型のトランジスタを用いて高速動作と低消費電力動作が可能な半導体装置を提供する。

【解決手段】本発明の半導体装置において、フローティングボディ型のトランジスタQ10は、センスアンプの出力ノードNS(第1の回路ノード)とローカル入出力線LIO(第2の回路ノード)との間に挿入されている。トランジスタQ10のゲートにカラム選択信号YS(第1の信号)が供給され、カラム選択信号YSがトランジスタQ10を非導通に保つ第1の論理レベルと導通方向に導く第2の論理レベルとの間で変化する。トランジスタQ10を利用しない回路状態時に、第2の論理レベルに近い第1及び第2の電圧レベルが出力ノードNS及びローカル入出力線LIOに供給される。これにより、フローティングボディ型のトランジスタQ10のCV特性を適切に制御し、ゲート容量を抑制することができる。

(もっと読む)

電気負荷の電流制御装置

【課題】常温環境のみで初期校正を行ない、実用温度環境においても正確な電流制御を行なう。

【解決手段】所定の温度特性を有する電流検出抵抗126の側近位置に温度センサ171を配置して、校正環境と実用環境における抵抗値を推定すると共に、目標負荷電流に対応した校正環境における実測負荷電流を制御特性データとして記憶し、目標負荷電流に対応した補正目標電流を算出し、電流検出抵抗の変動比率に基づく換算目標電流を電流制御の目標電流として制御する。温度センサ171では完全には検知できない電流検出抵抗126の発熱による抵抗変動分は、制御特性データの中で補正され、制御特性の線形性が改善される。

(もっと読む)

半導体基板および半導体装置

【課題】トレンチゲート型などの微細MOSFETにおいて、MOSFETの動作電流とダイオード電流を検出することができる半導体基板を提供する。

【解決手段】半導体基板において、半導体基板1は、主電流領域2と主電流領域2に流れる主電流より小さい電流が流れる電流センス領域3を有し、主電流領域2は、主面にソース電極8が配置され、ソース電極8はp型半導体領域(ボディ)6とn+型半導体領域(ソース)7に接触し、電流センス領域3は、主面にMOSFET電流検出用電極10およびダイオード電流検出用電極11が配置され、MOSFET電流検出用電極10はp型半導体領域(ボディ)6とn+型半導体領域(ソース)7に接触し、ダイオード電流検出用電極11はp型半導体領域(ボディ)6に接触する。

(もっと読む)

半導体スイッチ集積回路

【課題】チップやパッケージのサイズやコストの増加を抑えるとともに、安定動作が実現できる半導体スイッチ集積回路を提供する。

【解決手段】制御電圧印加端子と、オン状態のFETとオフ状態のFETの接続点との間に、抵抗素子を接続する。さらにオフ状態のFETのソース端子とドレイン端子との間に抵抗素子を接続する。その結果、制御電圧以外に外部からGND電位を含めたDC電圧を加えなくとも、半導体スイッチ集積回路を構成するFETのドレイン端子、ソース端子に安定に電圧を供給することができ、オフ状態のFETのソース端子およびドレイン端子の電位を所定の電位に設定することができる。

(もっと読む)

情報処理装置

【課題】 電源遮断機能を有するLSIにおいて、電源遮断をオンオフするときにリーク電流による電流が急激に変化すると電源線にノイズを生ずる。

【解決手段】 情報処理装置であって、回路ブロックと、前記回路ブロックに電源を供給するためのローカル電源線と、電源線と、前記電源線と前記ローカル電源線の間にそのソース―ドレイン経路が設けられる第1のトランジスタとを有し、前記第1のトランジスタは、第1の状態においてはオフ状態に制御され、第2の状態においてはオン状態に制御され、前記第1の状態から前記第2の状態に移行する際に、前記第1のトランジスタは、前記第1のトランジスタのソース―ドレイン経路を流れる電流の変化率が、所定の値を超えないように制御されることを特徴とする。

(もっと読む)

121 - 140 / 559

[ Back to top ]