Fターム[5J055GX06]の内容

Fターム[5J055GX06]に分類される特許

161 - 180 / 559

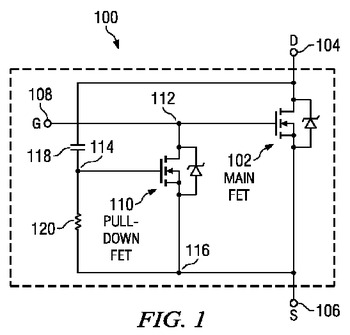

ゲート・プルダウンを備えたMOSFET

スイッチングタイプのDC−DCパワー・コンバータのMOSFETメインスイッチ・トランジスタ(102)のドレインとゲートとの間にプルダウンMOSFET(110)が結合される。プルダウンMOSFET(110)のゲートは、キャパシタ118によってメインスイッチ・トランジスタ(102)のドレインに結合され、抵抗(120)によってメインスイッチ・トランジスタ(102)のソースに接続される。プルダウンMOSFET(110)は、メインスイッチ・トランジスタ(102)にわたる電圧降下への容量性結合によって動作され、ミラー効果によるメインスイッチ・トランジスタ(102)の意図しないターンオンを避ける又は低減するため、メインスイッチ・トランジスタ(102)のゲートをそのソース電位にまたはその近辺に保持するために用いられ得る。

(もっと読む)

(もっと読む)

駆動回路、当該駆動回路を具備する表示装置、及び当該表示装置を具備する電子機器

【課題】チャネルが非晶質半導体によって構成される薄膜トランジスタを単極性の駆動回路に用いる際、しきい値電圧の変動の程度に応じてしきい値電圧を補正する駆動回路を提供することを課題の一とする。

【解決手段】半導体層の上下に絶縁層を介して配置された第1のゲート及び第2のゲートを有する単極性のトランジスタで構成される駆動回路において、第1のゲートには、トランジスタのスイッチングを制御するための第1の信号が入力され、第2のゲートには、トランジスタのしきい値電圧を制御するための第2の信号が入力され、第2の信号は、トランジスタのソースとドレインとの間を流れる電流を含む、駆動回路の消費電流の値に応じて制御されるものとする。

(もっと読む)

半導体記憶装置および昇圧回路

【課題】回路面積の削減しつつ、消費電流やピーク電流の増大を抑制することが可能な半導体記憶装置を提供する。

【解決手段】昇圧回路は、第1ないし第4の整流素子と、第1ないし第4のMOSトランジスタと、第1ないし第4のキャパシタと、スイッチ回路と、を備える。スイッチ回路は、第1のMOSトランジスタの他端と第3の整流素子の一端との間の第1の接続点、および、第2のMOSトランジスタの他端と第4の整流素子の一端との間の第2の接続点に接続された低レベル端子と、第3のMOSトランジスタの他端、および、第4のMOSトランジスタの他端に接続された高レベル端子と、を有し、低レベル端子の電圧または高レベル端子の電圧を切り換えて、出力端子に出力するスイッチ回路と、を含む。

(もっと読む)

論理回路及び半導体装置

【課題】クロックゲーティングを行う論理回路において、待機電力を低減すること又は誤動作を抑制すること。

【解決手段】論理回路は、クロック信号が供給されない期間に渡って、ソース端子及びドレイン端子に電位差が存在する状態でオフするトランジスタを有する。該トランジスタのチャネル形成領域は、水素濃度が低減された酸化物半導体によって構成される。具体的には、当該酸化物半導体の水素濃度は、5×1019(atoms/cm3)以下である。そのため、当該トランジスタのリーク電流を低減することができる。その結果、当該論理回路の待機電力を低減すること及び誤動作を抑制することができる。

(もっと読む)

集積回路装置及び電子機器

【課題】通常動作モード、低消費電力動作モードでの省電力化等を図れる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、外部電源電圧VDDEを受けて、外部電源電圧VDDEを降圧した第1の電源電圧VDDAを出力する第1のレギュレーターRG1と、外部電源電圧VDDEを受けて、外部電源電圧VDDEを降圧した第2の電源電圧VDDBを出力する第2のレギュレーターRG2と、第1の電源電圧VDDAが供給され、通常動作モード及び低消費電力動作モードにおいて動作する第1のロジック回路LG1と、第2の電源電圧VDDBが供給され、通常動作モードにおいて動作し、低消費電力動作モードでは非動作になる第2のロジック回路LG2を含む。

(もっと読む)

高耐圧スイッチ回路およびそれを用いた半導体集積回路装置

【課題】 双方向スイッチにおいて、ドレイン電圧またはドレイン-ソース間電圧に基づいて、上記スイッチのゲート-ソース間電圧を制御する手段と、上記制御手段を介して、上記スイッチのゲート端子に電圧を印加するスイッチドライバとを備えている双方向スイッチを提供する。

【解決手段】 双方向スイッチであるメインスイッチと、上記メインスイッチのゲート-ソース間電圧を、上記メインスイッチのドレイン電圧、ソース電圧に基づいて制御する手段と、上記制御手段を介して上記メインスイッチのゲート端子に電圧を印加するスイッチドライバとを備えている双方向スイッチを構成する。

(もっと読む)

多チャンネル高周波信号切替装置

【課題】多チャンネルの高周波信号切り替えを小規模の回路構成にて容易に実現できる多チャンネル高周波信号切替装置を提供する。

【解決手段】多チャンネルの高周波信号を扱う切替回路を、四辺形のマトリクス配線領域11を囲繞するように例えば8組の高周波信号切替スイッチ12A〜12Hを設け、各チャンネルに共通のマトリクス配線領域に集成して、多チャンネル集成型の高周波信号切替回路を構成した。

(もっと読む)

負荷駆動装置

【課題】従来の負荷駆動装置は、電源が正常に接続された場合の待機時において消費電流が増大するという問題があった。

【解決手段】本発明にかかる負荷駆動装置は、電源端子PWRと出力端子OUTとの間に接続された出力トランジスタT1と、出力端子OUTと接地端子GNDとの間に接続された負荷11と、出力トランジスタT1のゲートと接地端子GNDとの間に設けられ、電源11の極性が逆になった場合に出力トランジスタT1を導通状態にする保護トランジスタMN3と、電源10の極性が正常の場合に接地端子GNDと保護トランジスタMN3のバックゲートとを導通状態に制御するバックゲート制御回路17と、を備える。

(もっと読む)

半導体装置および電子機器

【課題】パワー半導体素子を駆動するためのドライバを低コストで得ることが可能な半導体装置およびそれを備えた電子機器を提供する。

【解決手段】半導体装置101は、ハイサイド駆動部62からの駆動信号を受ける第1のスイッチング機能部と、ローサイド駆動部64からの駆動信号を受ける制御電極とを有する第2のスイッチング機能部とを備え、ハイサイド駆動部62は、ノーマリーオン型の電界効果トランジスタを含み、スイッチング制御信号の基準電圧を出力ノードの電位へシフトした駆動信号を出力し、第1のスイッチング機能部はノーマリーオン型の第1の電界効果トランジスタTr1を含み、第2のスイッチング機能部はノーマリーオン型の第2の電界効果トランジスタTr2を含み、ハイサイド駆動部62および第1の電界効果トランジスタTr1は第1の半導体チップ71に含まれている。

(もっと読む)

半導体装置

【課題】回路構成の簡素化を図り、経年変化の影響を受けることなく、スイッチング素子のジャンクション又はチャネルを熱的破壊から保護することが可能な半導体装置を提供する。

【解決手段】縦型のMOSFETからなる保護トランジスタ20は、半導体基板2の一面にゲート電極23及びソース電極22を、他面にドレイン電極21を形成してある。出力トランジスタ10が形成された半導体基板1の一面に存するソース電極12と、半導体基板2の一面とを導電性の接着剤6で接着して、ソース電極12にソース電極22及びゲート電極23を電気的に接続し、熱的に密結合させる。出力トランジスタ10のゲート電極13は、リード線32で保護トランジスタ20のドレイン電極21と接続する。高温の場合、保護トランジスタ20は閾値が0V以下に低下してオンし、出力トランジスタ10が遮断される。

(もっと読む)

スイッチ回路

【課題】オン時の信号歪みが少なく、かつオフ時の抵抗を高くして確実に信号を遮断することができるスイッチ回路を提供する。

【解決手段】第1の端子から入力された電圧信号と切替電圧が入力される増幅器の入力端子と出力端子を結ぶ経路の途中およびこの増幅器の出力側に第1、第2のダイオードを配置し、また第2の端子が接続される経路で、第2のダイオードが接続されていない経路中にスイッチ素子を配置して、このスイッチ素子のオンオフを、第2のダイオードと同じように制御するようにした。信号歪みが少なく、かつスイッチ素子を用いて信号を遮断するので、確実に信号を遮断できる。

(もっと読む)

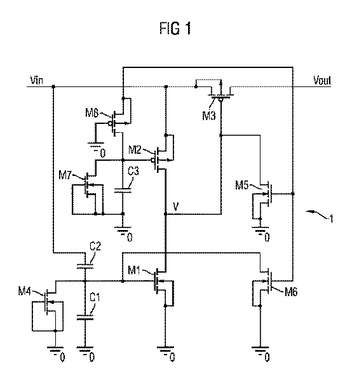

ドライバ回路

【課題】差動入力信号の振幅中心電圧が高い場合でも、差動出力信号の振幅変動やジッタを抑制することができるドライバ回路を提供することである。

【解決手段】本発明にかかるドライバ回路は、トランジスタM1と、トランジスタM1のソースと電源端子との間に接続された負荷素子R1と、トランジスタM1とカレントミラー回路を構成するトランジスタM2と、入力された差動入力信号に応じた差動出力信号を出力すると共に、トランジスタM2によりソースにバイアス電流が供給される一対のトランジスタを備える差動対と、トランジスタM2のソースと電源端子との間に接続された負荷素子R2と、非反転入力端子がトランジスタM1のソースと接続され、反転入力端子がトランジスタM2のソースと接続され、出力が差動対を構成する一対のトランジスタのバックゲートに接続されたオペアンプAMP1と、を有する。

(もっと読む)

時定数回路、スイッチ回路、DC/DCコンバータ及び表示装置

【課題】単調に減衰するだけの出力電圧特性に比べて、急峻に減衰した後に緩やかに減衰する出力電圧特性が得られる時定数回路等を提供する。

【解決手段】時定数回路10は、抵抗素子111と容量素子121との並列回路131,…が第一の端子14と第二の端子15との間に複数直列に接続されて成る直並列回路16と、第二の端子15に接続された第三の端子17と第四の端子18との間に接続された分圧用抵抗素子19と、を備えている。並列回路131は抵抗素子111と容量素子121とから成り、並列回路132は抵抗素子112と容量素子122とから成り、・・・、並列回路13nは抵抗素子11nと容量素子12nとから成る。nは、並列回路131〜13nの数であり、2以上の整数である。

(もっと読む)

半導体集積回路

【課題】PKGの設計期間を遅延させることなくクロストーク耐性を向上させることが可能な半導体集積回路を提供する。

【解決手段】複数の信号配線を有するChip20において、一の信号配線と前記一の信号配線に隣接する一方の隣接信号配線と前記一の信号配線に隣接する他方の隣接信号配線との間で生じるクロストークの発生量を抑制するための補正係数31と、前記一の信号配線に送出される一の信号、前記一方の隣接信号配線に送出される一方の隣接信号、および前記他方の隣接信号配線に送出される他方の隣接信号の組み合わせパターンと、に基づいて、前記一の信号のスルーレートの低減度合を示す補正量を演算する補正量演算部42a〜42cと、前記補正量に基づいて、前記一の信号のスルーレートを調整するドライバ41a〜41cと、を備える。

(もっと読む)

駆動装置、及び表示装置

【課題】並列接続された複数の出力アンプ回路において所望の駆動能力を実現することができる駆動装置、及び表示装置を提供すること。

【解決手段】本発明に係る駆動装置(ソースドライバ1)は、並列接続された複数の出力アンプ回路10と、複数の出力アンプ回路10に、バイアス電圧供給源25からバイアス電圧を供給するバイアス配線(幹バイアス配線22)と、複数の出力アンプ回路10に、電源電圧供給源35から電源電圧を供給する電源配線31と、複数の出力アンプ回路10に供給される電源電圧とバイアス電圧との差が所望となるように、バイアス電圧にオフセット電圧を重畳する補正手段(バッファ26)とを備えた。

(もっと読む)

半導体装置及びその制御方法

【課題】プルアップ回路(バスホールド回路)の電源電圧Vcc及び入力端子INに電位差が生じる場合でもリーク電流を発生させない手段を提供する。

【解決手段】パスホールド回路に制御端子CNTを設ける。この制御端子CNTの反転出力で動作するスイッチとしてMOSFET13を備える。一方入力端子INと制御端子CNTの入力はNORゲート31に入力され、このNORゲート31の出力がパスホールド回路の入力端子・電源電圧間の接続を制御するMOSFET12のゲート端子に入力される。MOSFET12及びMOSFET13を直列に接続することで、入力端子・電源電圧間の接続をより制度よく制御し、リーク電流の発生を抑止する。

(もっと読む)

リーク電流を検出及び補正するマルチプレクサ

【解決手段】多重入出力(I/O)システムは、選択された入力チャネルにおけるリーク電流を検出する。当該システムは、複数の入力チャネルのうちの1つから選択された出力を供給するために接続されたリーク電流検出マルチプレクサを含んでいる。また、リーク検出マルチプレクサは、選択された入力チャネルに関し測定されたリーク電流を当該出力の一部として供給する。検出されたリーク電流に基づき、検出されたリーク電流がマルチプレクサの出力のインテグリティを喪失させたか否かに関する測定を行うことが可能である。更に、当該検出されたリーク電流は、マルチプレクサによって供給される出力を補正するために使用され、選択されたチャネルにおけるリーク電流の存在を補償することが可能である。 (もっと読む)

低歪みのプログラマブルゲインアンプ用の動的スイッチドライバ

NチャネルMOSFETMB)及びPチャネルMOSFE(MA)を含む少なくとも1つのスイッチであって、NチャネルMOSFETMB)及びPチャネルMOSFE(MA)の各々は、スイッチのオン/オフ状態を変化させるための駆動信号を受けるように構成されたゲートを有する、少なくとも1つのスイッチと、スイッチのオン/オフ状態を変化させるための1対の駆動信号を選択的に加えるように構成され配置された駆動回路(5DC)であって、(a)スイッチのオン/オフ状態を変化させるのに十分な1対のDC信号成分と、(b)1対の時間変動信号成分(Vonn、Vonp)との関数として、上記駆動信号を発生させるように構成され配置された駆動回路とを備え、前記1対の時間変動信号成分は、各MOSFETのソース端子上に存在する信号の少なくとも部分的な複製としての1対の時間変動信号成分であり、DC信号とともにnチャネルMOSFET及びpチャネルMOSFETのゲートにそれぞれ加えられたときに、上記駆動信号は、スイッチのオン/オフ状態を保持し、各MOSFETのゲート−ソース電圧をMOSFETのゲート−ソース絶縁破壊限界内に維持するように、適切なレベルになる、時間変動入力信号をスイッチするためのスイッチング回路。  (もっと読む)

(もっと読む)

特に圧電式のマイクロジェネレータを有しているエネルギ自立型のマイクロシステムのためのトリガ回路及び整流器

本発明は、十分に大きい電圧レベルを検出するため、また、十分な出力を供給するためのトリガ回路に関する。更に本発明は、従来の解決手段に比べて、同じ出力電圧で効果的により多くの出力を供給する整流器に関する。トリガ回路及び整流回路は、特に圧電式のマイクロジェネレータを有するエネルギ自立型のマイクロシステムにおいて使用することができる。  (もっと読む)

(もっと読む)

パルス幅変調を有するチャージポンプ回路

電圧調整器のチャージポンプ回路の各スイッチング素子は、並列に接続される比較的大型のMOSトランジスタと関連付けられた、比較的小型のMOSトランジスタを備える。第1の動作モードにおいて、小型のトランジスタのみがスイッチングされ、一方、第2の動作モードにおいて、大型のトランジスタがスイッチングされる。このようにして、第1の動作モードにおけるスイッチング損失を減少させることができる。  (もっと読む)

(もっと読む)

161 - 180 / 559

[ Back to top ]