Fターム[5J055GX06]の内容

Fターム[5J055GX06]に分類される特許

81 - 100 / 559

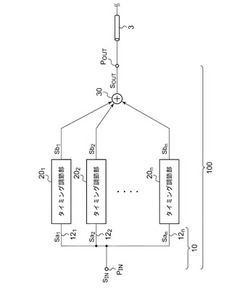

ドライバ回路およびそれを用いた試験装置

【課題】ポジティブエッジの波形、ネガティブエッジの波形の少なくとも一方を調節可能なドライバ回路を提供する。

【解決手段】分岐回路10は、送信すべき入力信号SINを複数の経路12に分岐する。各タイミング調節回路20は、それぞれが対応する経路に分岐された送信すべき信号Saのポジティブエッジおよびネガティブエッジの少なくとも一方に遅延を与える。合成出力回路30は、複数のタイミング調節回路20の出力信号Sbを合成し、合成された信号SOUTを伝送線路3に出力する。

(もっと読む)

負荷駆動装置

【課題】より高速駆動に対応でき、かつ、消費電流を低減することができる負荷駆動装置を提供する。

【解決手段】ダーリントン回路によってスイッチングデバイス2を駆動するようにし、ダーリントン回路を構成する第1PchMOSFET5と第2PchMOSFET6のドレインを共にスイッチングデバイス2を構成するIGBTのゲートに接続する。これにより、第2PchMOSFET6の駆動電流もIGBTの駆動に用いることができるため、消費電流を低減できると共に、より大電流でのIGBT駆動が可能になるため高速駆動を行うことができる。また、第2抵抗4と並列的にスイッチ10を備え、このスイッチ10をプルアップ駆動時にオンさせる。これにより、プルアップ駆動時に第1PchMOSFET5のゲート−ソース間の抵抗値を低下させることが可能となり、駆動スピードが低下することを抑制することが可能となる。

(もっと読む)

駆動装置、スイッチ装置、および試験装置

【課題】非反転増幅によるFETドライブ回路を提供する。

【解決手段】第1基準電圧出力部と、入力端子および第1基準電圧出力部の間に位置する第1端子および第2端子の間に設けられ、第1端子から第2端子へと流れる電流に応じて電圧を降下させる第1電圧降下部と、第1端子および出力端子の間に接続された第1電流源と、第2基準電圧を出力する第2基準電圧出力部と、出力端子および第2端子の間に設けられ、第2基準電圧と第2端子の電圧との差に応じてオンまたはオフとなる第1スイッチ部と、第1スイッチ部がオンおよびオフの状態における第1電圧降下部が降下させる電圧の変化を補償する補償部と、を備える駆動装置を提供する。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

半導体装置およびその検査方法

【課題】本発明の実施形態は、高周波スイッチ回路の高周波特性の良否を簡便に判定することができる半導体装置およびその検査方法を提供する。

【解決手段】実施形態に係る半導体装置は、複数の高周波端子と、共通高周波端子と、の間の信号経路を、前記高周波端子と前記共通高周波端子との間に直列に設けられた複数のFETにより切り替える高周波スイッチ回路を有する半導体装置であって、前記共通高周波端子に接続された複数のFETを含む半導体スイッチと、前記半導体スイッチを介して前記共通高周波端子に接続された発振回路と、前記発振回路の出力を入力とする検波回路と、前記検波回路の出力端子と、を備える。

(もっと読む)

半導体スイッチ

【課題】端子切替時の応答特性を改善した半導体スイッチを提供する。

【解決手段】電源回路部は、正の電源電位よりも高い第1の電位と、負の第2の電位と、を生成する。駆動回路部は、前記電源回路部に接続され、端子切替信号に応じて前記第1の電位をハイレベルとし前記第2の電位をローレベルとする制御信号を出力する。スイッチ部は、制御信号を入力して端子間の接続を切り替える。前記駆動回路部は、第1と、第2のレベルシフタと、第1の回路と、を有する。前記第2のレベルシフタは、前記第1のレベルシフタの出力電位に応じて互いに排他的にオンする第2のハイサイドスイッチと第2のローサイドスイッチとを有し、前記制御信号を出力する。前記第1の回路は、前記端子切替信号に応じて、前記制御信号の電位の変化よりも前に前記第2のローサイドスイッチに前記電源電位を供給し、または前記ハイサイドスイッチに前記接地電位を供給する。

(もっと読む)

負荷駆動装置の製造方法

【課題】負荷駆動装置において負荷を駆動するためのスルーレートが狙い値となるように負荷駆動装置を製造する。

【解決手段】まず、半導体基板に第1基準電源32、スイッチング素子34、電流生成部35、およびオペアンプ33を備えた駆動回路30を形成する。この場合、第1基準電源32の第1基準電圧を調整することにより、負荷10に流す定電流の大きさを調整する。続いて、電流生成部35で生成されるテール電流が大きくなるようにテール電流のトリミングを行うことでオペアンプ33のスルーレートを調整する。これにより、オペアンプ33がスイッチング素子34を駆動したときに負荷10に流れる定電流が一定値に達するまでの定電流の立ち上がりの傾きを狙い値に調整することができる。

(もっと読む)

MOSFETの電流判定装置

【課題】MOSFETのオン抵抗の温度特性に追随して高精度で電流レベル判定を行う。

【解決手段】MOSFET1に一体に感温素子4が設けられ、ドレイン/ソース間電圧Vdsと温度検出信号Vfを検出する。電圧Vdsは電圧検出部6に入力され、感温素子4の電圧Vfは第1および第2の補正回路8、9に入力される。MOSFET1のオン抵抗Ronの温度特性を第1および第2の温度領域のそれぞれに対応した近似直線で近似し、傾きを変えるように補正回路8、9で演算処理する。予め設定された判定電流値をRonの温度特性を考慮して判定電圧生成部11で判定電流に相当する判定電圧Vdsrefを生成する。これにより、比較器13で判定電流以上の電流がMOSFET1に流れたか否かを精度よく判定できる。

(もっと読む)

負荷駆動回路

【課題】負荷と直列に電流検出用のトランジスタを介在させることなく、オン指令期間とオフ指令期間の両期間における電流を高精度に検出する。

【解決手段】オン指令期間では、センストランジスタ23が負荷電流を検出する。オフ指令期間では、制御装置25は、オン指令期間に取得した少なくとも2つの時点の検出電流値を用いることにより、既知の電源電圧VBの下でリニアソレノイド2の時定数情報を算出し、その時定数情報と、オフ指令期間に移行する前に検出したオン指令期間の電流、電源電圧VBなどに基づいて、オフ指令期間における負荷電流を演算する。コンパレータ24は、オフ指令期間において出力電圧Voutと基準電圧Vrefとを比較し、制御装置25は、比較結果に基づいて還流ダイオード6のオープン故障を検出する。

(もっと読む)

高周波スイッチおよび高周波モジュール

【課題】挿入損失およびチップサイズの増大を生じることなく、歪特性に優れた高周波スイッチおよび高周波モジュールを提供する。

【解決手段】高周波スイッチであって、高周波信号を入出力するための複数の入出力端子101〜103と、2つの入力端子101、103間に設けられた基本スイッチ部104、105と、基本スイッチ部104、105の導通および遮断を制御するための制御電圧が入力される制御端子106、107とを備え、基本スイッチ部104、105は、メアンダ形状のゲート電極を有するメアンダ型のFET110〜113及びFET120〜123が多段に接続されて形成され、FET110〜113、及び120〜123のうち、入出力端子103からの電気的距離が最も短いFET113、及び120のフィンガー長は、他のFET110〜112、及び121〜123のフィンガー長よりも短い。

(もっと読む)

半導体装置、およびそれを用いた超音波診断装置

【課題】良好な線形性を有し、かつ電力損失の少ない双方向アナログスイッチの半導体装置を提供する。また、検出精度の高い超音波診断装置を提供する。

【解決手段】双方向にオンまたはオフ可能なスイッチ回路と、前記スイッチ回路の駆動回路を内蔵した双方向アナログスイッチの半導体装置であって、前記駆動回路は第一および第二の電源に接続され、前記第一の電源電圧は、前記スイッチ回路の入出力端子に印加される信号の最大電圧値以上であり、前記第二の電源電圧は、前記スイッチ回路の入出力端子に印加される信号の最小電圧値以下であり、さらに前記駆動回路は前記第一の電源と前記スイッチ回路との間に、直列に接続されたツェナダイオードとP型MOSFETを備えている。また、超音波診断装置であって、前記半導体装置を備える。

(もっと読む)

高周波用スイッチ回路

【課題】制御電圧以外の電源を用いることなく低消費電力かつ低コストで高性能に切り替え動作を行うことができる高周波用スイッチ回路を提供する。

【解決手段】第1および第2MOSFET回路11,21のゲート端子と第1および第2制御端子CT1,CT2との間に一端が接続され、他端がグランドGNDに接続されることにより、第1および第2制御端子CT1,CT2からグランドGNDへ向かう方向が順方向となるような少なくとも1つの整流素子D11,D12,D21,D22を含む第1および第2整流回路12,22と、第1および第2整流回路12,22の整流素子の少なくとも1つの順方向電流入力端子側と第1および第2MOSFET回路11,21の何れかの主端子側とが接続された接続部3とを備えている。

(もっと読む)

センス機能付きパワー半導体デバイス

【課題】センス機能付きパワー半導体デバイスのメイン領域とセンス領域の電流スイッチタイミングや過渡特性のずれを小さくするようゲート駆動回路で補正して電流検出の精度を向上させるセンス機能付きパワー半導体デバイスを提供する。

【解決手段】ゲートパルス発生回路(21)から出力されるゲート駆動信号が、ゲート抵抗値補正回路1(22)及びゲート抵抗値補正回路2(23)の各補正抵抗を経由してセンスゲート端子Gs 及びメインゲート端子Gm 並びにMPU(24)の入力端へ出力される。各ゲート抵抗値補正回路(22,23)の補正抵抗値は、駆動時の負荷電流値、各ゲート電圧値以外に、電源電圧値および素子温度値のうちいずれかの条件を測定し、測定した条件に応じてMPU(24)で最適な補正抵抗値を計算、または内蔵するメモリから最適な補正抵抗値を呼び出し、各ゲート抵抗値を補正する。

(もっと読む)

半導体装置および携帯電話機

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】RXスルートランジスタ群TH(RX)は、互いに直列に接続されたMISFETQ1〜Q5において、それぞれのMISFETのボディ領域と、隣接するMISFETのソース領域あるいはドレイン領域とを、それぞれ、ダイオード(整流素子)を介して接続する。そして、特に、nチャネル型MISFETの場合、MISFETのボディ領域から隣接するMISFETのソース領域あるいはドレイン領域へ向う向きが順方向となるようにダイオードを接続する。

(もっと読む)

マルチステートドライブ回路による半導体スイッチのスイッチング方法および回路

【課題】半導体スイッチがオフ状態からオン状態へ、或いはオン状態からオフ状態へ切換えられるときに半導体スイッチの損失を低減する新規な半導体スイッチの多段ドライブ回路を実施するための方法及び装置を提供する。

【解決手段】損失の低減は、半導体スイッチが切換える第1の時間期間中に半導体スイッチ両端のdv/dtに影響を与えることなく達成される。この損失の低減は、従って半導体スイッチが切換えるときの第1の時間期間中の急速なdv/dtによって発生する雑音をごくわずかしか増大させずに達成される。スイッチングロスのこの低減を達成するための回路の構成は、同様の結果を達成するための他の半導体スイッチドライブ方式よりも製造中の許容誤差及び温度の影響を受けにくい利点を有する。

(もっと読む)

リセット回路及び半導体集積回路

【課題】低電圧で動作可能なリセット回路を提供する。

【解決手段】リセット回路50Aは、Pチャネルの第1トランジスタ11を備え、第1電流i1が第1の値を超えると第1信号D1をアクティブとする第1回路10Aと、Nチャネルの第2トランジスタ21を備え、第2電流i2が第2の値を超えると第2信号D2をアクティブとする第2回路20Aと、電源電圧Vddの供給開始から、所定時間が経過した後に第3信号D3をアクティブとする第3回路30Aと、第1信号D1、第2信号D2、及び第3信号D3の全てがアクティブになるとリセット解除を指示するリセット信号RESを生成する論理回路40とを備える。

(もっと読む)

半導体スイッチ

【課題】端子切替時の挿入損失の増加を抑制した半導体スイッチを提供する。

【解決手段】実施形態によれば、電源回路部と制御回路部とスイッチ部とを備えた半導体スイッチが提供される。前記電源回路部は、内部電位生成回路と第1のトランジスタとを有する。前記内部電位生成回路部は、電源線に接続され、入力電位よりも高い第1の電位を生成する。前記第1のトランジスタは、前記内部電位生成回路の入力と出力との間に接続され、前記第1の電位が前記入力電位よりも低下したときオンして前記第1の電位を前記入力電位以上に保持するようにしきい値電圧が設定されたことを特徴とする。前記制御回路部は、前記第1の電位を供給され、ハイレベルまたはローレベルの制御信号を出力する。前記スイッチ部は、前記制御信号を入力して端子間の接続を切り替える。

(もっと読む)

高周波モジュール

【課題】信頼性が高い省電力モードを実現可能な高周波モジュールを提供する。

【解決手段】例えば、送信ノードTXをアンテナANTに接続するスイッチ用トランジスタTSW2と、TXを接地電源電圧GNDに短絡するスイッチ用トランジスタTSW1と、TSW1,TSW2のオン・オフを正の電源電圧VSWと負の電源電圧(−VSS)で制御するレベルシフト回路LSを備える。LSは、TSW2をオン、TSW1をオフに制御する送信動作モードTXMDの状態でスリープ命令を受けた際に、一旦、TSW2をオフ、TSW1をオンに制御するアイソレーション動作モードISOMDに移行し、一定の期間(Twait)が経過したのち、VSW,−VSSが非活性状態となるスリープモードSLPMDに遷移する。

(もっと読む)

半導体装置

【課題】小型化と高いアイソレーションを実現可能な半導体装置を提供する。

【解決手段】装置本体2は、半導体素子搭載部3と、第1の導電体4及び第2の導電体5を有する。第1の導電体4及び第2の導電体5は、半導体素子搭載部3の周囲に互いに近接して設けられている。半導体素子は、半導体素子搭載部に配設される。半導体素子は、第1のスルースイッチFET1と、第1のシャントスイッチFET1と、第2のスルースイッチFET2と、第2のシャントスイッチFET2と、を有する。第1のスルースイッチFET1は、共通端子ANTと第1の高周波端子RF1との間に接続される。第1のシャントスイッチFET1は、第1の高周波端子RF1に接続される。第2のスルースイッチFET2は、共通端子ANTと第2の高周波端子RF2との間に接続される。第2のシャントスイッチFET2は、一端が第2の高周波端子RF2に接続される。

(もっと読む)

電源復帰検出回路

【課題】電圧比較器を用いることなく、電源遮断ブロックの電源復帰を検出する。

【解決手段】電源遮断ブロック1に配置された信号遅延回路11と、電源が常時供給される常時オンブロック9に配置された測定パターン生成回路13、測定パターン検出回路15及び遅延時間測定回路17を備えている。遅延時間測定回路17は、測定パターン生成回路13から送信された測定パターンが信号遅延回路11を介して測定パターン検出回路15に到達するまでの遅延時間を測定する。電源遮断ブロック1の電源が遮断状態から投入状態に切り替えられた後、上記遅延時間が信号遅延回路11の設計値に基づく所定の遅延量以内になったときに、電源遮断ブロック1の電源が復帰したと判断する。

(もっと読む)

81 - 100 / 559

[ Back to top ]