Fターム[5J056AA00]の内容

論理回路 (30,215) | 回路の種類 (3,583)

Fターム[5J056AA00]の下位に属するFターム

入力回路 (420)

論理演算回路 (504)

出力回路 (1,065)

インターフェース、レベルシフト、レベル変換 (1,016)

Fターム[5J056AA00]に分類される特許

561 - 578 / 578

シフトレジスタ回路および表示装置

【課題】レベルシフト機能付きシフト回路を単純に複数段縦続接続し、互いに逆相のクロックパルスCK,xCKによって転送駆動を行う構成の場合、クロックパルスCK,xCKの周波数を簡単に下げることができない。

【解決手段】第1のシフト回路11−1と第2のシフト回路11−2とを対として縦続接続し、第3のシフト回路11−3と第4のシフト回路11−4とを対として縦続接続し、これら2組のシフト回路対を交互に縦続接続するとともに、これらシフトレジスタユニット(転送段)の繰り返し配置に対して、位相が相互に1/4周期ずれたクロックパルスCK1とクロックパルスCK2とを交互に与えるようにすることで、これらクロックパルスCK1,CK2の周波数を従来の1/2に低減する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の電源電圧の変換効率を向上させる。

【解決手段】 ハイサイドスイッチ用のパワーMOS・FETとローサイドスイッチ用のパワーMOS・FETとが直列に接続された回路を有する非絶縁型DC−DCコンバータにおいて、ローサイドスイッチ用のパワーMOS・FETと、そのローサイドスイッチ用のパワーMOS・FETに並列に接続されるショットキーバリアダイオードD1とを同一の半導体チップ5b内に形成した。ショットキーバリアダイオードD1の形成領域SDRを半導体チップ5bの短方向の中央に配置し、その両側にローサイドのパワーMOS・FETの形成領域を配置した。また、半導体チップ5bの主面の両長辺近傍のゲートフィンガ6aから中央のショットキーバリアダイオードD1の形成領域SDRに向かって、その形成領域SDRを挟み込むように複数本のゲートフィンガ6bを延在配置した。

(もっと読む)

半導体装置

【課題】 当該半導体装置の正常な動作を確保しつつ、低消費電力化を実現することのできる半導体装置を提供することを目的とする。

【解決手段】 主回路2は、クリティカルパスの第1論理回路21と、比較的高速な第2論理回路22とから構成されている。第2論理回路22には第1の電源電圧VDD1が供給されている。第1論理回路21には、通常、第2の電源電圧VDD2を供給されており、主回路2の正常な動作は確保されている。しかしながら、クロック供給回路6がクロックの供給を停止している時、又は信号供給源3からの入力信号Dinの信号電位が固定されている時には、第1論理回路21の電源電圧を第1の電源電圧VDD1に下げる。

(もっと読む)

半導体集積回路および半導体集積回路への電源電圧供給方法

【課題】 サンプル・ホールド回路を内蔵したICにおいて、コンデンサ素子の電極面積を縮小させる。

【解決手段】 サンプル・ホールド回路20は、入力信号Vinをサンプリングするスイッチ素子21と、サンプリングされた入力信号VinをVc=Vin−Vceの充電電圧でホールドするコンデンサ素子22と、コンデンサ素子22にホールドされた入力信号Vin=Vc+Vceをインピーダンス変換して出力するバッファアンプ23とを有している。コンデンサ素子22は、一端がスイッチ素子21とバッファアンプ23との接続点に接続されており、他端が中間電位Vceに接続される。コンデンサ素子22の耐圧は、高電位Vddと低電位Vssとの電位差より低く、高電位Vddと中間電位Vceとの電位差以上あればよい。

(もっと読む)

半導体記憶装置

【課題】周囲の温度変化に応じた適切なリフレッシュ周期で動作可能な半導体記憶装置を提供する。

【解決手段】定電流発生回路10は、温度依存性の小さい抵抗を内部に有し、周囲の温度にかかわらず常に一定のバイアス電圧BIASTを発生させて定電流発生回路11およびバイアス電圧調整回路12へ入力させる。定電流発生回路11は、温度依存性の大きい抵抗を内部に有し、周囲の温度によって変化するバイアス電圧BIASNを発生させてバイアス電圧調整回路12へ入力させる。バイアス電圧調整回路12は、バイアス電圧BIAST,BIASNに基づいて、温度依存性を有するバイアス電圧BIASSを発生させてリングオシレータ13へ入力させる。リングオシレータ13は、バイアス電圧BIASSのレベルに応じて、パルス信号PHY0の発生周期を変化させる。

(もっと読む)

レベル変換回路

【課題】 高速でレベル変換を行う小占有面積のレベル変換回路を提供する。

【解決手段】 小振幅の入力信号(IN)がサンプリングされる内部ノード(ND7)にMOS容量(6)を設け、このMOS容量のチャージポンプ動作により、内部ノードの信号電圧を選択的に昇圧する。この内部ノードに対して、選択的にラッチ状態となって内部ノードの電圧をラッチするラッチ回路(IV1、IV2、7)を設ける

(もっと読む)

電圧レベル変換回路

【課題】 入力信号の論理電圧を、より低い内部電圧に対応した論理電圧から、高電源電圧である外部電圧に対応した論理電圧に変換することができ、半導体装置の、より低い内部電圧による低電圧動作を可能とする電圧レベル変換回路を得る。

【解決手段】 低電圧系入力信号IN1の電圧レベルを高電圧系信号の電圧レベルに変換する電圧レベル変換回路100aにおいて、高電源電圧を耐圧とする複数の高耐圧MOSトランジスタからなるラッチ回路110と、該ラッチ回路の一方のラッチノードN10を放電する第1の高耐圧Nチャネル型MOSトランジスタQhn3と、前記ラッチ回路110のもう一方のラッチノードN11を放電する第2の高耐圧Nチャネル型MOSトランジスタQhn4とを備え、入力信号が遷移したときに、第1あるいは第2の高耐圧Nチャネル型MOSトランジスタのゲートに、低電圧系のパルス信号を昇圧して得られる昇圧パルス信号を印加する。

(もっと読む)

バルクバイアスを備える負極性チャージポンプ

チャージポンプ構造のCMOS環境につきものである寄生バイポーラトランジスタのターンオンを回避するような方法でnチャネルMOSトランジスタのバルクがバイアスをかけられる、nチャネルMOSトランジスタの負極性電圧チャージポンプが開示される、  (もっと読む)

(もっと読む)

半導体集積回路装置内瞬断対策回路

【課題】 外付けの大容量のコンデンサを使用することなく電源瞬断時にデータを喪失しないように対策を施すことができるようにする。

【解決手段】 電圧保持回路Hがバッテリ電源電圧+Bが低下したときにラッチ回路Rに供給される電源電圧を保持しているため、電源瞬断が発生したとしてもデータを喪失することなく対策を施すことができる。

(もっと読む)

集積回路のための電源の適応制御

本発明は、集積回路内の電源を制御するための回路装置および方法に関し、ここで、少なくとも1つの電気的に絶縁された領域の少なくとも1つの作業パラメータが、監視され、可変抵抗手段の導電率を局部制御して、前記少なくとも2つの電気的に絶縁された回路領域のそれぞれについて、少なくとも1つの監視された作業パラメータに基づいて、電源を個別に調整する。これにより、低い面積オーバーヘッドを有する高速で簡素な制御機能を、提供することができる。  (もっと読む)

(もっと読む)

異なる作動電圧範囲及びリセット電圧範囲を有するリピータ回路及びその方法

ワイヤ上の信号遷移を支援する回路及びその方法。第1のサブ回路(15〜22、65)は、回路の出力(34)に結合されている第1のトランジスタ(16)を、立ち上がり遷移の間、ターンオンさせ、出力(34)を高状態に駆動して、該立ち上がり遷移を支援する。第2のサブ回路(24〜30、66)は、回路の出力(34)に結合されている第2のトランジスタ(25)を、立ち下がり遷移の間、ターンオンさせ、出力(34)を低状態に駆動して、該立ち下がり遷移を支援する。第3のサブ回路(61、62)は、第1のサブ回路(15〜22、65)の構成要素をリセットする。該第1のサブ回路は、第1の閾電圧超で作動し、該第3のサブ回路(61、62)は、該第1の閾電圧未満で作動する。第4のサブ回路(63、64)は、第2のサブ回路(24〜30、66)の構成要素をリセットする。該第2のサブ回路は、第2の閾電圧未満で作動し、第4のサブ回路(63、64)は、該第2の閾電圧超で作動する。 (もっと読む)

集積回路の性能を調整するための装置および方法

プログラマブルロジックデバイス(PLD)は、遅延回路およびボディバイアスジェネレータを含む。遅延回路は、PLDにおけるユーザー回路のインプリメントの遅延を表すように構成された遅延回路を有する。ボディバイアスジェネレータは、ユーザー回路内のトランジスタのボディバイアスを調整するように構成される。ボディバイアスジェネレータは、遅延回路の信号伝播遅延から引き出されたレベルに応答し、トランジスタのボディバイアスを調整する。  (もっと読む)

(もっと読む)

一定電圧を供給可能な電源回路

【課題】 電源電圧の大きさに応じて、昇圧回路と降圧回路とを選択的に動作させることにより、効率的に一定電圧を供給することが可能な電源回路を提供する。

【解決手段】 USB電源13が5(V)の電圧を入力し、イネーブルスイッチ26がオン状態である場合、第1〜第3デジタルトランジスタ16〜18、nチャンネルMOSFET20、及び電圧検出部60が、変圧回路である昇圧回路40及び降圧回路50を制御して、降圧回路50のみを機能させる。一方、バッテリ14が1.8(V)の電圧を入力し、イネーブルスイッチ26がオン状態である場合、これらの素子は、昇圧回路40のみを機能させるように、変圧回路を制御する。いずれの場合においても、電源回路10は、出力端子24から3.3(V)の一定電圧を出力する。

(もっと読む)

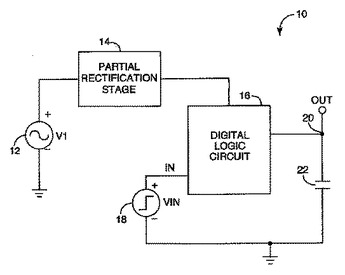

論理ゲートと部分整流段とを有する電子回路

論理回路は部分整流された交流(ac)波形により電力供給される。この波形はクリーンな一次dc電源信号を提供しないという意味で部分整流されている。代わりに実質的なac成分を含む波形で論理回路に電力供給することが可能である。部分整流ac波形をアモルファスまたは多結晶有機半導体、無機半導体またはそれら2つの組み合わせによる薄膜トランジスタを組み込んだ論理回路に適用し得る。  (もっと読む)

(もっと読む)

レベル・シフター

集積回路用レベル・シフター(301)である。一実施形態において、レベル・シフターは、入力端子又は出力端子として利用することができる各電圧ドメインに配置された信号端子(303,305)を有する双方向レベル・シフターである。或る実施形態においては、レベル・シフターは、入力端子が特定の状態であるとき両ドメインの電源間の電流の流れを遮断するためのトランジスタ(325,326)を含む。一実施形態において、レベル・シフターの唯1つの信号線が、ドメイン境界を横切る。  (もっと読む)

(もっと読む)

電圧変換装置

高入力電圧(Vi_high)と低入力電圧(Vi_low)とを有する入力信号(Si1)を受け取り、入力信号(Si1)の電圧レベルを変換して出力信号(So1)として出力する電圧変換装置(1)であって、上記電圧変換装置(1)が、上記入力信号(Si1)を受け取る第1の入力部(In1)と、第1の出力信号(So1)を出力する第1の出力部(Out1)と、第1の入力部(In1)が第1のノード(N1)に接続された接続状態と、第1の入力部(In1)が第1のノード(N1)から切り離された切断状態とを含む少なくとも2つ以上の状態の間で切替えを行うためのTFT(2)を有する電圧変換手段とを備え、上記電圧変換手段が、第1の入力部(In1)が第1のノード(N1)から切り離された状態から、第1の入力部(In1)が第1のノード(N1)に接続された状態に変化する前に、第1のノード(N1)の電圧を降下させるための第1の電圧降下手段を有する。 (もっと読む)

信号伝送システム

【課題】 できるだけ従来のシステム構成と部品構成を肯定しながら、数十GHz帯のディジタル高速信号を通すための信号伝送技術を提供する。

【解決手段】 電子回路全体に渡るトランジスタの論理回路、メモリ回路に含まれるドライバ1とレシーバ2の構成において、ドライバ1は信号伝送線路3を通じてレシーバ2に、電源・グランド伝送線路4を通じて電源Vddにそれぞれ接続される信号伝送システムであって、ドライバ1およびレシーバ2は全て実質的差動入力、差動出力とし、ドライバ1の実質的差動出力の出力端では電源またはグランドへの接続を有することなく、またレシーバ2は実質的差動入力の信号の電位差を検知することで受信し、さらに信号伝送線路3は分配配線がない、構造とする。

(もっと読む)

プリント回路基板、集積回路上の回路及び送信ラインの終端方法

【課題】送信ラインの正確なオンチップ終端の提供。

【解決手段】外部基準抵抗22に関係する抵抗値を有するオンチップ抵抗を使用して送信ラインの終端をネットワーク内に構成するようにする。終端抵抗ネットワーク50は、その抵抗値がオンチップ基準抵抗ネットワーク42の抵抗値に対して所定の関係を呈するように構成される。1つの実施例では、各終端抵抗ネットワークの抵抗地は実質的に各送信ラインの特性インピーダンスと同一である。

(もっと読む)

561 - 578 / 578

[ Back to top ]