Fターム[5J056AA03]の内容

Fターム[5J056AA03]に分類される特許

1 - 20 / 504

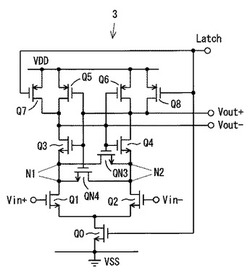

ラッチト・コンパレータ

【課題】差動回路の特性を損なうことなく、高速に信頼性の高いラッチ出力を行うラッチト・コンパレータを提供する。

【解決手段】ラッチト・コンパレータ(1)は、ドレイン・ソース間が、第1の電流経路上の第1のMOSトランジスタ(Q1)と第3のMOSトランジスタ(Q3)との間の第1のノード(N1)と、第2の電流経路上の第2のMOSトランジスタ(Q2)と第5のMOSトランジスタ(Q4)との間の第2のノード(N2)との間に接続されているとともに、ゲートが第1のCMOSインバータの出力に接続された、第7のMOSトランジスタ(QN3)と、ドレイン・ソース間が第1のノード(N1)と第2のノード(N2)との間に接続されているとともに、ゲートが第2のCMOSインバータの出力に接続された、第8のMOSトランジスタ(QN4)と、の少なくとも一方をさらに備えている。

(もっと読む)

半導体装置

【課題】低電圧動作を実現可能なレベルシフト回路を提供する。

【解決手段】入力電位は、GNDとVDDとの間で切り替わる。電源端子には、VDDよりも高いVDDOが印加される。レベルシフト回路は、クランプ回路と接続制御回路を備える。クランプ回路は、ソースが第1ノードに接続され、ドレインがP側出力端子に接続され、ゲートが電源端子に接続された第1NMOSトランジスタと、ソースが第1ノードに接続され、ドレインがN側出力端子に接続され、ゲートがグランド端子に接続された第1PMOSトランジスタと、を備える。入力電位がGNDとVDDの一方の場合、接続制御回路は、P側出力端子にVDDOを印加し、且つ、N側出力端子とグランド端子との間の電気的接続を遮断する。入力電位がGNDとVDDの他方の場合、接続制御回路は、N側出力端子にGNDを印加し、且つ、P側出力端子と電源端子との間の電気的接続を遮断する。

(もっと読む)

自己診断機能付き装置

【課題】自己診断する論理の範囲を比較回路以外の検査論理、更にはメイン論理に広げ、検査論理、メイン論理に異常がある場合、比較回路が不一致を発生する前に検出し装置の交換ができるようにする。

【解決手段】同じ入力が与えられ、同じ論理演算を実施する第1と第2の論理部、第1と第2の論理部のいずれかにエラー信号を与えるエラー注入回路、第1と第2の論理部の出力を入力し選択した信号を与える選択回路と第1と第2の論理部の出力を比較し、比較不一致信号を与える比較回路とを備えた比較補正回路から構成され、比較補正回路は、第1と第2の論理部のいずれかにエラー信号を与えた時、第1と第2の論理部の出力が不一致にならない場合、または、第1と第2の論理部にエラー信号を与えないときに、第1と第2の論理部の出力が不一致になる場合に異常があると判断する。

(もっと読む)

集積回路、集積回路装置及び伝送システム

【課題】回路遅延の増大を抑制しながら、回路しきい値電圧のバラツキを抑制できる集積回路を提供する。

【解決手段】

集積回路1は、高位側電源VDDと出力端子OUTの間に接続されたPMOSトランジスタMP1と、低位側電源VSSと出力端子OUTの間に接続されたNMOSトランジスタMN1と、高位側電源VDDと出力端子OUTの間に直列に接続されたPMOSトランジスタMP2及びNMOSトランジスタMN3と、低位側電源VDDと出力端子OUTの間に直列に接続されたNMOSトランジスタMN2及びPMOSトランジスタMP3とを備えている。PMOSトランジスタMP1、MP2、及びNMOSトランジスタMN1、MN2のゲートが入力端子INに接続されている。また、NMOSトランジスタMN3のゲートは高位側電源に接続され、PMOSトランジスタMP3のゲートは低位側電源に接続されている。

(もっと読む)

半導体集積回路装置

【課題】構成を簡略化して消費電力を低減させることができる交流電源駆動の半導体集積回路装置を提供する。

【解決手段】入力信号に応じた論理計算を行わない任意の負荷1aと当該負荷1aに直列に接続し、入力信号に応じた論理計算を行う第1の計算部2aとを備える第1のロジック演算部10aと、同様の構成で第1の計算部2aの代わりに第1の計算部2aの計算結果と相補的な計算結果が得られるような論理計算を行う第2の計算部2bとを備え、前記第1のロジック演算部10aと並列に接続される第2のロジック演算部10bと、第1のロジック演算部10a及び第2のロジック演算部10bの間に接続され、演算された計算結果を保持する保持回路5と、第1のロジック演算部10a及び第2のロジック演算部10bに高電圧と低電圧とを相補的に変化させて印加する交流電源3とを備え、論理計算の処理と、計算結果を増幅させて出力する処理とが半周期ごとに交互に実行される。

(もっと読む)

論理回路

【課題】安定した高速動作を実現しつつ、製造工程も簡素化することが可能な論理回路を提供すること。

【解決手段】この論理回路1は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2のFET2A,2Bを備える論理回路であって、第1及び第2のFET2A,2BのうちのFET2Aは、ゲート端子が接続されるゲート電極膜17と、半導体材料からなるチャネル層12と、ゲート電極膜17とチャネル層12との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層16と、を有する。

(もっと読む)

ラッチ回路

【課題】回路面積が小さく、かつ省電力化したラッチ回路を提供する。

【解決手段】複数の論理回路(第1の論理回路11、第2の論理回路13、第3の論理回路15、及び第4の論理回路17)によりラッチ回路1を構成し、選択信号の論理レベルに応じて差動動作とシングルエンド動作の切り替えを行う。また、これらの複数の論理回路11,13,15,17へのクロック入力信号に応じて個々の論理回路をON状態又はOFF状態にすることで、差動動作とシングルエンド動作それぞれにおいてスルー動作とホールド動作をさせる。

(もっと読む)

半導体装置

【課題】消費電力を小さくでき、トランジスタ数が少ない半導体装置を提供する。

【解決手段】ソース及びドレインの一方が第1の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース及びドレインの一方が第1の配線と電気的に接続され、ゲートが第1のトランジスタのゲートと電気的に接続された第2のトランジスタと、一方の電極が第3の配線と電気的に接続され、他方の電極が第2のトランジスタのソース及びドレインの他方と電気的に接続された容量素子と、を有する。

(もっと読む)

半導体回路

【課題】耐放射線特性の優れた半導体回路を提供することを目的とする。

【解決手段】複数のpMOSトランジスタ11,12を直列に接続した第1の回路ブロック1と、複数のnMOSトランジスタ21,22を直列に接続した第2の回路ブロック2とを備え、少なくとも1つの前記pMOSトランジスタ12のゲート及び/又は少なくとも1つの前記nMOSトランジスタ21のゲートを入力端子Vinに接続し、少なくとも1つの他のpMOSトランジスタ11のゲート及び/又は少なくとも1つの他のnMOSトランジスタ22のゲートに、オン電圧を印加する半導体回路。

(もっと読む)

論理回路及びデータ処理システム

【課題】素子数が少なく、遅延が小さく、ドライバ能力を有するXORゲート回路を提供する。

【解決手段】論理回路1は、電源電位VPERIとノードn1の間に接続されたトランジスタT1と、電源電位VPERIとノードn2の間に接続されたトランジスタT2と、電源電位VSSとノードn3の間に接続されたトランジスタT3と、電源電位VSSとノードn4の間に接続されたトランジスタT4と、ノードn1とノードn3の間に直列接続されたトランジスタT5,T7と、ノードn1とノードn3の間に直列接続されたトランジスタT9,T11と、ノードn2とノードn4の間に直列接続されたトランジスタT6,T8と、ノードn2とノードn4の間に直列接続されたトランジスタT10,T12とを備える。出力信号Yは、トランジスタT5,T7の接続点及びトランジスタT6,T8の接続点から取り出される。

(もっと読む)

半導体装置

【課題】信号伝送のより高速化を図る。

【解決手段】入力信号Vinと基準信号Vrefとを入力する第1の差動対(Q3、Q4が相当)と、第1の差動対のそれぞれ負荷となる第1及び第2のトランジスタQ2、Q1と、を含む第1の入力回路を備え、第1の入力回路の出力側となる第1のトランジスタQ2は、第2のトランジスタQ1に比べてゲート幅を長くする。

(もっと読む)

CMOS論理回路

【課題】貫通電流を抑制しつつ、ドライブ能力を向上することが可能なCMOS論理回路を提供する。

【解決手段】CMOS論理回路は、第1の電圧線に一端が接続され、印加される電圧に対して非線形となるインピーダンス特性を有する抵抗性素子と、第1、第2のMOSトランジスタで構成される第1のインバータ回路を備える。CMOS論理回路は、第3、第4のMOSトランジスタからなる第2のインバータ回路を備える。CMOS論理回路は、抵抗性素子と並列に接続され、ゲートが第3のMOSトランジスタP2の他端に接続された第5のMOSトランジスタを備える。CMOS論理回路は、第1の電圧線と第1の出力端子との間に接続され、ゲートが第3のMOSトランジスタの他端に接続された第6のMOSトランジスタを備える。

(もっと読む)

トランジスタ回路、双方向スイッチ回路、ダイオード回路及びトランジスタ回路の製造方法

【課題】トランジスタのゲートへの電流を防ぐ。

【解決手段】ノーマリーオン型の第1トランジスタと、ドレインが、第1トランジスタのソースと接続され、第1トランジスタとカスコード接続されたノーマリーオフ型の第2トランジスタと、第2トランジスタのソースと第1トランジスタのゲートとの間に設けられた、第2トランジスタのソースから第1トランジスタのゲートへと流れる電流を抑制する第1電流抑制部とを備えるトランジスタ回路を提供する。

(もっと読む)

ロジック回路及び携帯端末装置

【課題】DVDD系ロジック回路とRVDD系ロジック回路との間のアイソレートを実施しながら、小型化及び低コスト化を実現する。

【解決手段】第一のデジタル回路と第二のデジタル回路とを含むロジック回路であって、第一のデジタル回路の動作電圧である第一の電圧値を検出する第一の検出手段と、第二のデジタル回路の動作電圧である第二の電圧値を検出する第二の検出手段と、第一の電圧値と第二の電圧値とを比較する比較手段と、比較手段により得られた比較結果に応じて、第一のデジタル回路と第二のデジタル回路との間の分離結合を行う分離結合手段と、を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】素子面積の増加を抑制しつつ、動作速度が向上する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置は、ボディ領域11a、11bと、ボディ領域11a、11b上にゲート絶縁層12a、12bを介して配置されるゲート電極13a、13bと、ボディ領域11a、11bを挟んで配置される一対のソース/ドレイン領域14a、14b、14cと、を有する電界効果型トランジスタ10a、10bを複数備え、複数のトランジスタ10a、10bは、ボディ領域11a、11b同士が電気的に接続されており、複数のトランジスタ10a、10bの内の一のトランジスタ10aのゲート電極13aのみが、複数のトランジスタ10a、10bの内の何れかのトランジスタのボディ領域と電気的に接続される。

(もっと読む)

半導体回路

【課題】本発明は、ハイレベルの入力信号に混入されたローレベルのノイズ及びローレベルの入力信号に混入されたハイレベルのノイズをより効果よく取り除くことができる半導体回路を提供する。

【解決手段】 入力信号を所定時間遅延して出力する遅延部120、220、320と、該入力信号のレベルによって電圧を充放電させる電圧調整部140、240、340と、該入力信号のレベル及び遅延部120、220、320から出力される信号のレベルを用いて生成された信号によって、電圧調整部140、240、340の充放電動作を制御する組合せ部160、260、360とを含む。

(もっと読む)

ニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器

【課題】回路規模の増大を抑制し、低消費電力化を実現するフラッシュ型AD変換器を提供すること。

【解決手段】本発明の一実施形態によると、第1のCMOS回路と、共通するローティングゲートを有し、3個のゲートが前記フローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路とに並列に接続する2n−1−1個(nは3以上の整数)のニューロンCMOS回路と、を備える量子化出力部と、前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、前記量子化出力部又は前記エンコード部に接続するn個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器が提供される。

(もっと読む)

半導体集積回路,および,半導体集積回路の検査方法

【課題】故障検査のために観測用フリップフロップ回路を配置することなく,故障検査を可能とする半導体集積回路,その検査方法を提供する。

【解決手段】第2の論理回路51の試験の際に試験モードを示す制御信号TSMが,故障検査用回路41に入力され,この試験モードに対応するテスト値が,論理回路51に入力されると,故障検査用回路41により,論理回路51の出力論理が,論理回路13に対応するフリップフロップ回路14に入力される。さらに,通常モード時に,論理回路13の出力論理が,故障検査用回路41により,論理回路13に対応するフリップフロップ回路14にそのまま入力される。

(もっと読む)

加算器

【課題】新たなロジックインメモリ構造を提供する。また、より消費電力の低い信号処理回路を提供する。また、より消費電力の低い電子機器を提供する。

【解決手段】オフ電流の低いトランジスタを用いて記憶素子を構成することで、記憶機能と演算機能を組み合わせた回路を提供する。オフ電流の低いトランジスタを用いることで、オフ電流の低いトランジスタのソースまたはドレインの一方と、他のトランジスタのゲートとの間などに電荷を保持することができる。そのため、オフ電流の低いトランジスタのソース又はドレインの一方と、他のトランジスタのゲートと、の間のノード等を記憶素子として用いることができる。また、加算器の動作に伴うリーク電流を著しく低減することができる。これにより、消費電力の低い信号処理回路を構築することが可能である。

(もっと読む)

半導体集積回路

【課題】電源が遮断されてもデータが保持される新規な論理回路を提供する。また、消費電力を低減できる新規な論理回路を提供する。

【解決手段】2つの出力ノードを比較する比較器と、電荷保持部と、出力ノード電位確定部とを電気的に接続することにより、論理回路を構成する。それにより、電源が遮断されてもデータが保持される論理回路を得ることができる。また、論理回路を構成するトランジスタの総個数を低減させることができる。更に、酸化物半導体を用いたトランジスタとシリコンを用いたトランジスタを積層させることで、論理回路の面積の削減が可能になる。

(もっと読む)

1 - 20 / 504

[ Back to top ]