Fターム[5J056AA33]の内容

論理回路 (30,215) | 回路の種類 (3,583) | インターフェース、レベルシフト、レベル変換 (1,016) | 振幅縮小 (38)

Fターム[5J056AA33]に分類される特許

1 - 20 / 38

入力回路

【課題】高電位信号を低電位信号に変換する入力回路であって、適切なターゲット反転電位で動作可能な入力回路を提供する。

【解決手段】入力回路は、高電源電位が入力される入力端子とグランド端子との間に接続された抵抗と、抵抗中の第1ノードに接続された第2ノードと、第2ノードと第3ノードとの間に接続されたインバータと、抵抗を通した入力端子とグランド端子との間の電気的接続をON/OFF制御するスイッチと、を備える。ターゲット反転電位は、インバータの反転電位よりも高い。入力端子の電位がターゲット反転電位の場合、第2ノードの電位がその反転電位となる。第2ノードの電位が反転電位より低い場合、インバータは低電源電位を第3ノードに出力し、且つ、スイッチは上記の電気的接続をONする。一方、第2ノードの電位が反転電位より高い場合、インバータはグランド電位を第3ノードに出力し、且つ、スイッチは上記の電気的接続をOFFする。

(もっと読む)

半導体装置

【課題】信号転送ラインの充放電によって消費される電力を低減する。

【解決手段】フリップフロップ構成のアンプ回路AMPを含むレシーバ回路R0kと、データバスDBとレシーバ回路R0kの入力端T2との間に挿入され、データバスDBがVPERI−NVthに達するとオフするトランジスタM7を備える。本発明によれば、トランジスタM7によって入力端T2の振幅が制限されることから、データバスDBがローレベルからハイレベルに変化する際の転送速度が向上する。しかも、アンプ回路AMPがフリップフロップ構成を有していることから、フリップフロップが反転した後は貫通電流が生じない。これにより、消費電力がより一層低減される。

(もっと読む)

半導体装置

【課題】スタンバイ時のリーク電流と回路面積の増大を抑制する。

【解決手段】第1電源に接続する第1の回路11の入力対に出力が夫々接続された第2及び第3の回路12、13と、前記第1の回路の入力、又は、前記第1の回路の内部ノードに接続された第4の回路14と、を含み、前記第2の回路及び前記第3の回路は、第2電源と第3電源間に接続され、スタンバイ時にパワーゲーティングされる回路を有し、前記第2の回路は、前記第2及び第3電源電位を振幅範囲とする信号を入力し、前記第2の回路の出力は前記第3の回路の入力に接続され、前記第1の回路の出力信号の振幅範囲は、前記第1電源電位と、前記第2又は第3電源電位とされ、前記第4の回路は、パワーゲーティング時に前記第1の回路の前記入力対、又は前記内部ノードの論理値を保持し、スタンバイ時にも前記第1の回路の出力信号の論理を前記入力信号に関連した論理に維持する。

(もっと読む)

レベルシフト回路

【課題】レベルシフト回路における、低電圧動作、高耐圧、低消費電流、高速動作、検査容易化を目的とする。

【解決手段】第1のレベルシフト要素(1)として、低い電圧の場合に電源ONで動作状態として用い、電源電圧が高い場合には素子の耐圧を確保して電源OFFし停止状態で用いる低電源電圧用レベルシフト回路を備え、第2のレベルシフト要素(2)として、電源電圧が低い場合には電源OFFし停止状態で用い、電源電圧が高い場合に、素子の耐圧を確保して電源ONし動作状態で用いる高電源電圧用レベルシフト回路とを備え、電源電圧によって切り替えられるように構成する。

(もっと読む)

半導体集積回路装置

【課題】論理機能を有するシステムの小型化を図る。

【解決手段】第1電源電圧が印加される第1外部入力端子、第2電源電圧が印加される第2外部入力端子、第1入力信号が印加される第3外部入力端子、第2入力信号が印加される第4外部入力端子、接地電位が印加される第5外部入力端子及び信号を出力するための外部出力端子を有する。更に、第3外部入力端子からの信号を入力し信号レベルを変換して出力するレベルシフト回路及びその回路の出力信号を入力して外部出力端子に出力し第2入力信号に応じて出力をハイインピーダンス状態にすることが可能なトライステートバッファ回路を有する。レベルシフト回路は前段及び後段部分から構成され、第1電源電圧は前段部分の電源電圧として、第2電源電圧は後段部分及びトライステートバッファ回路の電源電圧として供給される。接地電圧はレベルシフト回路及びトライステートバッファ回路の接地電圧とされる。

(もっと読む)

レベル変換回路

【課題】安定したレベル変換を行う。

【解決手段】回路ブロック21,22は、それぞれ、ノードN14、N15に現れる電位0Vと電位HVとにより2つの論理値0,1が表される高電圧の論理信号を、電位VGと電位(VG+LL)とにより2つの論理値0,1が表される低電圧の論理信号に変換し、出力端子Poutから、この論理信号を出力する。回路ブロック22の各トランジスタは、回路ブロック21のそれらを逆極性の素子で置き換えた形となっており、電位VGを変化させたときに回路ブロック21,22のいずれかの動作が困難になった場合でも、もう一方が正常に動作する。このため、安定したレベル変換を行うことができる。

(もっと読む)

レベルシフト回路

【課題】低消費電力で高速動作が可能なレベルシフト回路を提供する。

【解決手段】レベルシフト回路は、タイミング制御回路1と、充電回路2と、放電回路3と、電圧保持回路4と論理合わせ回路5とを有する出力信号生成回路6とを備えている。出力信号Voutの論理を決定するために電流駆動力が大きいトランジスタQ21とトランジスタQ31とを縦続接続し、これらトランジスタQ21とトランジスタQ31とに貫通電流が流れないようにタイミング制御回路1がトランジスタQ21とトランジスタQ31のオン・オフを制御するため、トランジスタQ21およびトランジスタQ31が同時にオン状態となることはない。よって、低電源電圧端子から、トランジスタQ21およびトランジスタQ31を通して、接地端子へ貫通電流が流れることがなく、レベルシフト回路は低消費電力で高速動作が可能である。

(もっと読む)

半導体集積回路

【課題】 本発明は、位相比較回路に入力されるクロック信号のうち、第1クロック信号から伝播するクロック信号と、第2クロック信号(CK2)から伝播するクロック信号との間で、伝搬遅延の差異をなくし、位相差の調整にあたり誤差が抑制される半導体集積回路を提供することを目的とする。

【解決手段】 本発明は、第1クロック信号に基づいて動作する第1回路と、第2クロック信号に基づいて動作する第2回路と、第1クロック信号に対応した信号の位相と第2クロック信号に対応した信号の位相とを比較する位相比較回路と、第1クロック信号が位相比較回路に至る経路に介在し、第1クロック信号の電圧レベルを変更する第1のレベルシフト回路と、第2クロック信号が位相比較回路に至る経路に介在し、第1のレベルシフト回路と同じ回路構成を有する第2のレベルシフト回路とを備え、位相比較回路による比較結果に応じて第1クロック信号と第2クロック信号との位相差を調整する。

(もっと読む)

レベルシフト回路およびそれを備えた半導体装置

【課題】高い信頼性や、高速性を備えたレベルシフト回路を実現する。

【解決手段】例えば、高電圧レベル(電源電圧VCCHのレベル)の入力信号INを低電圧レベル(電源電圧VCCLのレベル)の出力信号OUTに変換するレベルシフト回路LS1において、カップリングノイズを抑制するためのNMOSトランジスタMN4を設ける。INが‘H’レベルから‘L’レベルに遷移した際には、NMOSトランジスタMNH1の寄生容量(CGD)を介して、そのドレインとなるノードNDE1にアンダーシュートが生じ得るが、それをMN4からの電流I1によって抑制する。これにより、PMOSトランジスタMPL1,MPL2を薄膜仕様としてもその耐圧を満たすことができ、薄膜仕様に伴い高速動作が実現できる。

(もっと読む)

スイッチング素子の駆動回路

【課題】dv/dt耐量を満足するレベルシフト回路を提供し、高信頼性のインバータ回路を提供すること。

【解決手段】主電源23の両端に、上アーム232のスイッチング素子IGBT24及び下アーム233のスイッチング素子であるIGBT25が、トーテムポール接続され、ハーフブリッジを構成している。上アーム232のIGBT24を駆動制御する駆動回路のパルス発生回路31はパルス状のオン、オフ信号を発生させ、レベルシフト用の高耐圧nMOS32、及び高耐圧nMOS33のゲート電極に与えられる。高耐圧nMOS32、及び高耐圧nMOS33のドレイン電極はそれぞれレベルシフト用抵抗34及び35の一方端に接続されるとともに、抵抗34と高耐圧nMOS33,抵抗35と高耐圧nMOS32の接続点の電位は、それぞれセット用の差分回路11及びリセット用の差分回路12に入力され正規の信号レベルか否かを判断される。

(もっと読む)

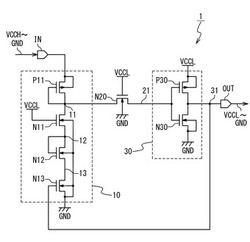

レベルシフト回路

【課題】 レベルシフト回路において電源電圧の異なる第1および第2の回路に共通電位を与える電源線にノイズが発生しても出力信号にノイズの影響が現れないようにする。

【解決手段】 第1の回路10および第2の回路20には、第1および第2の電源電圧が与えられる。第2の回路20において、NチャネルトランジスタM6は、第1の回路10および第2の回路20に共通の電位を与える低電位電源線202に接続され、第1の回路10の出力信号BによりON/OFFが切り換わる。NチャネルトランジスタM6にはNチャネルトランジスタM9が直列接続され、第2の回路20では、このNチャネルトランジスタM6およびM9の接続点の電圧に基づいて出力信号OUTを発生する。第3の回路30は、第1の回路10の出力信号Bの論理値を反転した論理値を有し、第1の電源電圧と同じ振幅を持った信号によりNチャネルトランジスタM9のON/OFF状態を切り換える。

(もっと読む)

昇圧回路、および降圧回路

【課題】入力電圧を昇圧して出力する半導体集積回路における、トランジスタの耐圧が、入力電圧以下に抑えられる昇圧回路を提供する。

【解決手段】コンデンサCpは、一方の端子がクロック信号を出力するクロック端子に接続され、他方の端子が整流回路4に接続されている。コンデンサCpの他方の端子の最低電圧を第1の電圧にクランプするクランプ回路3を備えている。このクランプ回路3は、第1のN型トランジスタN1、および第2のN型トランジスタN2を有している。この第1のN型トランジスタN1は、ドレインをコンデンサの他方の端子に接続し、ソースを前記第2のN型トランジスタN2のドレインに接続し、さらに、ゲートを第1の電圧よりも高い第2の電圧Vaに接続している。また、第2のN型トランジスタN2は、ソースを第1の電圧Vpに接続し、ゲートを前記クロック信号の反転信号を出力する反転信号端子に接続している。

(もっと読む)

高信号レベル対応入出力回路

(213)は、特定レベルを検出するためのマルチ信号レベルの信号を受け付けるように適合された入力回路(M6,M6,M7)を持つ。これらの信号レベルは、第1信号レベルおよび、より大きな第2信号レベルを含む。入力回路の電子構成要素は、第2信号レベルよりも低い信頼性レベルを持っている。ラッチ回路(710)は、受け付けられた信号の検出レベルに合致する信号をラッチするために、入力回路(M6,M6,M7)に結合される。  (もっと読む)

(もっと読む)

ワードライン電圧及びメモリ・セル性能を増強するためのレベル・シフタ

【課題】 ワードライン電圧及びメモリ・セル性能を増強するためのレベル・シフタを提供する。

【解決手段】 回路及び方法は、第1電源電圧によって電力供給される第1回路と、第2電源電圧によって電力供給される第2回路とを含む。レベル・シフタが、第1回路と第2回路との間に接続される。レベル・シフタは、少なくとも1つの実行すべき動作と動作を実行するコンポーネントとに依存する入力信号に従って、第1電源電圧及び第2電源電圧のうちの1つを含む回路に対する電源電圧出力を選択するように構成される。

(もっと読む)

レベルシフト回路用入力回路

【課題】 低コストとなる低耐圧トランジスタのみを使用し、高電圧(VH)の入力に対し、VH/2近辺で反転動作することが可能な入力回路を提供する。

【解決手段】 高電圧の入力信号が、ドレインに接続されたPMOS(P02)とNMOS(N02)に与えられ、PMOS(P02)のソースはPMOS(P00)のゲートに接続され、NMOS(N02)のソースはNMOS(N00)のゲートに接続される。前記のMOS(P02)、(N02)のゲートはVCCLに接続され、PMOS(P00)のソースは高電源電圧に接続され、NMOS(N00)のソースは接地電位に接続され、PMOSトランジスタ(P00)のドレインはPMOS(P01)のソースに接続され、NMOS(N00)のドレインはNMOS(N01)のソースに接続される。前記の(P01)、(N01)のゲートはVCCLに接続され、前記の(P01)、(N01)のドレインがともに接続され、高電圧入力を低電圧出力にレベルシフトする回路の入力となる。

(もっと読む)

低電圧での能力を備えた高速出力回路

【課題】1つの電圧レベル(たとえば、より低い電圧レベル)で入力信号を受入れかつ別の電圧レベル(たとえば、より高い電圧レベル)で出力信号を提供することができ、高い動作スピードを維持する出力回路を提供する。

【解決手段】 性能を犠牲にすることなく、さまざまな入力および出力電圧レベルとの互換性を提供する出力回路。出力端子上のプルアップ(P12)は内部ノード(PD)によってゲートされ、この発明はデータ入力信号をこの内部ノード(PD)に与えるためのさまざまな回路および手段を含む。一実施例は、データ入力経路上にレベルシフタ(100)を含み、レベルシフタをバイパスし出力回路を通る代替の経路も提供する。入力データの値がハイになると、代替の経路は減衰されたハイの値を内部ノードに素早く与える。レベルシフタはアクティブになり、内部ノードの電圧を出力パワーハイレベルに上昇させ、出力プルアップ(P12)が完全にオフされるようにする。

(もっと読む)

インタフェース回路および信号出力調整方法

【課題】伝送路の減衰量を考慮して送信側の信号の振幅を調整することのできるインタフェース回路および信号出力調整方法を得ること。

【解決手段】インタフェース回路100の送信側回路部分では、テスト時に一定振幅の繰り返し信号111をCML回路で構成される出力バッファ回路117を経て伝送路123に送出する。受信側回路部分102では、これによる入力信号131の振幅を判定回路135が複数の基準電圧Vref1〜Vrefnとコンパレータ1321〜132nで比較することにより求める。そして送信側回路部分101側の電圧制御回路119で、CML回路の定電流値を適切に制御することで振幅の設定を行って低消費電力化を実現する。

(もっと読む)

高速低電力差動受信機RobertE.PalmerJohnW.Poulton

低電圧差動通信システムには、差動チャネルを介して低電圧差動信号を受信機に伝達するプログラム可能な低振幅電圧モード送信機が含まれる。受信機は、2つの入力トランジスタ(それぞれは共通ゲート構成である)を用いて、低電圧差動信号を回復する。受信機における電流源は、入力トランジスタをバイアスし、それらのソース電圧が、差動信号の共通モード電圧において公称上バイアスされ、かつそれらのゲート−ソース電圧が、共通モード電圧変動に対してほぼ一定のままであるようにする。  (もっと読む)

(もっと読む)

インターフェース回路、およびこれを用いた回路システム

【課題】各種デバイス間でインターフェース電圧の相異がある場合でも、デバイス間の信号授受のときに動的にそのインターフェース電圧の相異を吸収する。

【解決手段】複数のデバイスが共通接続線を介して信号を授受するとき、デバイスと共通接続線との間に介在するインターフェース回路であって、デバイスから前記共通接続線への信号の出力時に、デバイス内での信号レベルを共通接続線で授受されるデバイスに相応の信号レベルに変換する出力変換部、および、共通線からデバイスへの信号の入力時に、共通接続線で授受されるデバイスに相応の信号レベルをデバイス内での信号レベルに変換する入力変換部の少なくとも一方を備える。

(もっと読む)

ドライバ回路

【課題】 従来のドライバ回路では、CML回路の出力振幅や中点電圧等の出力電圧を制御することが困難であった。さらに、従来のドライバ回路では、CML回路における出力電圧のハイレベルが電源電圧からドロップしていた。

【解決手段】 ドライバ回路は、差動入力信号の振幅を変換して差動出力信号を出力する振幅変換部と、前記差動出力信号の振幅を設定する振幅設定部と、前記差動出力信号の振幅の中心値を設定するコモン電圧設定部とを有する。

(もっと読む)

1 - 20 / 38

[ Back to top ]