Fターム[5J056CC01]の内容

Fターム[5J056CC01]に分類される特許

1 - 20 / 480

複数の集積回路にインタフェース信号を供給する方法および回路

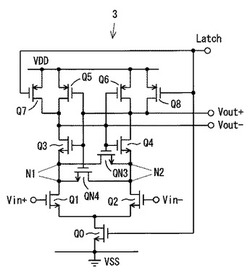

ラッチト・コンパレータ

【課題】差動回路の特性を損なうことなく、高速に信頼性の高いラッチ出力を行うラッチト・コンパレータを提供する。

【解決手段】ラッチト・コンパレータ(1)は、ドレイン・ソース間が、第1の電流経路上の第1のMOSトランジスタ(Q1)と第3のMOSトランジスタ(Q3)との間の第1のノード(N1)と、第2の電流経路上の第2のMOSトランジスタ(Q2)と第5のMOSトランジスタ(Q4)との間の第2のノード(N2)との間に接続されているとともに、ゲートが第1のCMOSインバータの出力に接続された、第7のMOSトランジスタ(QN3)と、ドレイン・ソース間が第1のノード(N1)と第2のノード(N2)との間に接続されているとともに、ゲートが第2のCMOSインバータの出力に接続された、第8のMOSトランジスタ(QN4)と、の少なくとも一方をさらに備えている。

(もっと読む)

ドライバ回路および試験装置

【課題】出力信号の応答特性および消費電流を一定にする。

【解決手段】入力信号の論理に応じた電圧の出力信号を出力するドライバ回路であって、定電圧のバイアス電圧を発生する定電圧発生部と、内部に流れる定電流の電流値に応じて出力信号の振幅が定まり、バイアス電圧の電圧値に応じて出力信号の電位が定まり、入力信号の論理に応じた電圧の出力信号を出力する電流モードロジック回路と、定電圧発生部におけるバイアス電圧の出力端から、設定された電流値の定電流を流し出す調整用定電流源と、電流モードロジック回路内に流れる定電流の電流値に応じて、調整用定電流源に流す定電流の電流値を予め設定する電流設定部とを備えるドライバ回路を提供する。

(もっと読む)

半導体装置

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な

振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路1

60を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路1

60に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場

合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能

とする。

(もっと読む)

ソースフォロア回路

【課題】複数段構成におけるソースフォロア回路において入出力レンジを確保する。

【解決手段】ソースフォロア部SF11、SF12間に、ゲートドレイン間がダイオード接続され且つソースフォロア部SF11およびSF12を構成するMOSトランジスタM11およびM12と同一チャネル種類のMOSトランジスタM13とそのドレインに接続された電流源C13とからなる接続部11を設け、前段のソースフォロア部SF11の出力端とMOSトランジスタM13のソースとを接続し、MOSトランジスタM13のドレインと後段のソースフォロア部SF12の入力端とを接続する。接続部11における入出力間の電圧レベルのシフト方向は、ソースフォロア部SF11、SF12における入出力間の電圧レベルのシフト方向と逆となり、電圧シフトを打ち消す方向に作用するため、電圧レベルのシフトにより入出力レンジが狭くなることを抑制することが可能となる。

(もっと読む)

出力ドライバー回路

【課題】nMOSトランジスタM2のゲート−ソース間に加わる電圧を耐圧電圧未満に制限する際に消費電流の増加を抑制する。

【解決手段】pMOSトランジスタM1がオフし、かつnMOSトランジスタM2がオンしたとき、ツェナーダイオードZD2により、nMOSトランジスタM2のゲート端子とソース端子との間の電圧を一定電圧に制限する。nMOSトランジスタM2のゲート端子とソース端子との間に耐圧電圧よりも高い電圧が加わることを避けることが可能になる。このとき、定電流電源20bが電源からツェナーダイオードZD2を通してグランドに流れる電流を制限する。電源からトランジスタM3、M5b、M6bを通してnMOSトランジスタM2のゲート端子に流れる電流をnMOSトランジスタM6bが制限する。

(もっと読む)

レベルシフト回路

【課題】占有面積が小さく、温度変化や素子のバラツキの影響を受け難く、さらに、ノイズを低減することで高品位のレベルシフトを実現することができるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、主に、第1の信号(VIN)をレベルシフトして第2の信号(Vm)を出力するレベルシフト部10と、pMOSトランジスタ32aとnMOSトランジスタ32bを含み、第2の信号を反転させた第3の信号(S1)を出力するCMOSインバータ回路部32、偶数個のインバータ素子(第1のインバータ33a〜第mのインバータ33m)を含み、第3の信号を遅延させた第4の信号(S3)を生成する遅延回路部33、論理素子を含み、第3の信号及び第4の信号が入力して第5の信号(S5)を出力する論理回路部34、及び第4の信号と第5の信号が入力するD−FF素子35、を含む出力バッファ部30と、を備える。

(もっと読む)

半導体装置及び電子機器

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な

振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路1

60を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路1

60に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場

合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能

とする。

(もっと読む)

出力回路、信号伝送回路及び信号伝送方法

【課題】電源ノイズの低減を図ることができる出力回路を提供する。

【解決手段】本発明の実施の形態に係る出力回路Oは、論理信号を出力するCMOS回路OAと、CMOS回路OAと同じ論理信号を出力する、CMOS回路OAと並列に設けられた電流一定回路OBと、入力される選択信号Sに応じて、CMOS回路OAと電流一定回路OBのいずれか一方にデータDを入力し、データDに応じた論理信号を出力させる選択回路SLとを備え、電源ノイズを許容値以下に抑える必要がある場合に、電流一定回路OBを選択する。

(もっと読む)

信号出力回路

【課題】広いダイナミックレンジと良好な周波数特性を得ることができる信号出力回路を提供する。

【解決手段】実施形態の信号出力回路は、ゲート端子へ一定の電圧Vgが印加され、ソース端子へ入力信号INが印加されるゲート接地型のNMOSトランジスタ1と、ゲート端子がNMOSトランジスタ1のドレイン端子に接続され、ソース端子から出力信号OUTが出力されるソースフォロワであるNMOSトランジスタ2とを備える。この信号出力回路は、バックゲートバイアス生成部3が、NMOSトランジスタ1およびNMOSトランジスタ2のバックゲート端子へ印加する共通のバックゲートバイアス電圧Vbを生成する。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、エンファシスの有無により消費電流が変動する問題があった。

【解決手段】本発明の半導体装置は、抵抗値を、エンファシスモードにおいて第1の抵抗値とし、非エンファシスモードにおいて第1の抵抗値よりも小さな第2の抵抗値とする可変抵抗30と、出力インピーダンスを、エンファシスモードにおいて第3の抵抗値とし、非エンファシスモードにおいて前記第3の抵抗値よりも大きな第4の抵抗値とする第1の駆動部10と、出力インピーダンスを、エンファシスモードにおいて第5の抵抗値とし、非エンファシスモードにおいて第5の抵抗値よりも大きな第6の抵抗値とする第2の駆動部11と、入力信号に応じて第1、第2の駆動部の導通状態を制御すると共に、エンファシスモードと非エンファシスモードとにおいて第1、第2の駆動部の出力インピーダンスと可変抵抗の抵抗値を切り換える制御部と、を有する。

(もっと読む)

小振幅差動パルス送信回路

【課題】最適の時期に出力電流を流して、それ以外の時期には出力電流を止めることによって省エネ性能に優れた小振幅差動パルス送信回路を提供すること。

【解決手段】定電流を送信データに応じて差動的に出力する定電流差動出力回路101と、前記定電流差動出力回路101の出力を、送信データの値の変化による該出力の過渡現象が収束した後であって次のデータが出力される前における所定期間通過させるスイッチ回路102と、前記スイッチ回路102の出力を所定電位にバイアスするバイアス回路103とを備える小振幅差動パルス送信回路。

(もっと読む)

半導体装置

【課題】信号伝送のより高速化を図る。

【解決手段】入力信号Vinと基準信号Vrefとを入力する第1の差動対(Q3、Q4が相当)と、第1の差動対のそれぞれ負荷となる第1及び第2のトランジスタQ2、Q1と、を含む第1の入力回路を備え、第1の入力回路の出力側となる第1のトランジスタQ2は、第2のトランジスタQ1に比べてゲート幅を長くする。

(もっと読む)

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

出力駆動回路及びトランジスタ出力回路

【課題】本発明は、出力駆動回路及びトランジスタ出力回路を提供する。

【解決手段】第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタ111を含む第1の駆動回路部110と、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作によって生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む第2の駆動回路部130と、第1の駆動回路部110と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部150とを含む。

(もっと読む)

電子回路、および実装基板

【課題】出力信号の電圧レベルの遷移の方向に応じて、電源線や接地線を通らず寄生インダクタンス成分の影響を受けない電流を加算して信号の電圧レベルの遷移をアシストすることにより、SSOノイズを抑制することが可能な電子回路および実装基板の制御方法を提供すること。

【解決手段】出力回路1は、出力バッファ4と、出力バッファ4から出力される出力信号が伝搬する出力線と、出力バッファ4に電源を供給する電源線VdeLあるいは接地線VgLの少なくとも何れか一方と、出力線と電源線VdeLあるいは接地線VgLとにより囲まれる磁心50と、磁心50に巻回される制御コイル51と、出力信号の遷移を前もって検出し検出結果に応じて制御コイル51への電流供給を制御するコイル電流制御回路3とを備え、出力信号の遷移方向に応じて、制御コイル51からの電磁誘導により出力線の信号遷移をアシストするアシスト電流を流す。

(もっと読む)

半導体回路

【課題】本発明は、ハイレベルの入力信号に混入されたローレベルのノイズ及びローレベルの入力信号に混入されたハイレベルのノイズをより効果よく取り除くことができる半導体回路を提供する。

【解決手段】 入力信号を所定時間遅延して出力する遅延部120、220、320と、該入力信号のレベルによって電圧を充放電させる電圧調整部140、240、340と、該入力信号のレベル及び遅延部120、220、320から出力される信号のレベルを用いて生成された信号によって、電圧調整部140、240、340の充放電動作を制御する組合せ部160、260、360とを含む。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを出力する電圧出力回路100と、制御信号SCに基づいて電圧出力回路100を制御する制御回路210と、第1の電源電圧VP及び第2の電源電圧VMの少なくとも一方の振幅に応じて変化する制御信号SCを生成して制御回路210に出力する制御信号生成回路240とを含む。制御回路210は、制御信号SCに基づいて、電圧出力回路100から出力される第1の電源電圧VP及び第2の電源電圧VMの振幅を可変に制御する。

(もっと読む)

出力回路

【課題】差動出力電圧の振幅のばらつきを抑制した出力回路を提供する。

【解決手段】出力回路は,定電圧ノードと基準電源との間に,複数のスイッチ素子のオン,オフにより合成抵抗値が可変制御可能な複数の抵抗を有し,定電圧ノードに第1の電流を生成する定電流生成回路と,第1の電流をカレントミラーにより生成した第2の電流を,内部回路から供給される内部差動信号に応じて,出力端子対に出力する出力駆動回路と,出力端子対の出力差動電圧の差が所望の電圧差と一致するように,定電流生成回路の複数のスイッチ素子を制御するスイッチ素子制御信号を生成する出力振幅調整部とを有する。

(もっと読む)

出力バッファ回路

【課題】 著しい遅延の増大を招くことなく、出力バッファ回路の貫通電流を防止する。

【解決手段】 出力段駆動部100は、出力信号VOUTを立ち下げる場合、Pチャネルトランジスタ201をOFFに遷移させ、そのドレイン電流が閾値電流Ith1を下回ったとき、Nチャネルトランジスタ202をONに遷移させ、出力信号VOUTを立ち上げる場合、Nチャネルトランジスタ202をOFFに遷移させ、そのドレイン電流が閾値電流Ith2を下回ったとき、Pチャネルトランジスタ201をONに遷移させる。閾値設定部130は、入力信号VINに出力信号VOUTを立ち下げる変化があったとき、Pチャネルトランジスタ201のドレイン電流に応じた値に閾値電流Ith1を設定し、閾値設定部140は、入力信号VINに出力信号VOUTを立ち上げる変化があったとき、Nチャネルトランジスタ202のドレイン電流に応じた値に閾値電流Ith2を設定する。

(もっと読む)

1 - 20 / 480

[ Back to top ]