Fターム[5J056CC05]の内容

Fターム[5J056CC05]に分類される特許

1 - 20 / 349

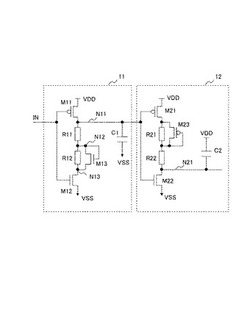

半導体装置

【課題】容量を充放電させ信号を遅延させる回路の遅延時間の温度依存性を緩和し回路規模の増大を抑制可能とした半導体装置の提供。

【解決手段】互いに異なる電源電圧を与える第1の電源(VDD)と第2の電源(VSS)の間に直列に接続され、制御電極が共通に接続された第1及び第2のFET(M11、M12)と、前記第1及び第2のFETの間に接続する第1の回路を有するインバータを備え、前記第1の回路は、互いに並列に接続された第1の抵抗素子(R12)と第3のFET(M13)を備え、前記第1の抵抗素子(R12)の抵抗値は正の温度特性を有し、前記第3のFET(M13)は、その動作範囲に、第3のFET(M13)の端子間抵抗が、第1の抵抗素子(R12)の温度特性と逆極性の負の温度特性を示す領域を含む。

(もっと読む)

半導体装置

【課題】半導体装置の回路ブロックへの電力供給復帰時に、無駄な充放電を削減すること。

【解決手段】半導体装置は、第1電源電圧を供給する第1電源線と、第1電源電圧よりも高い第2電源電圧を供給する第2電源線と、前段回路ブロックと、前段回路ブロックの出力信号に基づいて動作する後段回路ブロックと、前段回路ブロック及び後段回路ブロックに対する第1電源電圧及び第2電源電圧の供給を制御する電力供給制御回路と、を備える。電力供給制御回路は、後段回路ブロックへの第1電源電圧の供給開始タイミングを前段回路ブロックへの第1電源電圧の供給開始タイミングよりも遅延させる。更に、電力供給制御回路は、前段回路ブロック及び後段回路ブロックに第1電源電圧が供給された後に、第2電源電圧を前段回路ブロックと後段回路ブロックの両方に供給する。

(もっと読む)

省面積及び省電力のスタンダードセル方法

【課題】省面積及び省電力のための半導体集積回路の設計方法を提供する。

【解決手段】主回路217と適応電圧用調整回路を含む半導体集積回路であって、適応電圧調整用回路は、クロック信号を受け取るように構成された整合回路211と、整合回路211の出力を受け取り、また、クロック信号を受け取るように構成された位相検出器213と、電源電圧を増加又は減少させるように構成された電圧レギュレータ215とを含み、主回路217は電圧レギュレータ215から電源電圧を受け取るように構成され、整合回路211は電源電圧を受け取って、電源電圧における増加又は減少に基づいて、信号伝搬における遅延を調整するように構成される。

(もっと読む)

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

レベルシフト回路

【課題】占有面積が小さく、温度変化や素子のバラツキの影響を受け難く、さらに、ノイズを低減することで高品位のレベルシフトを実現することができるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、主に、第1の信号(VIN)をレベルシフトして第2の信号(Vm)を出力するレベルシフト部10と、pMOSトランジスタ32aとnMOSトランジスタ32bを含み、第2の信号を反転させた第3の信号(S1)を出力するCMOSインバータ回路部32、偶数個のインバータ素子(第1のインバータ33a〜第mのインバータ33m)を含み、第3の信号を遅延させた第4の信号(S3)を生成する遅延回路部33、論理素子を含み、第3の信号及び第4の信号が入力して第5の信号(S5)を出力する論理回路部34、及び第4の信号と第5の信号が入力するD−FF素子35、を含む出力バッファ部30と、を備える。

(もっと読む)

論理回路、半導体集積回路

【課題】供給される電源電圧の変動を抑制することができる論理回路及び当該論理回路が搭載される半導体集積回路を提供すること。

【解決手段】本発明の一態様であるバッファ回路100は、バッファ部11、電圧検出部12及びスイッチ部13を有する。バッファ部11は、電源端子Ts1又は電圧レギュレータ1と電源端子Ts2との間に接続されることにより電源供給され、入力信号INと同論理の信号を出力端子Toutへ出力する。電圧検出部12は、出力端子Toutの電圧を検出し、検出結果に基づく検出信号Sdetを出力する。スイッチ部13は、検出信号Sdetに応じて、バッファ部11を電源端子Ts1又は電圧レギュレータ1と接続する。

(もっと読む)

半導体装置

【課題】ストローブ信号の変化によって基準電位に重畳するノイズを低減し、これにより、基準電位を用いる入力レシーバ回路の動作マージンの低下を防止する。

【解決手段】ストローブ信号IDQSTによって活性化され、入力信号DQの電位と基準電位VREFとを比較することによって出力信号IDQRを生成する入力レシーバ回路17Rと、ストローブ信号IDQSTの変化によって基準電位VREFに生じるノイズをキャンセルするノイズキャンセラ100Tとを備える。本発明によれば、ノイズキャンセラ100Tによって基準電位VREFに生じるノイズがキャンセルされることから、入力レシーバ回路17Rの動作マージンを十分に確保することができる。これにより、高速なデータ転送を行うことが可能となる。

(もっと読む)

電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法

【課題】電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法を提供する。

【解決手段】本発明の電力制御回路は、電源電圧とロジック回路との間に連結されてロジック回路への電源供給をスイッチングする回路であって、外部から並列的にモード転換信号を受信する複数の第1パワーゲーティングセルと、第1パワーゲーティングセルのうちの何れか1つと連結される少なくとも1つの第2パワーゲーティングセルと、第2パワーゲーティングセルと直列連結される複数の第3パワーゲーティングセルと、直列連結された複数の第3パワーゲーティングセルのうち、先端の第3パワーゲーティングセルと並列連結される複数の第4パワーゲーティングセルとを含み、モード転換信号は、第1パワーゲーティングセルのうちの何れか1つ、第2及び第3パワーゲーティングセルを経て第4パワーゲーティングセルに伝達され、第1ないし第4パワーゲーティングセルのそれぞれは、各自のセルに入力されるモード転換信号に応答して電源供給をスイッチングする。

(もっと読む)

半導体装置

【課題】出力信号の立ち上がり時間および立下り時間が短い半導体装置を提供する。

【解決手段】このクロックドライバは、クロック信号CLKBの反転信号CLKを出力ノードN2に出力するインバータ1と、電源電圧VCCのラインと出力ノードN2との間に直列接続されたトランジスタP2,P3と、出力ノードN2と接地電圧VSSのラインとの間に直列接続されたトランジスタQ2,Q3と、クロック信号CLKを所定時間だけ遅延させてトランジスタP2,Q3のゲートに与える遅延回路3とを含む。たとえば、クロック信号CLKBが「L」レベルから「H」レベルに変化すると、所定時間だけトランジスタQ2,Q3がともにオンして、出力ノードN2から電流を引き抜く。

(もっと読む)

集積回路

【課題】集積回路において電力消費量を容易に低減する。

【解決手段】集積回路は、クロック分配回路、同期動作回路、論理回路、および、電源供給部を備える。クロック分配回路は、所定のタイミングを指示するクロック信号を分配する。同期動作回路は、クロック信号に同期して動作する。論理回路は、同期動作回路の動作結果に基づいて所定の論理演算を実行する。電源供給部は、クロック分配回路を駆動させるクロック分配回路駆動電圧より低い電圧を論理回路に論理回路駆動電圧として供給する。

(もっと読む)

半導体装置

【課題】ハイサイド駆動回路が負バイアス駆動を行いつつ、ブートストラップコンデンサによりハイサイド駆動回路に駆動電圧を供給することができる半導体装置を得る。

【解決手段】基準電圧回路3は、ハイサイド駆動回路1の高圧端子VBの電圧と低圧端子VEの電圧との間の基準電圧を生成して、ハイサイドスイッチング素子Q1とローサイドスイッチング素子Q2の接続点に供給する。充電用スイッチング素子Q3のドレインがハイサイド駆動回路1の低圧端子VEに接続され、ソースが接地されている。

(もっと読む)

補償装置および試験装置

【課題】消費電力を抑制する。

【解決手段】電源装置から印加された電源電圧により動作する対象回路の消費電流を補償する補償装置であって、電源装置から対象回路へと電源電圧を供給するための電源配線に接続され、電源配線に流れる電流を消費する電流消費部と、電流消費部に印加される電源電圧に応じて電流消費部により消費される電流を変化させる電流制御部と、電流消費部の基準電流量を変更する設定部と、を備え、設定部は、対象回路がスタンバイ状態において、基準電流量を低減する補償装置を提供する。

(もっと読む)

ディジタル信号処理回路及び車載用電子機器

【課題】ディジタル信号処理回路及び車載用電子機器において、消費電力を低減し、発熱量を低減する。

【解決手段】車載用電子機器に搭載されるディジタル信号処理回路は、クロック信号に同期して信号取込を行う入力段のフリップフロップ回路と、クロック信号に同期して信号取込を行う出力段のフリップフロップ回路と、順次処理を行う複数の組み合わせ回路が直列に接続されて構成されるとともに、クロック信号に同期して入力段のフリップフロップ回路から処理対象の信号が入力されて前記出力段のフリップフロップ回路に処理後の信号を出力する組み合わせ回路群と、クロック信号に同期して、組み合わせ回路毎に、クロック信号の1周期内において、駆動用電源の供給期間及び非供給期間を設けて駆動用電源の供給を行う電源供給回路と、を備える。

(もっと読む)

半導体集積回路装置

【課題】 差動増幅回路の出力信号の特性を改善する。

【解決手段】入力データ信号が‘Low’レベルになると、トランジスタ16に流れる電流I1の電流が減少し、抵抗14と抵抗14aとの接続部(ノードD)の電位が高くなる。この電位は、トランジスタ18にゲートに入力(負帰還)され、該ゲート電位が高くなることによって、テイル電流量I_TAILが増加する方向に調整される。入力データ信号が‘High’レベルになると、電流I1の電流が多く流れ、ノードDの電位が下がる。これによって、トランジスタ18のゲート電位(負帰還)が下がり、テイル電流量I_TAILを絞る方向に調整される、これによって入力波形の立上りと立下りとで、それぞれ出力波形との遅延時間の差が小さくなる。

(もっと読む)

小振幅差動パルス送信回路

【課題】最適の時期に出力電流を流して、それ以外の時期には出力電流を止めることによって省エネ性能に優れた小振幅差動パルス送信回路を提供すること。

【解決手段】定電流を送信データに応じて差動的に出力する定電流差動出力回路101と、前記定電流差動出力回路101の出力を、送信データの値の変化による該出力の過渡現象が収束した後であって次のデータが出力される前における所定期間通過させるスイッチ回路102と、前記スイッチ回路102の出力を所定電位にバイアスするバイアス回路103とを備える小振幅差動パルス送信回路。

(もっと読む)

電子回路、および実装基板

【課題】出力信号の電圧レベルの遷移の方向に応じて、電源線や接地線を通らず寄生インダクタンス成分の影響を受けない電流を加算して信号の電圧レベルの遷移をアシストすることにより、SSOノイズを抑制することが可能な電子回路および実装基板の制御方法を提供すること。

【解決手段】出力回路1は、出力バッファ4と、出力バッファ4から出力される出力信号が伝搬する出力線と、出力バッファ4に電源を供給する電源線VdeLあるいは接地線VgLの少なくとも何れか一方と、出力線と電源線VdeLあるいは接地線VgLとにより囲まれる磁心50と、磁心50に巻回される制御コイル51と、出力信号の遷移を前もって検出し検出結果に応じて制御コイル51への電流供給を制御するコイル電流制御回路3とを備え、出力信号の遷移方向に応じて、制御コイル51からの電磁誘導により出力線の信号遷移をアシストするアシスト電流を流す。

(もっと読む)

電源電圧設定方法及び電源電圧設定プログラム

【課題】チップごとに適正な電源電圧を設定する。

【解決手段】チップのレイアウトデータ20からクリティカルパスのゲート遅延と配線遅延の遅延比を抽出する(ステップS1,S2)。チップのモニタ回路で実測されたゲート遅延及び配線遅延を、その遅延比に基づき合成して第1遅延値を生成し(ステップS3)、モニタ回路のシミュレーションで得られるゲート遅延及び配線遅延を、その遅延比に基づき合成して第2遅延値を生成する(ステップS4,S5)。このようにゲート遅延、配線遅延、クリティカルパスでの遅延比が考慮された第1遅延値及び第2遅延値に基づいて、チップに適用するチップ電源電圧を設定する(ステップS7)。

(もっと読む)

半導体回路

【課題】本発明は、ハイレベルの入力信号に混入されたローレベルのノイズ及びローレベルの入力信号に混入されたハイレベルのノイズをより効果よく取り除くことができる半導体回路を提供する。

【解決手段】 入力信号を所定時間遅延して出力する遅延部120、220、320と、該入力信号のレベルによって電圧を充放電させる電圧調整部140、240、340と、該入力信号のレベル及び遅延部120、220、320から出力される信号のレベルを用いて生成された信号によって、電圧調整部140、240、340の充放電動作を制御する組合せ部160、260、360とを含む。

(もっと読む)

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

レベルシフト回路

【課題】伝播遅延時間を短縮する。

【解決手段】インバータINV1,INV2と、ラッチ回路1と、反転駆動回路2,3と、セレクタ4を備える。N1=VSS2、N2=VSS2、N3=VSS2、N4=VDD2のとき、入力端子INがVDD1→VSS1に変化したとき、トランジスタMP5をオンして大きな電流をVDD2からノードN1に流し高速にノードN1をVSS1→VDD2に変化させる。その後、トランジスタMP5はオフし、ノードN1はインバータINV4でVDD2に保持される。これで、N1=VDD2、N2=VDD2、N3=VDD2、N4=VSS2となる。次に入力端子INがVSS1→VDD1に変化したとき、トランジスタMN2がオンして大きな電流をノードN1からVSS2に流し高速にノードN1をVDD2→VSS2に変化させる。

(もっと読む)

1 - 20 / 349

[ Back to top ]