Fターム[5J056GG10]の内容

論理回路 (30,215) | 制御対象、制御態様 (2,427) | 出力電圧を制御するもの (1,446) | 段階的に制御するもの (1,382) | あるノードの電流を利用するもの (185)

Fターム[5J056GG10]に分類される特許

1 - 20 / 185

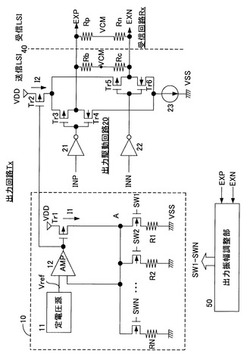

出力回路

【課題】差動出力電圧の振幅のばらつきを抑制した出力回路を提供する。

【解決手段】出力回路は,定電圧ノードと基準電源との間に,複数のスイッチ素子のオン,オフにより合成抵抗値が可変制御可能な複数の抵抗を有し,定電圧ノードに第1の電流を生成する定電流生成回路と,第1の電流をカレントミラーにより生成した第2の電流を,内部回路から供給される内部差動信号に応じて,出力端子対に出力する出力駆動回路と,出力端子対の出力差動電圧の差が所望の電圧差と一致するように,定電流生成回路の複数のスイッチ素子を制御するスイッチ素子制御信号を生成する出力振幅調整部とを有する。

(もっと読む)

スルーレートコントロール装置、スルーレートコントロール方法

【課題】クロック信号の出力バッファにおいて、クロック信号の周波数に応じたスルーレートの調整を行うことによりEMIノイズを抑制することが可能なスルーレートコントロール装置、およびスルーレートコントロール方法を提供すること。

【解決手段】変換ゲインGiに応じて、入力されるVCO入力電圧Viをクロック信号CKoに変換する電圧制御発振器15aを有するPLL回路24aと、VCO入力電圧Viおよび変換ゲインGiの各々に対して正の相関関係を有する制御電流Ibを出力する電圧電流変換器19aと、制御電流Ibに応じてドライブ電流を設定するバッファ制御回路21aと、ドライブ電流で、クロック信号CKoを出力する出力回路22aとを備える。よって、クロック信号CKoの周波数fに比例して出力回路22aのドライブ能力が大きくなる関係を有し、周波数fに応じて好適なスルーレートが決定することができる。

(もっと読む)

差動入力バッファ

【課題】動作モード切り換え時におけるノイズを抑制する。

【解決手段】差動入力バッファ1は、動作モードを通常状態又は省電力状態のいずれかに切り換える電源回路MN1,MN2と、ソースフォロア回路を構成する半導体素子MP1,MP3及びMP2,MP4のそれぞれの寄生容量の合計である第1の寄生容量に対応する第2の寄生容量を有する半導体素子MP7,MP8により構成されるダミー回路とを有し、動作モードの切り換え時に第1の寄生容量に起因して発生する電流の流通方向と、動作モードの切り換え時に第2の寄生容量に起因して発生する電流の流通方向とが共通の配線において相反する構成を有する。

(もっと読む)

出力バッファ回路

【課題】 誘導性負荷を駆動する出力バッファ回路の電力損失を低減する。

【解決手段】 誘導性負荷2から出力バッファ回路100に電流が流入している場合、スルーレート制御部140は、出力バッファ回路100の出力信号VOUTの立ち上がり過程において低いスルーレートから高いスルーレートへ変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において高いスルーレートから低いスルーレートに変化させる制御を行う。また、出力バッファ回路100から誘導性負荷2に電流が流出している場合に、スルーレート制御部140は、出力信号VOUTの立ち上がり過程において高いスルーレートから低いスルーレートに変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において低いスルーレートから高いスルーレートに変化させる制御を行う。

(もっと読む)

バッファ回路

【課題】入力信号の交流成分の歪み等の影響をなるべく受けることなく、本来のデューティー比(目標デューティー比)で出力信号を出力することのできるバッファ回路を提供する。

【解決手段】バッファ回路10は、デューティー比検出部16と直流成分生成部17とから構成される負帰還回路部によって、入力信号増幅部15の入出力間で出力信号SOのデューティー比に応じた直流成分の信号を帰還させている。つまり、バッファ回路10は、出力信号SOのデューティー比に応じて、入力信号SI´の直流成分をさらに小さくしたり、大きくしたりする。これにより、バッファ回路10は、出力信号SOのデューティー比を目的デューティー比に変更した上で、その出力信号SOを出力することができる。

(もっと読む)

半導体装置

【課題】切り替えスイッチのオンオフに伴うノイズがバイアスラインに重畳するのを防ぐ。

【解決手段】バイアス電流が流れるバイアスラインVLと、バイアス電流の量を制御信号DDに基づいて切り替える切り替えスイッチ70と、制御信号DDが供給される制御ラインとバイアスラインVLとの間の寄生容量を介して制御信号DDの変化時に生じるバイアスラインVLの電位変動を相殺する相殺回路91〜93とを備える。本発明によれば、切り替えスイッチ70のオンオフに伴ってバイアスラインVLに生じるノイズを相殺することが可能となる。

(もっと読む)

信号デスキュー方法および装置

【課題】超低圧VDDデジタル回路においては、クロックスキューは厳密な時間収率の劣化を招く大きな原因であるが、コンピュータによる設計の高度な自動化(EDA)手段の様々なプロセスが存在する中でのスキュー調和がとれたクロックツリーを実現する。

【解決手段】参照信号およびローカル信号を受信し、それらを比較して位相差を検出するための位相比較器、位相差の値に関連して制御信号のオン/オフを切り替えるための制御回路、およびローカル信号バッファーを有し、前記ローカル信号バッファーはnMOSトランジスタおよび/またはpMOSトランジスタを有しており、前記制御信号に応じてホットキャリアインジェクションストレスをnMOSトランジスタまたはpMOSトランジスタに掛けてnMOSトランジスタまたはpMOSトランジスタのしきい値電圧を増加させる。

(もっと読む)

出力回路、温度スイッチIC、及び、電池パック

【課題】電源電圧が動作電圧以下でも出力が不定にならず、かつ面積の小さい出力回路を提供する。

【解決手段】インバータ回路の電源端子にスイッチ回路を設け、電源電圧が回路の動作電圧以下のとき、スイッチ回路がインバータ回路の動作を停止させる。そして、インバータ回路の出力端子に電流源を設け、インバータ回路の動作が停止したときに出力を電源電圧に固定する、ように構成した。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

半導体出力回路

【課題】入力信号に対して出力信号が高速に応答し、かつ、半導体出力回路の消費電力を低減させることが可能である半導体出力回路を提供する。

【解決手段】本発明の半導体出力回路は、ベースが定電流源に接続され、コレクタが第2のnpnトランジスタのエミッタに接続され、エミッタが第1のnpnトランジスタのコレクタに接続される第3のnpnトランジスタを含む。

(もっと読む)

レベルシフト回路並びにレベルシフト回路を備えたインバータ装置

【課題】VM電位のdv/dtに起因する上アーム電力用スイッチング素子の誤動作を抑制できるレベルシフト回路並びにこれを備えたインバータ装置を提供する。

【解決手段】支持体Si基板上にBOX酸化膜を介しN型Si活性層を形成したSOI基板により構成し、分離酸化膜により分離されN型MOSFETを形成する第1のN型Si活性層、分離酸化膜により分離されP型拡散層による拡散抵抗を形成する第2のN型Si活性層、分離酸化膜により分離され上アーム制御電源の一端側に接続する第4のN型Si活性層から構成され、第1のN型Si活性層を形成する分離酸化膜と第4のN型Si活性層を形成する分離酸化膜は、隣接配置されるとともに、N型MOSFETのドレイン電極と拡散抵抗の第一の電極を接続し、拡散抵抗の第2の電極を上アーム制御電源の他端側に接続した。

(もっと読む)

電気信号の伝送回路、IC、プリント配線板、機器およびシステム

【課題】CMOS伝送回路において、レシーバの動作を不安定にしたり不要輻射を放出したりするリンギングの発生を抑制した電気信号の伝送回路を提供する。

【解決手段】本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、CMOSドライバのPMOS FET1と並列にアノード電極がドライバ出力端子につながれるように第1のダイオード6を接続し、CMOSドライバのNMOS FET2と並列にカソード電極がドライバ出力端子につながれるように第2のダイオード7を接続し、PMOS FET1のデバイストランスコンダクタンスと第1のダイオード6の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにし、NMOS FET2のデバイストランスコンダクタンスと第2のダイオード7の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路である。

(もっと読む)

電圧発生装置

【課題】低電源電圧状態で、ビットラインプリチャージ電圧又はセルプレート電圧を安定的に駆動し、待機電流IDD2P及び動作電流を最小化すること。

【解決手段】電源電圧のハーフレベルの基準電圧を利用し、異なるレベルのバイアス信号を生成するバイアス信号生成手段と、出力端の電圧レベルに応答してプルダウン駆動信号を生成する駆動信号生成手段と、駆動信号に応答して出力端を駆動する電圧駆動手段と、出力端の電圧レベルに応じてプルアップ駆動信号/プルダウン駆動信号を生成する駆動信号生成手段と、前記プルアップ駆動信号/プルダウン駆動信号に応答して前記出力端をプルアップ駆動/プルダウン駆動するプルアップPMOSトランジスタ/プルダウンNMOSトランジスタと、第1多重化手段と、第2多重化手段とを備える半導体メモリ素子の電圧発生装置。

(もっと読む)

差動出力回路

【課題】ゲート電圧に対する遅延調整を行わずに、クロスポイントの変動を抑えること。

【解決手段】駆動部100と出力部101は、カレントミラー構成により、プロセス、電圧、温度条件が変動しても共に同一の変動となるため、入力信号INTの信号レベルが“H”から“L”に切り替わる際、MOSFET3、6がオンしているときに、MOSFET5、4がオフ状態からオン状態に速く切り替わることはない。従って、クロスポイントの変動を抑えることができる。また、この構成により、ゲート電圧PL、PR、NL、NRは、電源電圧VSSからVDDまでフルスイングされないため、MOSFET3、6をオンさせ、MOSFET5、4をオフさせる場合、ゲート電圧PLの立ち下がりに対してゲート電圧NLの立ち下がりに遅延をもたせたり、ゲート電圧NRの立ち上がりに対してゲート電圧PRの立ち上がりに遅延をもたせたりする必要がない。

(もっと読む)

レベルシフト回路及びその方法

【課題】レベルシフト回路及びその方法の提供。

【解決手段】本発明のレベルシフト回路及びその方法は、レベルシフト回路のラッチ装置と電圧源の間に限流回路を接続して、前記ラッチ装置の駆動電流が設定値を超えないように制限する。これにより、レベルシフト回路を変換する時の消耗電流を減らし、通路の短いトランジスタを使用したラッチ装置を実現し、レベルシフト回路面積を縮小する。前記設定値は調節可能とし、レベルシフト回路の出力駆動能力を調整することにより、前記レベルシフト回路の変換速度を加速させることができる。

(もっと読む)

磁気レベルシフタ

【課題】多チャンネル化しても形成面積の増大を抑えることができる磁気レベルシフタを提供する。

【解決手段】レベルシフタは、入力信号が印加される磁界発生用配線112と、磁界発生用配線112が発生した磁界に対応した値をとる検出信号を出力する検出用磁気抵抗効果素子11と、一定の値をとる参照信号を出力する参照用磁気抵抗効果素子21,31を備える。当該レベルシフタは、検出信号と参照電圧の差に基づいて出力信号を生成する。

(もっと読む)

電圧レベルシフト回路および半導体装置

【課題】電圧レベルシフト回路において、入力信号の信号レベルによる応答特性の差違を抑制する。

【解決手段】電圧レベルシフト回路は、入力信号とは異なる電圧振幅を有する出力信号VOUTを生成する。インバータINV2は、入力信号にしたがってVSS〜VDDIの範囲の電圧V1を生成する。インバータINV3は、入力信号にしたがってVSS〜VPERIの範囲の電圧V2を生成する。インバータINV4は、V1およびV2にしたがって出力信号VOUTを生成する。

(もっと読む)

半導体装置

【課題】外部電圧が変動したときにも半導体装置の動作安定性を維持する。

【解決手段】入力信号判定部116は、第1電流源122から供給される電源電位によって動作する。入力信号判定部116は、入力信号VINと参照電位Vrefを比較する。比較結果はインバータINV1により反転され、出力信号V0となる。電源センサ回路120は、第1の電源ラインVDDIの電位を監視する。外部電位VDDIが基準電位VXよりも低くなると、電源センサ回路120は第2電流源124をオンする。第2電流源124がオンされると、判定部126には、第1電流源122に加えて第2電流源124からも動作電流が供給される。

(もっと読む)

差動増幅回路及びそれを用いたレベル変換回路

【課題】従来の差動増幅器は出力ノードから出力される差動信号の振幅レベルが十分確保できない可能性があった。

【解決手段】第1の電源端子と第1、第2のノード間にそれぞれ接続され、入力差動信号に導通状態が制御される第1、第2の能動負荷回路と、前記第1、第2のノードと第1、第2の出力ノード間にそれぞれ接続される第3、第4の能動負荷回路と、前記第1、第2の出力ノードと第2の電源端子との間にそれぞれ接続され、前記第2、第1のノードの電位に応じて導通状態が制御される第5、第6の能動負荷回路とを有し、前記第3、第4の能動負荷回路が前記入力差動信号に応じて導通状態が制御される第1の構成、前記第5、第6の能動負荷回路がそれぞれ前記第1、第2の出力ノードの電位に応じても導通状態が制御される第2の構成の少なくともどちらか一方の構成を有する差動増幅回路。

(もっと読む)

高速送信器ドライバ回路のための構成可能なエンファシス

【課題】シリアルデータ信号において、シリアルデータ信号内の直前のビットのデータ値とは異なる各ビットにプレエンファシスを与える回路を提供すること。

【解決手段】シリアルデータ信号において、該シリアルデータ信号内の直前のビットのデータ値とは異なる各ビットにプレエンファシスを与える回路であって、該回路は、各次のビットのデータ値を示す方向に回路要素内に第1の電流を流す第1の回路と、1つのビットが、該1つのビットの直前にあるビットと同一のデータ値を有する条件に応答して、該第1の電流とは反対の方向に該回路要素内において流れるように第2の電流を流す第2の回路と、該回路要素における正味の電流の量および方向に基づいて、シリアルデータ出力信号を生成する第3の回路とを備える、回路。

(もっと読む)

1 - 20 / 185

[ Back to top ]