Fターム[5J067AA64]の内容

Fターム[5J067AA64]に分類される特許

1 - 20 / 24

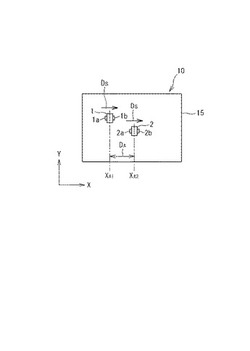

ドハティ増幅装置及び通信装置

【課題】ドハティ増幅装置の効率低下を防止する。

【解決手段】ドハティ増幅装置は、メインアンプを構成するメインアンプデバイス1と、ピークアンプを構成するピークアンプデバイス2と、メインアンプデバイス1及びピークアンプ2が実装された基板15とを有している。メインアンプデバイス1は、第1デバイス本体1c、第1入力端子1a、及び、第1出力端子1bを備え、第1入力端子1a及び第1出力端子1bが第1デバイス本体1cを挟んで対向して配置されている。ピークアンプデバイス2は、第2デバイス本体2c、第2入力端子2a、及び、第2出力端子2bを備え、第2入力端子2a及び第2出力端子2bが第2デバイス本体2cを挟んで対向して配置されている。ピークアンプデバイス2は、メインアンプデバイス1の位置に対して、メインアンプデバイス1の第1入力端子から第1出力端子に向かう入出力方向Dsにずれた位置に、実装されている。

(もっと読む)

交流電力増幅器

【課題】LINC方式の増幅器において入力振幅の広い範囲に亘って高い効率を得ることができる交流電力増幅器を提供する。

【解決手段】入力端子1から入力された入力信号を2つの定振幅の交流信号に分離して、それらの交流信号の位相差が入力信号の振幅に対応して変化するようにした分波回路90と、飽和領域で動作するFET12、22を有し、2つの定振幅の交流信号をそれぞれ増幅する2つの飽和増幅器10、20と、を備え、それぞれの飽和増幅器からの増幅された増幅信号を合成点で合成して、出力端子2から出力しており、各FET12、22のドレインと合成点39との間が、増幅すべき交流信号の基本波に対して略四分の一波長に相当する遅延を与える伝送線路32、33で結合されており、且つ合成点39には、高調波を反射し且つ合成点39で負荷側を見た高調波の反射位相を逆相とするキャパタ34が設けられる。

(もっと読む)

増幅装置

【課題】ピーク信号の電力および位相を最適化できるようにして、ドハティ増幅装置の生産性、リニアリティおよび効率を改善する。

【解決手段】ドハティ増幅装置を改良した増幅装置2においては、減衰器242および移相器244によるピーク信号の位相および電力の最適に調整される。この最適化の結果、キャリア増幅部22およびピーク増幅部24において生じるキャリア信号と、ピーク信号との位相差が解消されるので、高効率で、しかも、リニアリティよく、無線信号を増幅できるようになる。

(もっと読む)

高周波電力増幅器および電力増幅方法

【課題】回路を複雑にすることなく高効率な高周波電力増幅器および電力増幅方法を提供する。

【解決手段】メインアンプ1および所定の出力以上になると動作するピークアンプ2とによりドハティ型増幅器と呼ばれる回路を構成し、入力信号の一方は、メインアンプ1へ、他方はλ/4線路3を介してピークアンプ1へ入力される。メインアンプ1の出力は、λ/4線路4を介して出力され、そのλ/4線路4の出力は更にλ/4線路5へ入力される。

ピークアンプ2の出力も同様にλ/4線路5へ入力され、バンドパスフィルタ6は、このピークアンプの出力を入力し入力信号の2倍波の信号を抽出して更に補償部7へ出力する。補償部7は振幅および位相を整えた信号を両アンプ1、2の入力へフィードバックする。

(もっと読む)

増幅器

【課題】 キャリア増幅器が飽和する前にピーク増幅器に流れる電流を低減して、増幅器全体としての効率を向上させることができる増幅器を提供する。

【解決手段】 AB級又はB級で動作する増幅素子を備えたキャリア増幅回路4と、B級又はC級で動作する増幅素子を有し、入力レベルに応じて段階的に動作を開始する複数のピーク増幅回路5-1〜5-nとを備え、キャリア増幅回路4とピーク増幅回路5-1〜5-nの出力を合成して出力し、ピーク増幅回路5-1〜5-nの内、最も低い入力レベルで動作を開始するピーク増幅回路の飽和出力がキャリア増幅回路4の飽和出力より小さい増幅器としている。

(もっと読む)

増幅器

【課題】

ドハティ(doherty)増幅器において、高価な増幅素子のみを用いることなく、増幅効率を維持したまま、より経済的に有利な増幅器を構成する。

【解決手段】

ドハティ増幅器において、キャリア増幅器に用いる増幅素子としてピーク増幅器に用いる増幅素子よりも効率特性の良好な増幅素子を用い、ピーク増幅器に用いる増幅素子として効率特性がキャリア増幅器で用いられる増幅素子より劣る増幅素子を用いる。

【効果】

効率特性の異なる増幅素子を用いることで、増幅効率を劣化させずに経済的に有利にドハティ増幅器を構成することができる。

(もっと読む)

電力合成形増幅器

【課題】広帯域かつ高効率で、容易に実現可能な電力合成形増幅器を提供する。

【解決手段】所定の入力信号が分配される2つの経路の一方に設けられて入力信号を増幅するB級動作トランジスタ3と、他方の経路に設けられて入力信号を増幅するC級動作トランジスタ4と、B級動作トランジスタ3の出力電力とC級動作トランジスタ4の出力電力とを合成するT分岐11とを有する電力合成形増幅器である。B級動作トランジスタ3の出力電力は、第1アイソレータ9を介してT分岐11に送られ、C級動作トランジスタ4の出力電力は、第2アイソレータ10を介してT分岐11に送られる。第1アイソレータ9によりB級動作トランジスタ3の負荷インピーダンスを一定値にし、第2アイソレータ10がC級動作トランジスタ4の負荷インピーダンスを一定値にする。

(もっと読む)

ドハティ増幅回路

【課題】 従来のドハティ増幅回路では、AM−PM特性(振幅−位相特性)の変動が複雑であって、十分な歪補償を行うのが困難であるという問題点があり、本発明は、AM−PM特性を改善し、歪の小さいドハティ増幅回路を提供する。

【解決手段】 互いにAM−PM特性の異なる複数のドハティ増幅部を縦続接続したものであって、例えば、AM−PM特性が逆特性となるGaAsFETを用いた成るドハティ増幅部20と、LD−MOSFETを用いたドハティ増幅部30とを縦続接続したものであり、それぞれのドハティ増幅部で発生する位相変化を相殺して、全体として良好なAM−PM特性を実現し、歪を低減するドハティ増幅回路である。

(もっと読む)

ドハティ増幅器

【課題】変化する入力電力やピーク/平均電力比に対して最適なバイアスを印加するドハティ増幅器を提供する。

【解決手段】アクティブ・バイアス回路では、平均電力検出手段22が入力信号の平均電力を示す電圧値を検出し、包絡線検出手段26が入力信号の包絡線を検出し、しきい値演算手段24が平均電力電圧値に応じて包絡線のしきい値を演算し、電圧制限手段32が包絡線を一定値以下に制限し、これにより、入力信号の平均電力に応じたバイアス電圧を印加する。また、ピークホールド手段27が包絡線の最大電圧値を保持し、差演算手段28が包絡線最大電圧値と平均電力電圧値との差を演算し、電圧制御増幅器30が演算された電圧値を制御電圧として増幅率を変化させて包絡線を増幅し、これにより、入力信号のピーク/平均電力比に応じたバイアス電圧を印加する。

(もっと読む)

増幅器

【課題】 高効率ドハティ増幅器の入力分配器の分配損によるゲイン低下を防止して高ゲインを図り、高次歪の増加を抑えて高次歪を低減できる増幅器を提供する。

【解決手段】 AB級で動作するキャリア増幅回路4とB級又はC級で動作するピーク増幅回路5からの出力をノード62で合成出力するものであって、分配器2で分配された信号に対して伝送線路33で線路の長さが調整されて低入力時の反射係数を変更し、キャリア増幅回路4からの信号をインピーダンス変換器64でインピーダンス変換し、ピーク増幅回路5からの信号について伝送線路65で損失がないよう低入力時のインピーダンスを大きくみせ、低入力時に、分配器2からピーク増幅回路5側の入力インピーダンスを無限大に近づけることで、低入力時の利得を上げる増幅器である。

(もっと読む)

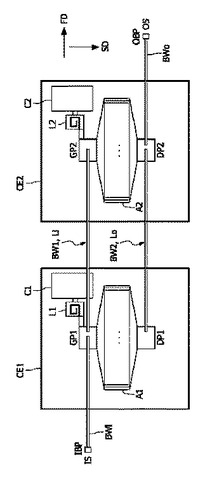

高出力集積RF増幅器

入力ボンド・パッド(IBP)と第1の方向(FD)に互いに変位された複数のセル(CE1、CE2)と出力ボンド・パッド(OBP)とをこの順序で第1の方向(FD)に備えた集積HF増幅器構造体。セル(CE1、CE2)の各々は入力パッド(GP1、GP2)とアクティブ領域(A1、A2)と出力パッド(DP1、DP2)とを有する増幅器を備える。アクティブ領域(A1、A2)は、入力パッド(GP1、GP2)と出力パッド(DP1、DP2)の間に配置され、入力パッド(GP1、GP2)とアクティブ領域(A1、A2)と出力パッド(DP1、DP2)は第1の方向(FD)に対してほぼ直角な第2の方向(SD)に互いに変位される。第1の回路網(N1)は、複数のセル(CE1、CE2)のうちの隣接するセルの入力パッド(GP1、GP2)を相互接続するための第1の相互接続手段(Li、Ci;Li1、Li2、Ci1)を備え、且つ第1の方向(FD)に延びる。第2の回路網(N2)は、複数のセル(CE1、CE2)のうちの隣接するセルの出力パッド(DP1、DP2)を相互接続するための第2の相互接続手段(Lo、Co;Lo1、Lo2、Co1)を備え、且つ第1の方向(FD)に延びる。第1の回路網(N1)及び第2の回路網(N2)は、すべての相互接続されたセル(CE1、CE2)について、出力ボンド・パッド(OBP)にて、入力ボンド・パッド(IBP)での同じ入力信号(IS)に対して等しい位相シフト及び振幅を有する出力信号(OS)を得るように構成される。特定のバイアス及び位相シフト条件において、構造体は出力バックオフでの効率が改善されたドハティ増幅器を実現する。  (もっと読む)

(もっと読む)

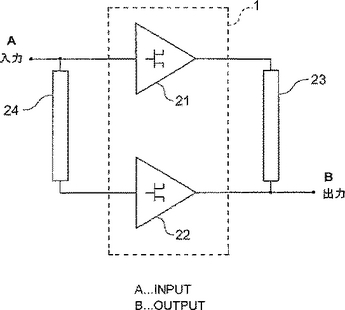

LINC技術と組み合わされた出力ネットワーク

本発明は、Chireixのようなアウトフェージング技術と組み合わされた平衡型電力増幅器のネットワークに関する。本発明の目的はカレントモードクラスD(CMCD)又はクラスE/Fのような平衡型増幅器をLINCネットワークと組み合わせるための解決方法を提供することである。主な問題点として、いくつかの電力増幅器が平衡出力を有し、そして、LINCネットワークがシングルエンデッド型であるという点が挙げられる。その結果、さまざまなインピーダンスレベルで作動する高出力低損失変圧器を必要とすることになるが、セルラ周波数でこの変圧器を実現することは困難である。  (もっと読む)

(もっと読む)

ドハティ型増幅器

【課題】単品ごとの特性のばらつきを抑え、外部擾乱への耐性を高めたドハティ型増幅器を提供すること。

【解決手段】メインアンプ2の出力を一部分岐した信号を入力信号と逆相で加算した信号をピーキングアンプ3に入力するようにしているので、ピーキングアンプ3のバイアス調整が不要となる。つまりメインアンプ2の出力と入力信号との関係に応じた信号がピーキングアンプ3に入力されるので、メインアンプ2が飽和して利得が低下した分の電力だけ、ピーキングアンプ3から電力が供給されるようになる。従ってピーキングアンプ3のドレイン電流の立ち上がり特性を改善することができ、線形性をより高められるとともに部品ごとの特性のばらつきを抑え、外部擾乱にも高い耐性を持つドハティ型増幅器を提供することが可能になる。

(もっと読む)

増幅器

【課題】 例えば、従来のドハチィ増幅器を超えた性能を有する増幅器を提供する。

【解決手段】 信号を増幅する増幅器において、信号を分配する分配手段1と、分配された第1の信号をAB級で増幅するキャリア増幅回路2と、分配された第2の信号をB級又はC級で増幅するドライブ増幅回路5と、ドライブ増幅回路により増幅された信号をB級又はC級で増幅するピーク増幅回路6と、キャリア増幅回路の出力に接続される第1のインピーダンス変換器8と、ピーク増幅回路の出力に接続される第2のインピーダンス変換器7と、第1のインピーダンス変換器の出力と第2のインピーダンス変換器の出力を合成する合成端9と、を備えた。

(もっと読む)

増幅器

【課題】歪を更に改善し、周囲環境温度の変化時にも性能の変動が少ない高効率の増幅器を提供する。

【解決手段】本発明の増幅器は、入力信号を分配器で分配して複数の増幅回路に入力し、複数の増幅回路の出力を合成して出力とする増幅器であって、複数の増幅回路は、増幅素子をAB級で動作させる少なくとも一つの第1の増幅回路と、増幅素子をB級またはC級で動作させる少なくとも一つの第2の増幅回路とにより構成され、分配器の配分比を異ならせ、第1及び第2の増幅回路の出力をそれぞれ任意の長さの電気長を有する伝送線路からなるインピーダンス変換器を介して接続して合成としたものである。

(もっと読む)

増幅装置

【課題】増幅装置で、適切な整合を取ることにより性能を改善する。

【解決手段】信号を増幅する増幅装置で、信号を分配する分配手段1と、分配された第1の信号をAB級で増幅するキャリア増幅器2と、分配された第2の信号をB級又はC級で増幅するピーク増幅器4と、キャリア増幅器の出力に接続される任意の電気長を有する第1の伝送線路と、ピーク増幅器の出力に接続される任意の電気長を有する第2の伝送線路と、第1の伝送線路の出力と第2の伝送線路の出力を合成する合成端18を備え、合成端のインピーダンスは、第1の伝送線路及び第2の伝送線路により夫々変換されたキャリア増幅器及びピーク増幅器の最大出力時の負荷インピーダンスの並列インピーダンスとは異ならせ、あるいはキャリア増幅器及びピーク増幅器の最大出力時の負荷インピーダンスを変えた並列インピーダンスとして、設定された。

(もっと読む)

増幅器

【課題】従来のドハティ増幅器を超えた高電力効率および低出力歪である増幅器を提供する。

【解決手段】本発明に係る増幅器は、複数の増幅回路の出力を合成して出力とする増幅器において、複数の増幅回路のうち、増幅素子をAB級で動作させる第1の増幅回路と、複数の増幅回路のうち、増幅素子をB級またはC級で動作させる第2の増幅回路と、第1の増幅回路の出力に接続されるλ/4以外の電気長を有する第1の伝送線路と、第2の増幅回路の出力に接続される任意の電気長を有する第2の伝送線路と、第1の伝送線路の出力と第2の伝送線路の出力とを合成する合成端と、を備える。更に、第1の伝送線路若しくは第2の伝送線路の少なくとも一方が、位相器を有する。更に、第1の増幅回路は、AB級で動作する第1のプリアンプを有し、第2の増幅回路は、A級からC級のいずれかを動作点とする第2のプリアンプを有する。

(もっと読む)

高周波電力増幅装置

【課題】ドハティ機能を機構的にサイズが大きくなる伝送線路を用いずに実現することができ、ドハティ機能を備える増幅装置のサイズをさらに小型化して、機構的に容積の縮小化が要求される移動体通信機器にもドハティ機能を実装することができる高周波電力増幅装置を提供する。

【解決手段】キャリア増幅器102とピーク増幅器103をそれぞれトランジスタによる多段構成として、各増幅器102、103が90度の位相差で動作するように設計することにより、ドハティ機能を実現する場合に従来ピーク増幅器の入力側に用いていた1/4波長ネットワークを不要とする。

(もっと読む)

増幅器

常に信号の増幅動作を行うキャリア増幅器と、高電力出力時のみに動作するピーク増幅器と、キャリア増幅器とピーク増幅器の出力を合成して出力する合成器と、入力信号をキャリア増幅器側とピーク増幅器側に分配する分配器とを含んで構成される。キャリア増幅器およびピーク増幅器は1個のパッケージ1(1パッケージトランジスタ)に内蔵される。  (もっと読む)

(もっと読む)

増幅器

【課題】AM−PM歪みを効果的に抑制することができ、小型で低コストの増幅器を提供する。

【解決手段】ドハーティ増幅器において、入力分配回路2の前段に前置歪み補償回路7が、また、ピーク増幅器4の前段に、置歪み補償回路9が夫々設けられている。入力端子1からの入力信号は、入力分配回路2により、キャリア増幅器3とピーク増幅器4とに分配され、キャリア増幅器3が飽和するまでは、キャリア増幅器3のみで増幅され、キャリア増幅器3が飽和すると、入力信号のキャリア増幅器3が飽和するレベル以上のピーク部分がピーク増幅器4で増幅されるが、キャリア増幅器3で生ずるAM−PM歪みは前置歪み補償回路7で補償され、ピーク増幅器4で生ずるAM−PM歪みは前置歪み補償回路7と前置歪み補償回路9とで補償される。

(もっと読む)

1 - 20 / 24

[ Back to top ]