Fターム[5J079AA04]の内容

電気機械共振器を用いた発振回路 (23,106) | 周波数決定素子 (2,461) | 電気機械振動子 (2,458) | 圧電振動子 (2,040) | 水晶 (1,806)

Fターム[5J079AA04]に分類される特許

1,721 - 1,740 / 1,806

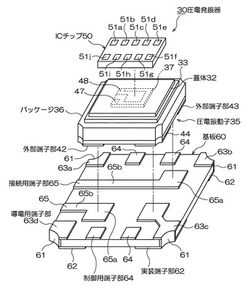

圧電発振器、及びその製造方法

【課題】 小型化に対応するとともに、汎用性のある圧電振動子を利用して、製造コストを抑えた圧電発振器を提供すること。

【解決手段】 実装端子部を除き、少なくとも導通可能な部分が樹脂で封止されるようになっており、実装端子部62を底面に有する基板60と、この基板の上面に固定され、蓋体で封止されたパッケージ36内に圧電振動片37を収容し、この圧電振動片と電気的に接続された外部端子部42,43をパッケージの表面に有する圧電振動子35と、パッケージ36の基板60に実装する面と反対の面に固定され、発振回路を構成するための発振回路素子と50を備え、基板60は、その上面に、実装端子部62と電気的に接続された導電用端子部63a〜63dを有し、外部端子部42,43および導電用端子部63a〜63dが、発振回路素子50と電気的に接続されている。

(もっと読む)

水晶発振装置

【課題】 従来の発振器では経時変化により劣化して周波数が変化した場合に、定期的に計測しなおしてゼロ調整しなくてはならなかった。そのため計測の設備を用意し、計測しながら周波数調整を行っていた。

【解決手段】 本発明では、二つの発振器のうち第二発振器は水晶振動子の水晶電流を多く流して短期安定度のよい発振器とし、これを基準として水晶電流を少なくして長期安定度の特性の良い第一発振器に位相同期させて、安定な周波数を得られる発振装置としている。

(もっと読む)

圧電発振器

【課題】

本発明の目的は、取り扱いが簡便で、生産性に優れた圧電発振器を提供することである。

【解決手段】

本発明は、下面にキャビティ部を有する矩形状の容器体と、前記の容器体の上面側に実装された水晶振動素子と、前記キャビティ部内に、前記水晶振動素子の発振周波数に対応した発振信号を温度補償データに基づいて補正しつつ出力する集積回路素子を取り付けて成る圧電発振器であって、前記キャビティ部の内壁部分に特性制御データ書込端子、または/及び水晶振動素子のモニター端子を設けることにより課題を解決するものである。

(もっと読む)

圧電振動子収納用パッケージおよび圧電装置

【課題】 小型化が可能であり、微妙な発振周波数の調整が可能であり、かつ圧電振動子の発振周波数特性等の特性に優れるとともに外部の電気回路等に対する電気的接続の信頼性に優れた圧電振動子収納用パッケージおよび圧電装置を提供すること。

【解決手段】 圧電振動子収納用パッケージは、上面に第一の凹部5が形成されるとともに下面に第二の凹部12が形成された絶縁基体1と、絶縁基体1の上面の第一の凹部5の周囲に全周にわたって形成された枠部10と、枠部の内側から絶縁基体1の外表面にかけて形成された配線導体6と、絶縁基体1の上面に第一の凹部5を塞ぐように取着される蓋体7とを具備しており、第一の凹部5に圧電振動子2,3および第一の電子部品4が収容され、蓋体7の上面に半導体素子8が搭載され、第二の凹部12に圧電振動子2,3の周波数を調整するための第二の電子部品11が収容されている。

(もっと読む)

圧電発振器及びその製造方法

【課題】従来の圧電発振器おいては、基板の下側主面及び基体により形成される空間の容量には、集積回路素子のほかチップ型電子素子を搭載するための空間容量(特に基体で囲われた基板の下面主面の面積)が必要であり、圧電発振器の小型化に対し大きな障害の一つとなっていた。

【解決手段】基板の他方の主面上辺縁部に切欠部、及びこの切欠部の底面にはチップ型電子素子と電気的に接続固着する2つの電子素子接続用電極パッドが設けた基体が形成され、切欠部に少なくとも1つのチップ型電子素子が、基体の底面の少なくとも1つの角部に該チップ型電子素子の接地する電極が来るような位置に配置されており、且つチップ型電子素子が配置されていない基体の残りの角部底面には該集積回路素子と電気的に接続した外部接続用電極端子が形成されている圧電発振器およびその製造方法であること。

(もっと読む)

圧電振動子収納用パッケージおよび圧電装置

【課題】 圧電振動子を半導体素子等の他の電子部品とともに収容しても小型化が可能であり、かつ圧電振動子の発振周波数特性等の特性に優れるとともに、外部の電気回路等に対する電気的な接続の信頼性に優れた圧電振動子収納用パッケージおよび圧電装置を提供すること。

【解決手段】 上面に3つの凹部が形成された絶縁基体1と、絶縁基体1の上面の3つの凹部5の周囲に全周にわたって形成された枠部10と、枠部10の内側から絶縁基体1の外表面にかけて形成された配線導体6と、絶縁基体1の上面に3つの凹部5を塞ぐように取着される蓋体7とを具備しており、3つの凹部5のうちの2つにそれぞれ圧電振動子2,3が収容されるとともに他の1つに電子部品4が収容され、蓋体7の上面に半導体素子8が搭載されている。および電子部品4が収容され、蓋体7の上面に半導体素子8が搭載されている。

(もっと読む)

PLL回路、テレビジョン受信機、及びテレビジョン受信機のビート改善方法

【課題】 チャネル毎に基準発振周波数の必要変化量が異なる場合に、複数のチャネルでビート回避し得るPLL回路、テレビジョン受信機、及びテレビジョン受信機のビート改善方法を提供する。

【解決手段】 局部発振成分として基準となる周波数の信号を発振すべく、発振子32、容量及び発振子32の直列回路にて構成される基準信号発振回路40を備える。容量は、妨害症状を有するチャネルに対して局部発振成分における基準となる周波数を可変すべく、バリキャップダイオード(VDi)42・バリキャップダイオード(VDi)用バイアス抵抗43にて構成される可変容量からなっている。

(もっと読む)

逓倍型の水晶発振器

【目的】小型を促進してn次高調波成分よりも低い雑音成分を抑圧した逓倍型発振器を提供する。

【構成】アース電位に接地した並列共振回路及び増幅回路を有する逓倍回路を発振回路に接続し、前記発振回路のn次高調波成分(但し、nは2以上の整数)を出力とする逓倍型の水晶発振器において、前記並列共振回路は、前記n次高調波成分よりも低い共振周波数とするインダクタとコンデンサの直列共振回路と、前記直列共振回路に並列接続したリアクタンス素子とから逓倍型の水晶発振器を構成する。

(もっと読む)

高周波モジュール

【課題】 高周波モジュールの小型化を促進し、且つ、コストの低減を図る。

【解決手段】 高周波モジュール1の回路基板2の側面に水晶振動子6を装着して該回路基板2の縮小を図り、斯くして高周波モジュールを小型化する。

(もっと読む)

圧電振動子収納用パッケージおよび圧電装置

【課題】 圧電振動子を半導体素子等の他の電子部品とともに収容しても小型化が可能であり、かつ圧電振動子の発振周波数特性等の特性に優れるとともに、外部の電気回路等に対する電気的な接続の信頼性に優れた圧電振動子収納用パッケージおよび圧電装置を提供すること。

【解決手段】 上面に複数の凹部5が形成された絶縁基体1と、絶縁基体1の上面の複数の凹部5の周囲に全周にわたって形成された枠部10と、枠部10の内側から絶縁基体1の外表面にかけて形成された配線導体6と、絶縁基体1の上面に複数の凹部5を塞ぐように取着される蓋体7とを具備しており、複数の凹部5のうちの1つに圧電振動子2,3が収容されるとともに他の一つに電子部品4が収容され、蓋体7の上面に半導体素子8が搭載されている。

(もっと読む)

圧電発振器及びその製造方法

【課題】従来の圧電発振器おいては、基板の下側主面及び基体により形成される空間の容量には、集積回路素子のほかチップ型電子素子を搭載するための空間容量(特に基体で囲われた基板の下面主面の面積)が必要であり、圧電発振器の小型化に対し大きな障害の一つとなっていた。

【解決手段】この基板の他方主面の4つの角部の内少なくとも一つの角部に、一端の電極端子を集積回路素子の非接地端子に電気的接続し、他端の電極端子を集積回路素子の接地端子に電気的接続し、且つ他端の電極端子が該角頂部に配置するようにチップ型電子素子が搭載され、基板の他方の主面の残り3つの角部には底面に外部接続用電極端子が形成された金属柱が形成されていることを特徴とする圧電発振器およびその製造方法であること。

(もっと読む)

圧電振動子収納用パッケージおよび圧電装置

【課題】 圧電振動子を半導体素子等の他の電子部品とともに収容しても小型化が可能であり、かつ圧電振動子の発振周波数特性等の特性に優れるとともに、外部の電気回路等に対する電気的な接続の信頼性に優れた圧電振動子収納用パッケージおよび圧電装置を提供すること。

【解決手段】 上面に凹部5が形成された絶縁基体1と、絶縁基体1の上面の凹部5の周囲に全周にわたって形成された枠部10と、枠部10の内側から絶縁基体1の外表面にかけて形成された配線導体6と、絶縁基体1の上面に凹部5を塞ぐように取着される蓋体7とを具備しており、凹部5に圧電振動子2,3および電子部品4が収容され、蓋体7の上面に半導体素子8が搭載されている。

(もっと読む)

接合型とした表面実装用の水晶発振器

【目的】セット基板に搭載後での発振周波数の変化を防止した表面実装発振器を提供する。

【構成】 本発明は、特許請求の範囲に示したように、請求項1では、水晶片を密閉封入して底面の4角部に振動子用端子を有する水晶振動子と、ICチップを収容して枠壁の上面に前記振動子用端子と接続する接合端子を有する凹状の実装基板とを備え、前記水晶振動子の底面に前記実装基板の開口面側を接続してなる表面実装用の水晶発振器において、前記実装基板の前記接合端子の間となる前記枠壁に切り欠きを設けて、保護樹脂の流入を防止する樹脂を注入した構成とする。又は、前記水晶振動子の前記振動子用端子間に保護樹脂の流入を防止する絶縁膜を設けた構成とする。

(もっと読む)

圧電振動子収納用パッケージおよび圧電装置

【課題】 半導体素子と水晶振動子とを同時に搭載した圧電装置としても、圧電振動子の発振周波数特性に悪影響を与えることのない、小型の圧電装置を提供すること。

【解決手段】 上側主面の中央部に半導体素子9の搭載部11を有し、上側主面の搭載部11から上側主面の外周部および下側主面にかけて第1の配線導体5−1が形成された第1の絶縁基体2と、下面の中央部に圧電振動子3を収容するための凹部12を有し、凹部12の内側から下面の外周部にかけて第2の配線導体5−2が形成された第2の絶縁基体1と、凹部12の内側に取着され、凹部12に収容される圧電振動子3を封止する蓋体4とを具備しており、第1の絶縁基体2の上側主面の外周部および第2の絶縁基体1の下面の外周部が接合されるとともに第1および第2の配線導体5−1,5−2が電気的に接続されている。

(もっと読む)

差動出力圧電発振器および電子機器

【課題】 圧電発振回路と、この回路から出力されるクロック信号の分配回路とをパッケージに搭載した差動出力圧電発振器およびこの発振器を搭載した電子機器を提供する。

【解決手段】 差動出力圧電発振器10は、圧電発振回路と、前記圧電発振回路から出力される信号に基づいて差動信号を出力するバッファと、前記バッファに接続し、前記差動信号を伝送する一対の伝送線路24と、前記各伝送線路24上に電気的に接続し、いずれか一方の前記伝送線路を跨いで前記伝送線路24の側方に前記差動信号を引出す受動素子28と、前記受動素子28に接続し、前記受動素子28を介して引出された差動信号を伝送する分配伝送線路26とを備えた構成である。

(もっと読む)

圧電発振器

【課題】CMOSインバータを用いた圧電発振器において、電源に発生するスパイクノイズを低減し、消費電流を抑えた高性能、低価格な圧電発振器を提供することを目的とする。

【解決手段】CMOSインバータと、前記CMOSインバータの入出力間に挿入された圧電振動子とを有する圧電発振器において、前記CMOSインバータの電源端子に接続する第1の抵抗と、前記CMOSインバータの接地端子に接続する第2の抵抗とを備えたことを特徴とする圧電発振器。

(もっと読む)

高周波モジュール

【課題】 高周波モジュールの小型化を促進し、且つ、コストの低減を図る。

【解決手段】 高周波モジュール1の回路基板2の裏面を凹設してキャビティ部5を形成する。該キャビティ部5に水晶振動子チップ6を収容すると共に、該回路基板2の上面に搭載するIC3と該水晶振動子チップ6とを上下に位置させて高周波モジュールの小型化を実現する。

(もっと読む)

逓倍型の水晶発振器

【目的】特に出力周波数としての逓倍周波数のズレ及びバラツキを防止し、さらにはスプリアスを抑制した逓倍型発振器を提供する。

【構成】アース用金属膜を両主面に有する中間基板の両側に実装基板を積層してなる多層基板と、前記多層基板の一主面に少なくとも逓倍用のLCフィルタを配置してなる逓倍型の水晶発振器において、前記LCフィルタの配置領域と対向する前記中間基板の一主面に設けられた前記アース用金属膜には、開口部が設けられて生地が露出した構成とする。

(もっと読む)

水晶発振器及び感知装置

【課題】 小型、低消費電力であり、かつ周波数温度特性が良好な水晶発振器を提供すること。

【解決手段】 水晶振動子及び発振回路からなる発振部として第1の発振部1Aと第2の発振部1Bとの2つを用い、これら発振部1A、1Bからの発振周波数の差を取り出しその周波数差の周波数信号を出力する例えばヘテロダイン検波器2を設ける。第1の発振部1Aの共振周波数は、第2の発振部1Bの共振周波数とは異なり、かつその周波数温度特性は、第2の発振部1Bの周波数温度特性と揃っている。

(もっと読む)

圧電発振器及びその製造方法

【課題】 圧電振動素子とICチップを同一のパッケージ内に封止した圧電発振器において発生し易いDLD特性不良を防止できる圧電発振器の製造方法を提供すること。

【解決手段】 シリコンウェハ31の集積回路が形成されていない面をケミカルポリッシュする工程(S2)と、シリコンウェハ31を洗浄する工程(S3)と、シリコンウェハ31をICチップ6個片に切断する工程(S5)と、ICチップ6を絶縁容器の凹陥部内にフェイスダウンでボンディングする工程と、圧電振動素子を絶縁容器内に搭載する工程と、金属蓋により封止する工程とからなる。

(もっと読む)

1,721 - 1,740 / 1,806

[ Back to top ]