Fターム[5J079GA12]の内容

電気機械共振器を用いた発振回路 (23,106) | 発振のための増幅部の構成 (697) | 増幅部の変更、制御 (110) | 電圧利得の変更 (24)

Fターム[5J079GA12]に分類される特許

1 - 20 / 24

絶縁アンプ

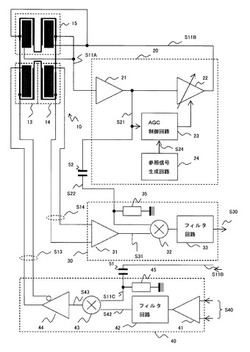

【課題】機械振動を応用した絶縁アンプは、1次側から2次側へ伝達する振動振幅は振動体のQ値に依存するため、変調レベルが安定せずアナログ信号を高精度で伝達できない。また、Q値が高い振動体を使うと入力信号の変化への追従性が悪くなり、帯域幅がほとんど得られない。

【解決手段】Q値の高い同一の振動体上に、第1の振動数を有する発振用振動子と第2の振動数を有する絶縁用振動子とを形成し、特に第1の振動数と前記第2の振動数とには所定の差を持たせる。発振用振動子により第1の振動数で発振するAGC機能付きの発振器を構成し、この発振信号に絶縁アンプ入力信号による振幅変調をかけて絶縁用振動子の1次側を振動させ、絶縁用振動子の2次側から得られる信号をAGCモニタ信号をもとに復調することで絶縁アンプ出力信号を得る。

(もっと読む)

発振器

【課題】異常発振を抑圧する発振器を提供する。

【解決手段】発振信号を起動および増幅する増幅部120と、所望の発振周波数を決定する共振部130と、を備えた発振回路110と、発振回路110の出力端子に緩衝回路160が接続された発振器100であって、増幅部120は入出力用の2端子を有する低域濾波器140と、3段の増幅回路とを有し、増幅部120の1段目増幅器121と2段目増幅器122とが不平衡型増幅器で、3段目増幅器123がオペアンプであり、2段目増幅器122の出力端子が、低域濾波器140の入力端子と3段目増幅器(オペアンプ)123の反転入力端子に接続され、低域濾波器140の出力端子が、3段目増幅器(オペアンプ)123の非反転入力端子に接続されている。

(もっと読む)

圧電発振器

【課題】同一のICを用いて広範囲の周波数に対応した圧電発振器を得る。

【解決手段】圧電振動子と、発振回路と、定電流回路と、メモリ回路と、を備えた圧電発振器であって、前記発振回路は、トランジスタのコレクタとベースとの間にコレクタ電位を決める第1の可変抵抗回路を有し、前記定電流回路は、複数のカレントミラー回路からなり、出力電流に関わるカレントミラー回路のトランジスタ素子に第2の可変抵抗回路が接続され、前記メモリ回路の出力部は、前記発振回路の第1の可変抵抗回路と、前記定電流回路の第2の可変抵抗回路と、に信号線で接続され、前記定電流回路の出力電流を制御し、前記トランジスタのコレクタ電位を制御する圧電発振器を構成する。

(もっと読む)

圧電発振器

【課題】安定駆動に達するまでの時間を短縮した圧電発振器を提供する。

【解決手段】本発明の水晶発振器(圧電発振器)50は、水晶振動子(圧電振動子)1と、水晶振動子1に接続されて発振ループを形成して発振信号を出力する水晶発振部(圧電発振部)24、及び水晶発振部24の起動時に自励発振する自励発振部25により構成された発振回路と、を備え、自励発振部25の周波数が水晶発振部24の周波数よりも高く設定されている。尚、自励発振部25は、複数のコンデンサー(容量素子)C、インバーター5及び抵抗素子4により構成され、複数のコンデンサーCの合成容量の値を調整するために、調整手段6を備えている。

(もっと読む)

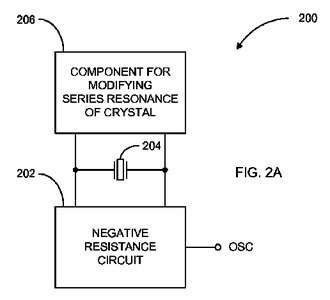

発振器の電力消費を低減させるためのシステムおよび方法

負性抵抗回路と、クリスタルと、発振信号を生成することにおいて、負性抵抗回路の電力消費を減らすために、クリスタルの直列共振を修正するように適合されるコンポーネントとを含む発振信号を生成するための装置。このコンポーネントは、正のリアクタンス回路、1つまたは複数の誘導性素子、またはクリスタルに結合された一対の誘導性素子を含む。この装置は、クリスタルに結合された可変キャパシタのような、発振信号の周波数を調整するための周波数同調コンポーネントを更に含む。負性抵抗回路は、デジタルインバータ回路、反転アナログ増幅器、または自己調整回路を含みうる。この装置は、負性抵抗回路に定常電流を供給するための静止電流ソースと、発振信号が、定義された定常状態に達するのを促進するために、スタートアップ中にのみ、負性抵抗回路にブースト電流を供給するためのスタートアップ電流ソースとを具備する。  (もっと読む)

(もっと読む)

クリスタル発振器

【課題】製造試験段階で出力周波数を調節するために、負荷容量を調節する際に、発振器コア電流を自動的に変化することによって出力信号のスイングを一定に維持する。

【解決手段】クリスタル発振器はクリスタル1とクリスタル発振器回路3とを具備する。負荷コンデンサのバンクC1からC6はそれぞれのスイッチ9から19によって回路にあるいは回路から切り換えられることができる。スイッチは制御ラインD0からD5によって制御され、トリムレジスタとして既知である6ビットレジスタによって設定される。トリムレジスタの値は出力信号の周波数に従って設定される。出力信号のスイングを打ち消すために、電流スイッチのバンクT1からT4が設けられ、抵抗R1からR4が回路にあるいは回路から切り換えることができるようにする。各抵抗R1からR4は制御ラインのそれぞれの1つによって切り換えられる。

(もっと読む)

発振制御回路

【課題】発振開始時からデューティが50%に安定する発振制御回路を提供する。

【解決手段】作動制御回路3が、発振信号の発振電位がCMOSインバータIV1の反転電位よりも低い第1基準電位よりも低くなるまでMOSトランジスタT11及びT12をオフ状態、MOSトランジスタT2をオン状態に保持する。作動制御回路3が、発振信号の発振電位が第1基準電位よりも低くなったとき出力が反転するCMOSインバータIV31と、CMOSインバータ31の後段に設けた抵抗R31とコンデンサC31とからなるローパスフィルタ31と、ローパスフィルタ31の出力が閾値を越えると出力が反転するCMOSインバータ33と、を有している。

(もっと読む)

固体振動子発振回路およびこれを用いた物理量センサ

【課題】振動子を定常励振させるまでに要する時間、すなわち、起動時間を短縮するとともに、増幅器の出力電圧波形の飽和や、ノイズの増幅、増幅度変化後の振動子の発振状態の安定性といった問題を解決した固体振動子発振回路を提供する。

【解決手段】振動子12と、振動子からの出力電流を電圧に変換する電流電圧変換回路14と、該電流電圧変換回路14からの出力電圧を増幅するための増幅器16,18を備えた固体振動子発振回路10であって、増幅器16,18は、その増幅器の増幅度を変化させる可変電流スイッチ20,22を備え、可変電流スイッチ20,22は、電流電圧変換回路14からの出力電圧に基づいて、流れる電流の大きさが連続的に変化し、増幅器16,18の増幅度を連続的に変化させるように構成する。

(もっと読む)

高周波コルピッツ回路

【課題】 高周波においても安定した発振を実現でき、回路規模を小さくできる高周波コルピッツ回路を提供する。

【解決手段】 発振用のトランジスタQ1に加え、帰還用のトランジスタQ2を設け、トランジスタQ1のコレクタがトランジスタQ2のベースに接続し、トランジスタQ2のコレクタには電源電圧が抵抗R5を介して印加されると共に出力端子に接続され、当該コレクタが帰還抵抗Rfを介してトランジスタQ1のベースに接続され、当該ベースには、水晶振動子、直列接続のコンデンサC1とコンデンサC2の一端が接続され、他端が接地され、トランジスタQ1のエミッタには、コンデンサC1とコンデンサC2との間の点が接続されると共に、抵抗R4を介して接地される高周波コルピッツ回路である。

(もっと読む)

結合共振器のアレイ、バンドパスフィルタおよび発振器

【課題】共振中心周波数、帯域幅の調整が容易な結合共振器アレイ及びそれを使用したフィルタ並びに発振器を提供する。

【解決手段】結合共振器16iのアレイ10は、入力電気信号Veを供給するための手段12と、この入力電気信号を使用してアレイのN個の結合共振器16iを電気的に励起するための手段14とを備える。電気励起手段14は、これらN個の結合共振器16iのそれぞれに関して、入力電気信号に従ってこの結合共振器を作動させるために入力電気信号供給手段12に接続された作動手段18iと、この結合共振器16iを作動させるための結合共振器固有の可変利得入力増幅手段20iとを備える。さらに、それらは、入力増幅手段20iのそれぞれの可変利得の特定の設定を制御するための手段22を備える。

(もっと読む)

SAW発振回路、電圧制御発振器及び発振回路

【課題】発振回路に可変容量ダイオードや、コイルを不要とし、発振回路のIC化を容易にするSAW発振回路とそれを用いた電圧制御発振器を提供する。

【解決手段】SAW共振子2と、SAW共振子2の出力側に接続されて帰還増幅器として機能し利得を可変可能な第1の増幅器3と、SAW共振子2の出力側に接続されて帰還増幅器として機能し利得を可変可能とすると共に、第1の増幅器3に入力される信号とは位相が180°異なるSAW共振子2の出力信号が入力される第2の増幅器4と、第1の増幅器3の出力信号を移相する移相器5と、移相器5が出力信号と第2の増幅器4の出力信号とを加算演算する演算器として加算器6とを、備え、加算器6の出力信号をSAW共振子2にフィードバックすると共に発振信号として出力するようにした。

(もっと読む)

発振回路

【課題】動作電圧範囲の広い発振回路を提供する。

【解決手段】両端にキャパシタc1、C2が接続された振動子11と、出力抵抗R1を介して振動子11に並列接続されたインバータ12を有する反転増幅部13と、インバータ12に並列接続されたトランスミッションゲート14、15を有する帰還抵抗部16と、同一導電型で、閾値電圧の異なるn型第1および第2MOSトランジスタM1、M2の直列回路を有し、電源電圧Vddのレベルに応じて、第1および第2MOSトランジスタM1、M2が相補的にオンまたはオフして帰還抵抗部16の抵抗値を可変するための制御信号A1、A2を出力する制御手段17と、を具備する。

(もっと読む)

発振回路

【課題】発振回路において、起動時間を有効に短縮できる発振回路を提供する。

【解決手段】本発明の発振回路は、振動子とこの振動子を駆動する第1の電圧信号とこの第1の電源電圧信号よりも高い電圧により振動子を駆動する第2の電圧信号と前記振動子の振幅を増幅するための増幅回路とを有する発振回路において、前記第1の電圧信号によって前記振動子の駆動を開始し、その後に前記第1の電圧信号から前記第2の電圧信号へ切り替える切り替え信号を発生する切り替え信号発生回路を備える。これにより、振動子を安定して駆動するまでの起動時間を有効に短縮した発振回路を提供できる。

(もっと読む)

発振回路

【課題】 共振子を有し、発振開始時間が早く、同時に信号の波形が潰れることのない発振回路を提供する。

【解決手段】 発振回路は、SAW共振子等の共振子と、共振子で生成された高周波などの信号を増幅して出力すると共に共振子に帰還信号を出力する差動増幅器と、電源投入時から所定時間と所定時間経過後とで差動増幅器の利得を変える手段を有している。利得を変える手段として、例えば、差動増幅器に、定電圧源に接続された第1のトランジスタ13と、定電圧源あるいは第2の電源にスイッチ15を切り替えることにより接続される第2のトランジスタ14を有する利得調整回路を配置する。スイッチ15の接離により、安定した振幅で発振を開始するまでの時間が短縮でき、安定発振後に回路の利得を抑えることにより信号の波形が潰れることの無い発振回路が実現できる。

(もっと読む)

発振装置

【課題】 ベース電流を減少させることなく、発振装置の負性抵抗を大きくする。

【解決手段】バイポーラトランジスタと、当該バイポーラトランジスタのベースに接続さ

れた圧電振動子とを有する発振回路と、前記バイポーラトランジスタのベース電極に入力

端が接続されているインバータ素子と、前記インバータ素子の入力端及び出力端間に接続

された抵抗器と、を含む。

(もっと読む)

半導体装置

【課題】製造プロセスの追加やトランジスタ動作の不安定さを招くことなく、発振用インバータを用いて構成された発振回路を搭載する半導体装置を提供する。

【解決手段】本発明の半導体装置において、複数のMOSトランジスタはノーマリーオフ型のもので、製造プロセスが許容する最小寸法に等しいゲート長において所定の閾値を有し、最小寸法に比較してゲート長が大きくなるにつれて閾値の絶対値が小さくなる特性を有する。本発明の半導体装置は、最小寸法以上の範囲で、相対的に長いゲート長を有する第1のMOSトランジスタからなる第1の発振用インバータと、相対的に短いゲート長を有する第2のMOSトランジスタからなる第2の発振用インバータと、第1および第2の発振用インバータに電源電圧を供給する電源配線と、電源電圧に応じて、第1および第2の発振用インバータの一方を動作可能とする選択回路とを有する。

(もっと読む)

発振回路、物理量トランスデューサ及び振動ジャイロセンサ

【課題】 簡素な構成で、発振ループ内の振幅制御を高精度で実現し発振起動時間を短縮する発振回路、物理量トランスデューサ及び振動ジャイロセンサを提供する。

【解決手段】 発振回路10は、制御電圧Vcの変化に対するそのゲインの変化を示す所与の感度特性を有し、発振ループ内の発振振幅を制御するためのゲインコントロールアンプ20と、発振振幅に応じてゲインコントロールアンプ20のゲインを調整するための制御電圧Vcを出力するゲイン制御回路30とを含む。ゲイン制御回路30は、発振振幅を監視して発振ループ内の発振が定常状態か起動過程かを判別する。ゲインコントロールアンプ20は、発振が起動過程と判別されたとき、制御電圧Vcに基づいて第1の感度特性に従ってそのゲインを変化させ、発振が定常状態と判別されたとき、制御電圧Vcに基づいて第1の感度特性より感度の低い第2の感度特性に従ってそのゲインを変化させる。

(もっと読む)

発振回路、物理量トランスデューサ及び振動ジャイロセンサ

【課題】 簡素な構成で、発振ループ内の振幅制御を高精度で実現し、発振の起動時間を短縮できる発振回路、物理量トランスデューサ及び振動ジャイロセンサを提供する。

【解決手段】 発振回路10は、発振ループ内の発振振幅を制御するためのゲインコントロールアンプ20と、発振振幅に応じてゲインコントロールアンプ20のゲインを調整するための制御電圧を出力するゲイン制御回路30とを含む。制御電圧をVc、ゲインをkとした場合に、発振ループ内の発振が定常状態か起動過程かにかかわらず、Vc×kの値が一定である。

(もっと読む)

高速始動付き低雑音基準発振器

速い始動時間及び定常状態での低い雑音を有する周波数源が提供される。周波数源は、発振器(102)と、発振器始動でのアナログAGCループと定常状態の動作でのデジタルAGCループとの間を切り替えるハイブリッド自動利得制御(AGC)ループとを含む。アナログAGCループは、発振器(102)に接続されたピーク検出器(104)と、ピーク検出器(104)出力と基準電圧との差を積分する誤差積分器(106)とを含む。デジタルAGCループは、ピーク検出器出力と高/低基準電圧とを比較する比較器(110)と、タイマ信号を与える発振器(102)カウンタと、デジタル・ワードを供給されるデジタル/アナログ変換器(DAC)(114)と、DAC(114)と発振器(102)との間のロー・パス・フィルタ(116)とを含む。タイマ信号は、マルチプレクサ(108)にアナログAGCループ又はデジタルAGCループのいずれかを選択させる。  (もっと読む)

(もっと読む)

圧電発振器回路

【課題】

解決しようとする課題は、雑音特性とエージング特性に優れると供に、消費電力化及び小型化を実現できる発振器回路を提供することである。

【解決手段】

本発明は、FETを発振用増幅器とした圧電発振器であり、FETのゲート・ソース間電位を制御する為のAGC回路がダイオードから成る整流回路を備えた単純構造であることを特徴とする。

(もっと読む)

1 - 20 / 24

[ Back to top ]