Fターム[5J081CC04]の内容

LC分布定数、CR発振器 (9,854) | 目的、効果 (1,425) | 特性の改善 (481) | 高速化(起動時を含む) (18)

Fターム[5J081CC04]に分類される特許

1 - 18 / 18

ディジタル制御発振装置および高周波信号処理装置

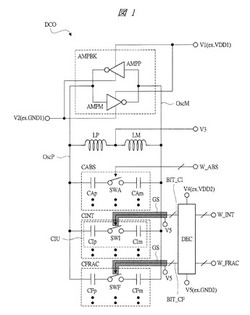

【課題】DNLの低減を実現可能なディジタル制御発振装置を提供する。

【解決手段】例えば、発振出力ノードOscP,OscM間に並列に結合されるアンプ回路ブロックAMPBK、コイル素子LP,LM、複数の単位容量ユニットCIU等を備え、各CIUは、容量素子CIp,CImと、当該CIp,CImを発振周波数の設定パラメータとして寄与させるか否かを選択するスイッチSWIを備える。ここで、SWIは、デコーダ回路DECからのオン・オフ制御線BIT_CIによって駆動され、当該BIT_CIは、シールド部GSによってOscP,OscMとの間でシールドされる。

(もっと読む)

改良された帯域幅を備える電圧制御発振器を有する位相同期ループ回路

【課題】改良された電圧制御発振器を提供する。

【解決手段】電圧制御発振器(16)は複数の直列に接続された合成利得段(42、44、46)を含む。合成利得段はトランスコンダクタンス段(48)及びトランスインピーダンス段(50)を含む。トランスコンダクタンス段は第1電源電圧端子から第2電源電圧端子への第1電流経路(52、56、64)及び第2電流経路(54、58、66)を有する。第1可変抵抗(62)は第1電流経路と第2電流経路との間に接続される。トランスインピーダンス段は、第1電流経路の出力に接続された入力端子と、出力端子とを有する第1インバータ(68、72)及び第2電流経路の出力に接続された入力端子と、出力端子とを有する第2インバータ(70、74)を有する。第2可変抵抗(76)は第1インバータの入力端子と出力端子との間に、第3可変抵抗(78)は第2インバータの入力端子と出力端子との間に接続される。

(もっと読む)

圧電発振器

【課題】水晶発振器などの圧電発振器において、出荷時あるいは受け入れ時の調整や検査に際して発振器特性の計測に要する時間を短縮でき、かつ、電子機器への搭載後においても一時的な電源断に対応できるようにする。

【解決手段】水晶振動子12などの圧電振動子と発振回路16とを収容した容器10内に、二次電池11と、二次電池11に対する充放電を制御する充放電制御回路14と、電源端子に外部電源電圧Vccが印加されているときには電源端子を選択し、それ以外の場合に充放電制御回路14を選択して電力を発振回路16に供給する切替回路15と、を設ける。

(もっと読む)

圧電発振器

【課題】安定駆動に達するまでの時間を短縮した圧電発振器を提供する。

【解決手段】本発明の水晶発振器(圧電発振器)50は、水晶振動子(圧電振動子)1と、水晶振動子1に接続されて発振ループを形成して発振信号を出力する水晶発振部(圧電発振部)24、及び水晶発振部24の起動時に自励発振する自励発振部25により構成された発振回路と、を備え、自励発振部25の周波数が水晶発振部24の周波数よりも高く設定されている。尚、自励発振部25は、複数のコンデンサー(容量素子)C、インバーター5及び抵抗素子4により構成され、複数のコンデンサーCの合成容量の値を調整するために、調整手段6を備えている。

(もっと読む)

発振器、および発振を開始する方法

【課題】休止期間は消費電力を削減すると共に起動特性のよい発振器を提供する。

【解決手段】発振信号がコールドスタートからの規定の定常状態条件に達する時を早める回路を含んでいる発振信号を生成するための装置。装置は、発振信号を生成するための発振回路412と、前記発振回路に第1の電流を供給する第1の制御可能電流源404と、発振回路に第2の電流を供給する第2の制御可能電流源408と、を含み、第1および第2の電流は、発振信号が規定の定常状態条件に達するための時間分を縮小するのに適している。装置は、1以上の通信チャネルを確立するために低い負荷サイクルパルス変調を用いる通信システムに有益であるかもしれず、それによって装置はパルスのほぼ始めで発振信号を生成し始め、パルスのほぼ終わりに発振信号を終了する。

(もっと読む)

MEMSデバイス、電子機器

【課題】実装面積やコストを抑え、起動時間を短縮し、周波数精度の高いクロックも出力できるMEMSデバイス等を提供する。

【解決手段】 第1のクロック信号400と第2のクロック信号402の少なくとも一方を出力するMEMSデバイス100であって、同一の基板上に設けられた第1のMEMS共振子302を有する第1のMEMS発振器300と第2のMEMS共振子322を有する第2のMEMS発振器320とを含み、第1のMEMS発振器の共振周波数である第1の共振周波数と、第2のMEMS発振器の共振周波数である第2の共振周波数とは略一致し、第1のMEMS共振子のQ値と第2のMEMS共振子のQ値とは異なり、第1のMEMS発振器は、第1の共振周波数を周波数とする第1のクロック信号を出力し、第2のMEMS発振器は、第2の共振周波数を周波数とする第2のクロック信号を出力する。

(もっと読む)

発振回路

【課題】従来の発振回路は、発振信号を増幅させる電流等の影響で発振周波数の高速化が制限されるという問題があった。

【解決手段】本発明にかかる差動発振回路は、帰還ループ回路を備えた差動型の発振回路であって、帰還ループ回路上に縦続接続され、入力された一対の差動入力信号を遅延させて一対の差動出力信号として出力する遅延回路2〜5と、発振回路が発振起動状態か安定状態のいずれかにあるかを検出し、検出結果を示す検出信号VSTPを出力する発振起動検出回路7と、を備える。さらに遅延回路2〜5は、発振起動検出回路7から出力された検出信号VSTPに基づいて、差動出力信号の出力電流値を制御する。このような回路構成により、発振周波数の高速化が可能である。

(もっと読む)

発振器制御装置

【課題】安定した位相雑音特性を高速に得ることができる発振器制御装置を提供する。

【解決手段】動作電流制御信号に基づく動作電流を供給する可変電流源14を含み、発振器調整ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器1と、前記発振信号と基準信号との間の位相差を算出し、位相差信号を出力する位相差算出部(2,3,4)と、前記デジタル制御発振器の発振周波数を設定するための周波数命令ワードと前記位相差信号との差分を平滑化して、前記発振器調整ワードを出力するフィルタ6と、前記発振器調整ワードを測定し、前記動作電流制御信号を出力する制御部7と、を備え、前記制御部は、前記動作電流の値を変化させるように前記動作電流制御信号を出力し、前記発振器調整ワードが極大値となる前記動作電流の値を抽出し、前記可変電流源が供給する動作電流がこの抽出した値となるように前記動作電流制御信号を出力する。

(もっと読む)

温度補償型圧電発振器

【課題】圧電振動素子を搭載した温度補償型圧電発振器の小型化が進んでも、消費電力が少なく、短時間で立ち上がり、温度補償型圧電発振器の表面に新たに外部接続用電極端子を設けることがない温度補償型圧電発振器を提供することを課題とする。

【解決手段】第1のスイッチは、機能端子から入力された信号により電源電圧端子と増幅回路部の第2のインバータとの間を接続または切断し、第2のスイッチは、切替信号制御回路部からの切替信号により、第1のスイッチ又は可変容量ダイオードのカソードと、機能端子との接続を切り替え、第3のスイッチは、チップセレクト回路部からの切替信号により、メモリ部又は、第2のスイッチと、機能端子との接続を切り替える。

(もっと読む)

発振回路及び半導体装置

【課題】本発明は、発振回路及び半導体装置に関し、電源投入後、リセット後、スタンバイ状態からの復帰後のMCUの処理の高速化と低消費電力化を両立することを目的とする。

【解決手段】第1の発振回路と、第1の発振回路より長い発振安定時間を有する第2の発振回路と、第2の発振回路の発振安定時間の経過を示す安定信号を出力する信号生成回路と、選択信号に基づいて第1及び第2の発振回路の出力の一方を選択出力するスイッチ回路と、抑止信号に基づいて第2の発振回路の起動を抑止する抑止回路とを備え、第1及び第2の発振回路が同時に起動されてスイッチ回路により第1の発振回路の出力が選択出力された後に第2の発振回路の出力に切り替えられるモードと、第1の発振回路が起動されて抑止回路により第2の発振回路が起動されずスイッチ回路により第1の発振回路の出力のみが選択出力されるモードを有するように構成する。

(もっと読む)

電圧制御発振器および電圧制御発振器の発振周波数制御方法

【課題】電圧制御発振器で使用される可変容量において、回路のグラウンド電位から電源電位以上に広い可変容量の線形領域を使用することが可能な電圧制御発振器を提供する。

【解決手段】共振回路を構成するインダクタ2a、2bと可変容量10a、10b、11a、11b、12a、12bと、共振回路の共振周波数を制御するための周波数制御端子5とを備えた発振部200に加え、共振回路にバイアス電圧を与えるバイアス回路201と、周波数制御電圧に応じてバイアス回路201のバイアス電圧を切り替え制御するバイアス制御回路202を設ける。バイアス制御回路202は周波数制御電圧が変化してしきい値を超えたときに、周波数制御電圧を目的の制御電圧に近づける方向にバイアス電圧を切り替える。

(もっと読む)

差動発振装置及び変調器

【課題】差動発振装置において発振開始時から二つの出力端子から出力される出力信号の位相が反転するまでの時間を短縮すること。

【解決手段】一方のトランジスタ105の端子に外部入力端子を有しスイッチ回路104を有する差動発振部103と、前記差動発振部103の発振開始と発振停止を制御する第一の制御信号を生成する第一の制御信号発生回路101と、前記差動発振部103の一方のトランジスタ105の端子に入力する第二の制御信号を生成する第二の制御信号発生回路102とを有する差動発振装置において、第二の制御信号によって二つのトランジスタ105,106に流れるコレクタ電流の位相関係を決めることで、発振開始時から二つの出力端子から出力される出力信号の位相は逆相となる。

(もっと読む)

間欠動作回路及び変調装置

【課題】小回路規模、低消費電力で、立ち上がりと立ち下がりの速い出力波形を得ることができる間欠動作回路を提供すること。

【解決手段】能動回路106と、能動回路106の動作開始と動作停止を制御する第1の制御信号S1を生成する第1の制御信号生成回路101と、能動回路106にリンギング振動を起こさせ、かつ、そのリンギング振動の周波数と振幅値を制御することができる第2の制御信号S2を生成する第2の制御信号生成回路102と、能動回路106からリンギング振動と安定振動が継続して出力されるように、第1及び第2の制御信号S1、S2の能動回路106への入力タイミングを調整するタイミング調整回路103とを設けるようにする。

(もっと読む)

静磁波発振装置

【課題】

静磁波発振装置において、外部からの衝撃や周期的な振動などの外的要因により、空隙の間隔が急激に変化した場合には、静磁波素子用磁気回路の磁界の強さが急激に変動するため、発振周波数も急激に変動する。発振周波数制御装置は、静磁波発振装置の出力を監視して、制御信号をコイル電流制御回路に出力しているため、発振周波数の急激な変動には対応できない。この結果、所望の周波数ではない発振出力を出してしまう。従来のように静磁波発振装置の出力を監視してから制御信号を出力し、発振周波数を制御する方法では、静磁波素子に印加される磁界の強さが急激に変動した場合に対応できない問題があった。

【解決手段】

本発明では、磁気検出素子を用いて静磁波素子に印加される磁界の強さを直接監視し、磁界の強さを調節するコイル電流に反映させることにより、自動的に安定した発振周波数を出力できる。

(もっと読む)

誘電体共振器装荷型発振回路及びこれを用いたレーダー装置

【課題】 誘電体共振器装荷型発振回路の立ち上がり時間及び/又は立ち下がりを短縮する。

【解決手段】 誘電体共振器11と、誘電体共振器11に共振電圧を与える駆動回路20と、共振電圧を生成するために必要な電圧Vdsを駆動回路20に与えるスイッチ71と、共振電圧の生成を停止させるグランド電圧を駆動回路20に与えるスイッチ72と、スイッチ71から見て電圧Vdsを供給する電源端子側に接続され、駆動回路20が発生するノイズを除去するコンデンサ42とを備える。そして、これらスイッチ71,72を排他的に導通させれば、スイッチ72をオンさせることにより直ちに発振を停止させることができ、また、スイッチ71のオン・オフにかかわらず、コンデンサ32は常に電荷が蓄積された状態となることから、スイッチ71がオンすると直ちに発振動作を行うことが可能となる。

(もっと読む)

発振装置及び発振方法

【課題】 従来の発振装置では、CR発振回路は、水晶発振回路の発振の起動の支援を充分に適切に行うことができなかった。

【解決手段】 本発明に係る発振装置は、水晶発振子により規定される周波数を有する第1の信号を発振する水晶発振回路と、前記水晶発振回路が前記第1の信号を定常的に発振するまでの過渡期において、前記周波数と実質的に同一な第2の周波数を有する第2の信号を生成し、当該第2の信号を前記水晶発振回路に供給するCR発振回路とを含む。

(もっと読む)

YIG発振器のコイル電流ドライブ回路および周波数シンセサイザ

【課題】大電流の出力が可能な電源は単一であり、そして高い電源電圧を必要としない、YIG発振器のコイル電流ドライブ回路を提供する。

【解決手段】設定入力に応じた電流をYIG発振器のメインコイルに流すコイル電流ドライブ回路において、電荷を蓄積して電位差を保つコンデンサと、このコンデンサの基準電源電位を切り替える2つのスイッチと、基準電源電位を切り替えたときに主電源との経路を遮断するスイッチによって構成され、制御信号に応じて前記各スイッチを一時的にメインコイルのプルアップ電位を上昇させるように切り替えることにより、高速電流ドライブ時に前記メインコイルが起電力を発生するように構成する。

(もっと読む)

LC発振器を備えたPLLの粗チューニング時間の改良

LC発振器のチューニング方法と装置が開示されている。本発明の実施形態は、ビット比較時間を適応的に制御し、最少の粗チューニング時間が得られるようにすることを含んでいる。ビット比較時間は、LC発振器のキャパシタアレイ内の対応する加重キャパシタの冗長量に逆比例してスケーリングされる。 (もっと読む)

1 - 18 / 18

[ Back to top ]