Fターム[5J081CC22]の内容

LC分布定数、CR発振器 (9,854) | 目的、効果 (1,425) | 調整・制御 (181) | 周波数の可変・調整 (135)

Fターム[5J081CC22]に分類される特許

61 - 80 / 135

発振装置

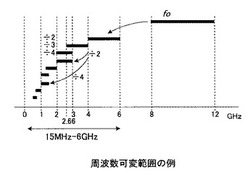

【課題】通信機などが必要とする発振装置の発振周波数範囲の広帯域化が、簡単な構成で精度よく行えるようにする。

【解決手段】8GHzから12GHzなどの第1の周波数帯域幅の可変範囲を持つ低位相雑音な発振手段と、発振手段の発振出力を分周する周波数分周器とを備える。発振手段が出力する発振信号の周波数と、周波数分周器で分周する分周比を制御して、周波数分周器の出力周波数を、発振手段の発振周波数以下の周波数で、第1の周波数帯域幅と同じかそれ以上の周波数帯域幅で可変設定される所望の周波数とする制御を行う。

(もっと読む)

静磁波発振装置

【課題】

静磁波発振装置に於ける磁極間の空隙の距離が磁界の強さを決定する一因であることを利用し、多くの周波数帯域に対応できる静磁波発振装置を提供する。

【解決手段】

所定の空隙7を形成する様に磁極3,8が対峙して配設され、前記空隙に磁界15が形成され、前記空隙内に発振回路基板9を介して静磁波素子12が設けられた静磁波発振装置1であって、前記磁極間の距離を変更可能とし、該距離を変更することで発振周波数を変更可能とした。

(もっと読む)

発振回路、異常発振検査方法、高周波受信機、及び高周波送信機

【課題】複数の電圧制御発振器を有するにもかかわらず異常発振の有無検査の検査時間を短縮することができる発振回路を提供する。

【解決手段】動作電流がそれぞれ異なる値である第1から第n(nは2以上の自然数)の電圧制御発振器VCO1〜VCOnと、1つの基準電圧生成回路RV0と、第1から第n(nは2以上の自然数)のスイッチSW1〜SWnとを備え、すべてのk(k=1〜n)について、第kの電圧制御発振器VCOkの直流バイアス入力端子T_kと基準電圧生成回路RV0の直流バイアス出力端子T_0との間に第kのスイッチSWkが設けられており、第kのスイッチSWkがオン状態のときに基準電圧生成回路RV0から第kの電圧制御発振器VCOkの差動トランジスタにベースバイアス電圧が供給される発振回路。

(もっと読む)

遅延素子、可変遅延線及び電圧制御発振器並びにそれを備えた表示装置及びシステム

【課題】温度が変化しても中心発振周波数が安定している電圧制御発振器等を、簡単な構成で提供する。

【解決手段】入力信号Viに遅延量τdを加えて出力信号Voとする遅延発生部11と、遅延τdを制御する遅延制御部12とを備えている。遅延制御部12は、遅延量τdを調節する第一の制御信号としての制御信号S1を出力する遅延調節回路13と、温度による特性変化を補償する第二の制御信号としての制御信号S2を出力する温度補償回路14とを有し、制御信号S1と制御信号S2とを合成して得た第三の制御信号としての制御信号S3を遅延発生部11へ出力することにより遅延量τdを制御する。遅延制御部12は、遅延調節回路13と温度補償回路14とを直列に接続することにより、制御信号S3を得ている。

(もっと読む)

電圧電流変換回路、及び電圧制御発振回路

【課題】入力電圧に対する出力精度の高い電圧電流変換回路、及び電圧制御発振回路を提供する。

【解決手段】電圧電流変換回路は、入力端子1に入力された入力電圧を電流に変換して、出力する電圧電流変換回路であって、入力端子1に接続されたゲートを有するNMOS4を含み、NMOS4に流れる電流に応じた出力電流を発生する第一電流発生回路11と、ソース、及びドレインと異なる電位となるゲートを有するNMOS8を含み、NMOS8に流れる電流に応じた重畳電流を発生して、NMOS4に供給する第二電流発生回路と、を備えたものである。

(もっと読む)

半導体集積回路及び電圧制御発振器

【課題】待機状態から任意の容量安定状態への過渡時間の短いMOSバラクタを提供する。

【解決手段】Nウェルを有するMOSバラクタ素子の動作待機時に電極の電位からウェル領域の電位を引いた電位差を0以上にする制御回路を備えることにより、動作待機時から任意の容量安定状態への過渡時間を短くすることが可能となる。また、Pウェルを有するMOSバラクタ素子の動作待機時に電極の電位からウェル領域の電位を引いた電位差を0以下にする制御回路を備えることにより、動作待機時から任意の容量安定状態への過渡時間を短くすることが可能となる。

(もっと読む)

電気的に制御される磁気回路を備えた装置の駆動回路

【課題】

部品の着脱作業を要することなく、簡単に、発振器等磁気回路を備えた装置単体での、周波数特性の検査を可能とした電気的に制御される磁気回路を備えた装置の駆動回路を提供する。

【解決手段】

信号レベル調整部14と積分回路部15とを具備する電気的に制御される磁気回路を備えた装置の駆動回路であって、前記積分回路部がOPアンプ23と、該OPアンプに対して並列に接続されたコンデンサ27と、並列に接続された負帰還用の抵抗28と、該抵抗を前記OPアンプに対して継断するスイッチング手段33,32とを有し、該スイッチング手段が前記抵抗を断状態とすることで、前記積分回路部が積分回路として動作し、前記スイッチング手段が前記抵抗を継状態とすることで、前記積分回路部が増幅回路として動作する様構成した。

(もっと読む)

調整可能な周波数を備える信号発生器

発振信号の周波数は、出力信号の位相および/または周波数を調整するために一時的に調整される。例えば、発振信号の周波数は、出力信号の位相を調整するために、極めて短期間で調整されてもよい。加えて、発振信号の周波数は、出力信号の有効周波数を調整するために、反復される手法で一時的に調整されてもよい。いくつかの態様では、発振信号の周波数は、発振回路に関連したリアクタンス回路の再構成によって調整される。  (もっと読む)

(もっと読む)

集積回路装置

【課題】VCOを備える周波数シンセサイザに関し、VCOのf−V特性のばらつきに対処する手法を提案する。

【解決手段】制御電圧V1に応じて発振周波数f1が変化する第1の電圧制御発振器を備え、基準周波数に応じた周波数の信号を発振する第1の周波数シンセサイザと、制御電圧V2に応じて発振周波数f2が変化する第2の電圧制御発振器を備え、前記第1の周波数シンセサイザと同じチップ上に設けられており、前記基準周波数に応じた周波数の信号を発振する第2の周波数シンセサイザと、前記第1の電圧制御発振器の制御電圧V1をモニタし、前記第1の周波数シンセサイザの周波数がロックしているときにモニタされた前記制御電圧V1と基準電圧とを比較し、前記制御電圧V1と前記基準電圧との比較結果に基づいて、前記第2の電圧制御発振器のf2−V2(発振周波数−制御電圧)特性を変化させるコンパレータとを備えることを特徴とする集積回路装置。

(もっと読む)

発振器、および発振を開始する方法

発振信号がコールドスタートからの規定の定常状態条件に達する時を早める回路を含んでいる発振信号を生成するための装置。装置は、発振信号を生成するための発振回路と、発振回路に第1の電流を供給する第1の回路と、発振回路に第2の電流を供給する第2の回路と、を含み、第1および第2の電流は、発振信号が規定の定常状態条件に達するための時間分を縮小するのに適している。装置は、1以上の通信チャネルを確立するために低い負荷サイクルパルス変調を用いる通信システムに有益であるかもしれず、それによって装置はパルスのほぼ始めで発振信号を生成し始め、パルスのほぼ終わりに発振信号を終了する。  (もっと読む)

(もっと読む)

高周波発振回路、位相同期ループ回路、半導体装置及び通信装置

【課題】より大きなQのインダクタを必要とせず、従来技術に比較してより小さいサイズでかつより高い発振周波数で発振させることができる高周波発振回路を提供する。

【解決手段】帰還型高周波発振回路は、短絡スタブ用伝送線路に接続されたゲートと、発振出力端子に接続されたドレインとを有する電界効果トランジスタ1と、電界効果トランジスタ1のソースに接続されたドレインを有するソース接地の電界効果トランジスタ2とを含み構成され、短絡スタブ用伝送線路11及び電界効果トランジスタ2を帰還回路として発振する。また、電界効果トランジスタ2のゲートと、電界効果トランジスタ1のドレインとの間に帰還用キャパシタを接続する。

(もっと読む)

発振器

【課題】簡易な構成で低コストであり、高性能な発振器を提供すること。

【解決手段】発振器は、コイルとコンデンサとを有する共振回路と、この共振回路にて発生した共振を増幅して出力する発振回路と、を備え、発振回路内に形成された発振ループに、所定の通過帯域幅を有するSAWフィルタを介挿すると共に、共振回路に対して並列に、当該共振回路の容量値を変化させる素子、例えば、可変容量ダイオードを接続した。また、上記発振器に、温度に応じた値の電圧を可変容量ダイオードに印加する電圧印加手段を有する温度補償回路を備えた。

(もっと読む)

自動式の自己トリミングを有する聴取装置及び対応する方法

【課題】聴取装置のLC共振回路を所望の周波数範囲で持続的に作動させる。

【解決手段】発振器L、Cresと発振器の発振周波数をトリミングするためのトリミング装置11、12とを有する聴取装置において、予め与えられた目標値に依存してトリミング装置11、12を用い発振器の発振周波数を自動的に調節するための調節装置17、18、19を有する。

(もっと読む)

発振器

【課題】発振周波数変更機能を備えた発振器において、不揮発性メモリからデータを読み出す際に発振周波数が変更されることなく安定的に読み出すことができる。

【解決手段】LSIの外部に設けられた不揮発性メモリ15に、発振回路13から発振されるクロック信号の周波数を変更するための周波数設定値が記憶されており、その周波数設定値が、発振回路13から発振される初期設定された周波数のクロック信号によって読み出されると、ダミーレジスタ11に格納される。不揮発性メモリ15からデータが全て読み出されてロード動作完了信号が出力されると、ダミーレジスタ11から記憶レジスタ12へ周波数設定値が格納され、発振回路13の発振周波数が周波数設定値とされる。

(もっと読む)

マイクロ波発振装置

【課題】小型化が可能で、発振周波数を調整してもマイクロ波を安定して発振させるマイクロ波発振装置を提供する。

【解決手段】マイクロ波発振装置100は、基板102上に設けられたマイクロストリップ線路105と、マイクロストリップ線路105上に支持された誘電体共振器110と、の結合によりマイクロ波を発振させる。さらに、マイクロ波発振装置100は、傾斜送り部120を有し、傾斜送り部120はキャビティ103の傾斜板113に設けられている。傾斜送り部120は、発振周波数を調整するための送りねじ115と、送りねじ115用のねじ孔を有する円柱状の角度調整軸117と、所定角度に固定可能な軸受け114と、これらの部品と発振回路とを電磁気的に遮蔽する遮蔽板112と、誘電体共振器110と、遮蔽板112と誘電体共振器110とを接続する接続部111と、を含んでいる。

(もっと読む)

電圧制御発振回路

【課題】ICへの集積化が容易で、かつ、ノイズの発生を低減することも可能な電圧制御発振器を提供する。

【解決手段】抵抗R1,R2と、クロスカップルされた発振用のペアトランジスタM1,M2による正帰還回路と、可変容量ダイオードD1,D2と、可変容量ダイオードD1,D2に対して固定のバイアス電圧を与えるバイアス回路M4,M5とを備え、可変容量ダイオードD1,D2の容量値を同調電圧VTによって可変させることで発振周波数を制御できるようにすることにより、IC化に向かないインダクタや大きな電流性ノイズを出しやすい定電流源を用いずに電圧制御発振器を構成する。

(もっと読む)

VCO回路

【課題】可変周波数範囲の広域化を可能にしつつ高い位相雑音特性を備えるVCO回路を提供する。

【解決手段】上記課題を解決するために、VCO回路100に、バッファ回路B11、P型MOSトランジスタQ11及びキャパシタC11からなるバイアス回路101と、アンプA11と、インダクタL11、可変キャパシタC12、及びスイッチ付きキャパシタC13、C14、・・・からなる共振回路102と、を備える。

(もっと読む)

静磁波発振装置

【課題】静磁波素子が出力する発振信号の発振周波数が高いときでも小型化することのできる静磁波発振装置を提供することを目的とする。

【解決手段】静磁波素子に印加する磁界の強さを変えることで発振信号の周波数を調整する1つ以上の電磁コイルを、永久磁石の外側で且つ筐体の内部に配置することにより、永久磁石の幅寸法を電磁コイルの幅寸法より小さくすると共に、発振周波数が高いことで永久磁石が大きくなることで永久磁石の高さ寸法が大きくなっても、永久磁石が固定される筐体上面部材の凹部の深さ寸法を永久磁石の高さ寸法に合わせて大きくすることにより、静磁波発振装置の小型化を実現する。

(もっと読む)

2バンド発振器

【課題】簡単な構成で二つの発振周波数帯に切り替えることのできる2バンド発振器を提供すること。

【解決手段】第一の発振トランジスタを有して第一の周波数帯で発振する第一の発振回路1と、第二の発振トランジスタを有して前記第一の周波数帯と異なる第二の周波数帯で発振する第二の発振回路2と、エミッタが電源端子に接続され、コレクタから前記第一の発振トランジスタにバイアス電圧を印加する第一のスイッチトランジスタ6と、エミッタが前記電源端子に接続され、コレクタから前記第二の発振トランジスタにバイアス電圧を印加する第二のスイッチトランジスタ9とを設け、前記第一のスイッチトランジスタ9のベースに切替端子8が接続され、前記第二のスイッチトランジスタ9のベースが前記第一のスイッチトランジスタ6のコレクタと接続されており、前記第一のスイッチトランジスタ6と前記第二のスイッチトランジスタ9とをオンとオフとが互いに逆となるように切り替えられる。

(もっと読む)

可変容量回路とこれを用いた電圧制御発振回路

【課題】低電圧動作に適し、動作周波数レンジが広げられ、安定動作が得られ、位相ノイズやジッタの低減を図れる。

【解決手段】電圧可変容量回路は、電圧可変容量手段としてのNMOS42と、NMOS42のドレインにソース電位と異なる電位を供給するための電位供給部41とから構成されている。NMOS42のゲート42gと接地端子GNDとの間に発生する等価容量Cgを可変できる電位範囲や、変化の傾きを電気的・回路設計的に調整することが可能となる。更に、電圧制御端子VCに印加する制御電位vcに対して等価容量Cgは単調に変化し、制御電位vcの有効な電位範囲は拡大する。前記電圧可変容量回路をVCOに用いることで、VCOの発振周波数fは、電圧制御端子VCに印加する制御電位vcによって、制御できる。

(もっと読む)

61 - 80 / 135

[ Back to top ]