Fターム[5J098AA03]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | 半導体素子 (443) | FET (224)

Fターム[5J098AA03]に分類される特許

141 - 160 / 224

インピーダンス変換回路及びそれを用いた電力増幅装置

【課題】複数の周波数帯のインピーダンス条件に対するインピーダンス変換を低損失に行なうことができるようにする。

【解決手段】インピーダンス変換回路10Aは、入力された高周波信号の位相を調整する位相調整用伝送線路4と、その出力側に接続された第1のスイッチ素子6Aと、該第1のスイッチ素子6Aの出力側に設けられ、高周波信号を第1の高周波信号として出力する第1の出力端子7Aと、位相調整用伝送線路4の出力側に接続され、高周波信号を反射可能な第1の反射量調整用伝送線路5と、その出力側に接続された第2のスイッチ素子6Bと、該第2のスイッチ素子6Bの出力側に設けられ、高周波信号を第2の高周波信号として出力する第2の出力端子7Bとを有している。第1のスイッチ素子6A及び第2のスイッチ素子のbうちの一方がオン状態とされる。

(もっと読む)

自動調整回路

【課題】直流電圧レベルの変動に影響されることなくgm−Cフィルタ回路の出力信号を安定にする自動調整回路を提供する

【解決手段】gm−Cフィルタ回路により構成されるフィルタ回路を調整する自動調整回路であって、基準クロック信号を増幅する第1増幅回路と、第1増幅回路により増幅される信号の直流電圧レベル変動を抑制する第1コモンモードフィードバック回路と、第1コモンモードフィードバック回路の出力信号を増幅する第2増幅回路と、第1コモンモードフィードバック回路の出力の位相を90度シフトさせる移相回路と、第2増幅回路の出力と、移相回路の出力とを乗算する乗算回路と、乗算回路の出力を平滑する積分回路と、調整回路の出力を増幅する第3増幅回路と、を具備する自動調整回路である。

(もっと読む)

抵抗器およびキャパシタをチューンするための方法および装置

集積回路における抵抗器(410)およびキャパシタ(420)についての2ステップチューニングプロセスが説明されている。チューニングプロセスの第1のステップにおいては、オンチップ調節可能な抵抗器(410)は、チューンされた抵抗器を得るために、外部抵抗器に基づいてチューンされる。チューンされた抵抗器の値は、外部抵抗器と調節可能な抵抗器(410)の設計とによって決定された、ターゲットパーセンテージ内で、正確である。第2のステップにおいては、調節可能なキャパシタ(420)は、正確な値を有しているチューンされたキャパシタを得るために、チューンされた抵抗器の値と正確なクロックとに基づいて、チューンされる。調節可能なキャパシタ(420)は、チューンされた抵抗器およびチューンキャパシタについてのRC時間定数が、正確クロックと調節可能なキャパシタ(420)の設計とによって決定されるターゲットパーセンテージ内に正確であるように、チューンされることができる。集積回路上の他の回路の抵抗器およびキャパシタは、チューンされた抵抗器およびチューンされたキャパシタ、それぞれに基づいて、調節されることができる。  (もっと読む)

(もっと読む)

差動増幅器、電圧制御発振器および電圧制御発振器動作方法

【課題】 マイクロ波周波数で動作し、低出力、低ノイズで高品質を達成できるCMOS差動増幅器を供給する。

【解決手段】 マイクロ波差動増幅器は、ソースが共通バイアス・ノードに接続され、ゲートが差入力信号を受信する入力ポートに接続され、さらにドレインが差出力信号を供給するための出力ポートに接続される第1および第2のMOSデバイスから構成される。各デバイスのミラー・キャパシタは入力と出力ポートの間に必要なフィードバックを供給し、差出力信号の位相を差入力信号の位相と所定の周波数で45゜シフトさせる。整合負荷と対応バイアス電流を用いて、NMOSデバイスの動作点は各転送特性の線形領域に維持される。ジャイレータ構成中に4つの差動増幅器を内蔵するVCOは、所定の周波数で発振し、8つの出力信号を持つ。

(もっと読む)

フィルタ回路

【課題】電源投入時の起動時間を短縮することが可能なフィルタ回路を提供する。

【解決手段】電源投入時には各スイッチSW1,SW2をオフ動作させてキャパシタCfcをオペアンプAMPから切り離すことにより、出力端子OUTの電圧を急峻に立ち上げ、電源投入時の起動時間を短縮させる。そして、出力端子OUTの電圧が完全に安定した時点で各トランジスタSW1,SW2をオン動作させる。すると、フィルタ回路10はキャパシタCfcに抵抗Rfcが並列接続された不完全積分回路を構成するため、キャパシタCfcおよび各抵抗Ra,Rfcによって規定されるフィルタ特性を確保できる。

(もっと読む)

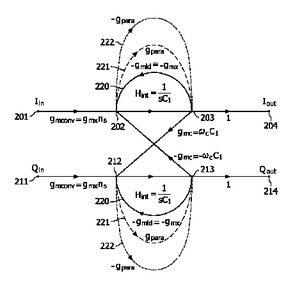

ラジオ受信機

信号有向グラフを用いてフィルタ内の寄生信号伝達を識別するステップと、補償経路をフィルタに追加して寄生信号伝達の影響を低減または解消するステップとを具えた方法を提供する。これに対応するフィルタを提供し、このフィルタは、1つ以上のフィルタ極を生成する複数の増幅段と、これらの増幅段の少なくとも1つに結合された少なくとも1つの構成部品であって、フィルタ内に寄生効果を生じさせる構成部品と、上記少なくとも1つの増幅段に補償電流を加えて、この寄生効果を低減または解消する手段とを具えている。さらにラジオ受信機を提供し、このラジオ受信機は、同相及び直交信号を受信してフィルタ処理するフィルタと、フィルタ処理した同相及び直交信号の一方を受信して増幅する増幅器と、フィルタ処理して増幅した同相または直交信号をこの増幅器から受信し、上記同相または直交信号の他方を、上記フィルタ処理して増幅した信号から再生する手段とを具えている。  (もっと読む)

(もっと読む)

段間フィルタとこれを用いた無線機

【課題】インダクタを削除して占有面積を減らし半導体集積回路を小型化し、かつインダクタの削除による相互変調歪を劣化させることなく確保する。

【解決手段】第1の電子回路1および第2の電子回路2の入出力端子を接続した端子間に容量5の一端を接続し、この容量5の他端をアクティブインダクタ回路10の入力端に接続し、また出力端をGNDに接続する。このアクティブインダクタ回路10は、容量5の他端にバイポーラトランジスタ6のエミッタ端子、ベース端子に抵抗7の一端を接続し、またコレクタ端子と抵抗7の他端を電源に接続して、さらにエミッタ端子には、他端をGNDに接続した電流源8の一端を接続し構成する。バイポーラトランジスタ6等の能動素子と容量5等の受動素子を組み合わせてインダクタ相当の特性を持つ構成として、相互変調歪を劣化させる高調波成分をバンドリジェクションすることで相互変調歪を確保する。

(もっと読む)

可変トランスコンダクタ

【課題】トランスコンダクタンスの可変域を拡大又は維持しつつ出力端子の寄生容量を低減する。

【解決手段】2つの入力回路10,60が平方根圧縮回路20と電圧電流変換回路30とを共有するように構成する。また、電圧電流変換回路30を構成する差動MOSトランジスタM5及びM6の出力部において、固定バイアス電流Ibiasを電流源41,42で引き抜き、同時にM5及びM6の可変駆動電流と同一の可変バイアス電流Ibを電流源51,52から供給することで、出力バイアス回路40の電流が固定バイアス電流Ibiasと常に等しくなるようにする。更に、電圧電流変換回路30と出力バイアス回路40との間に、カスコード接続のMOSトランジスタM9及びM10からなる電流バッファ50を挿入する。

(もっと読む)

遅延回路及びリングオッシレータ型電圧制御発振回路

【課題】遅延回路1を構成するトランジスタ素子のばらつきの影響を低減し、少ない余裕で発振周波数可変範囲を確保する。

【解決手段】第2のトランジスタQ2に対してソース同士、ドレイン同士が接続された第3のトランジスタ素子Q3と、前記第3のトランジスタ素子Q3のゲートに接続され、当該ゲートにトランジスタ素子の特性のバラツキを補正するためのバイアス電圧を印加するためのバイアス生成回路10とを備える。前記バイアス生成回路10は、遅延回路1と同一の基板から形成された少なくとも1つのトランジスタ素子Q6を備え、このトランジスタ素子Q6を用いて前記バイアス電圧を生成する。

(もっと読む)

スプリッタ回路

【課題】スプリッタ回路の集積回路化を図り、実装面積を縮小すること。

【解決手段】このスプリッタ回路10は、それぞれのコレクタが直流電源14に接続され、それぞれのベースに共通のRF信号が供給される複数のトランジスタ11〜13と、一端がそれぞれ接地され他端が各々対応する前記各トランジスタ11〜13のエミッタに接続された複数の第一の抵抗16〜18とを備える。複数のトランジスタ11〜13のエミッタにそれぞれ現れた信号を前記各第一の抵抗16〜18の他端から出力信号として取り出す。

(もっと読む)

フィルタ自動調整回路およびフィルタ調整方法ならびに携帯電話システム

【課題】特性周波数の調整機能を有するフィルタに対して、高い調整精度を持ちかつ容易に低消費電流化を実現したバラツキ補正を可能にし、フィルタ調整誤差を確実に抑えることができるフィルタ自動調整回路およびフィルタ調整方法ならびに携帯電話システムを提供する。

【解決手段】基準フィルタ103のバラツキを検出するために、位相差検出器104により、基準フィルタ103における前後の位相差をカウンタ106にてカウントする際に、一種類の基準信号でなく、位相器110で作成した複数個の基準信号を用いてカウントし、このカウント結果から得られる信号を、主フィルタ109の制御信号116(1)〜116(n)としてレジスタ108に保持することにより、主フィルタ103のバラツキ調整後は、フィルタ調整に関する部材のすべての動作を停止させる。

(もっと読む)

半導体集積回路

【課題】外部寄生抵抗の抵抗値に応じて、プログラマブルに外部から終端抵抗の抵抗値を調整し、高精度のインピーダンス整合を実施することが可能な半導体集積回路を提供する。

【解決手段】本発明に係る半導体集積回路100は、電源Vccに接続された電流回路3、この電流回路3と接地との間に接続され電流回路3が出力する主電流Iが入力される可変抵抗4、この可変抵抗4の電位と第1の基準電位Vref1とを比較し信号を出力するコンパレータ回路5、および、コンパレータ回路5の出力信号に基づいて可変抵抗4の抵抗値を制御する制御回路6、を有する終端抵抗調整回路1と、電源Vccと可変抵抗4との間に接続され、終端抵抗と伝送線路との間の外部寄生抵抗の抵抗値に応じた外部信号Sに基づいて可変抵抗4に付加電流Iadを出力する付加電流調整回路2と、を備える。

(もっと読む)

バイアス電圧供給回路

【課題】全体のレイアウト面積を抑制でき、アナログ回路を正しく動作させることができるバイアス電圧供給回路を提供する。

【解決手段】バイアス電圧供給回路100は、アナログ回路ACの信号ラインSL1にバイアス電圧Vbを印加するバイアス電圧供給回路であって、基準電圧ライン20と、抵抗生成部130と、抵抗変化抑制部140とを備える。基準電圧ライン20には、第1基準電圧Vbが供給されている。抵抗生成部130は、信号ラインSL1と基準電圧ライン20とに接続されている。抵抗生成部130は、トランジスタを用いて抵抗を生成する。抵抗変化抑制部140は、抵抗生成部130の抵抗R130の値の変化を抑制する。

(もっと読む)

トランスコンダクタ、積分器及びフィルタ回路

【課題】完全差動型のトランスコンダクタについて、差動出力の同相動作点を安定させ、さらに、消費電力及びチップ面積を低減し、ノイズ特性を向上する。

【解決手段】差動電圧信号を受け、差動電流信号を出力するトランスコンダクタとして、差動電圧信号を受け、シングルエンドの電流信号を出力する二つのトランスコンダクタ(10+、10-)を備えたものとする。ここで、二つのトランスコンダクタ(10+、10-)の一方の反転入力端と他方の非反転入力端とは互いに接続されている。本トランスコンダクタは、二つのトランスコンダクタ(10+、10-)のそれぞれから出力された電流信号を差動電流信号として出力する。

(もっと読む)

能動フィルタ回路

【課題】回路規模を増大させることなく、フィルタ回路を所望の特性に安定化させる

【解決手段】能動フィルタ部14は、電流制御部30と、第1Gm−Cフィルタ部32と、後段回路34と、を含む。電流制御部30は、中央制御部20から出力された信号を入力として、第1Gm−Cフィルタ部32に対し、それぞれのトランスコンダクタンスアンプに対応した、Gm値を調整するための調整電流を出力する。後段回路34は、トランスコンダクタンスアンプなどの能動素子によって構成される負荷容量を含む。第1Gm−Cフィルタ部32は、複数のトランスコンダクタンスアンプと、トランスコンダクタンスアンプのGm値を制御する制御部とから構成され、第1フィルタ信号選択部12から出力された信号の帯域を制限して後段回路34に出力する。

(もっと読む)

能動フィルタ回路、フィルタ調整方法、および、それらを用いた通信装置

【課題】回路規模を増大させることなく、フィルタ回路を所望の特性に安定化させる

【解決手段】能動フィルタ部14は、電流制御部30と、第1Gm−Cフィルタ部32と、後段回路34と、を含む。電流制御部30は、中央制御部20から出力された信号を入力として、第1Gm−Cフィルタ部32に対し、それぞれのトランスコンダクタンスアンプに対応した、Gm値を調整するための調整電流を出力する。後段回路34は、トランスコンダクタンスアンプなどの能動素子によって構成される負荷容量を含む。第1Gm−Cフィルタ部32は、複数のトランスコンダクタンスアンプと、トランスコンダクタンスアンプのGm値を制御する制御部とから構成され、第1フィルタ信号選択部12から出力された信号の帯域を制限して後段回路34に出力する。

(もっと読む)

出力装置および半導体レーザ変調駆動装置および画像形成装置

【課題】 信号伝送速度が高速化する場合にも、インピーダンス整合を正確にとることができ、その場合に、回路の大規模化等を有効に防止する。

【解決手段】 この出力装置1は、スイッチングによって出力信号を生成して伝送路(出力ノード)に出力するスイッチング部2と、出力装置1の出力インピーダンスを伝送路のインピーダンスに合うように調整するために設けられているインピーダンス整合部3と、出力装置1の出力インピーダンスを伝送路のインピーダンスに合うようにインピーダンス整合部3を設定する制御手段4とを有し、前記インピーダンス整合部3は複数のトランジスタ部により構成されている。

(もっと読む)

アッテネータ

【課題】従来のアッテネータは、スイッチを切り替える場合にオフセットの変動によるノイズが発生する問題があった。

【解決手段】本発明にかかるアッテネータは、制御信号に応じて入力信号と所定の電位とのいずれか一方を出力する複数のスイッチSW1〜SW4を有するスイッチ群20と、スイッチSW1〜SW4の出力受けて所定の出力抵抗値で出力する複数のバッファ回路31〜34を備えたバッファ回路群30と、所定の出力抵抗値に実質的に等しい又は1/2倍である抵抗値を有する2種類の負荷回路からなる直列回路において前記バッファ回路の出力を受ける負荷回路の接続点(タップ)を設けた負荷回路群40とを、有するものである。

(もっと読む)

共振回路

本発明の実施形態は共振回路に関し、特に、広い周波数範囲に応答するRFID(radio frequency identification)における共振回路に関するが、これに限定しない。可制御電気共振器は、共振回路を構成するために第1キャパシタに結合されたインダクタを備え、前記可制御電気共振器は、可制御素子と、前記可制御素子によって前記第1キャパシタの一端から他端に制御可能に結合される第2キャパシタと、前記第1および第2キャパシタの合計の実効静電容量が前記可制御電気共振器における振動信号のデューティサイクルによって変化するように前記可制御素子を制御する制御装置とをさらに備える。  (もっと読む)

(もっと読む)

ボルテージレギュレータ

【課題】非常に長い間、出力電圧のオーバーシュートが生じる状況でも当該オーバーシュートを抑制可能とすると共に、容量の大きなコンデンサの付加を不要とし、省スペースを実現する。

【解決手段】誤差増幅器を具備したボルテージレギュレータに、出力電圧のオーバーシュートを検出する第1の手段(誤差増幅器(2)1a)と、出力電圧のオーバーシュートを検出している間、誤差増幅器に流す電流を増加させる第2の手段(PチャネルトランジスタM19、NチャネルトランジスタM12)とを設ける。

(もっと読む)

141 - 160 / 224

[ Back to top ]