Fターム[5J098AA03]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | 半導体素子 (443) | FET (224)

Fターム[5J098AA03]に分類される特許

101 - 120 / 224

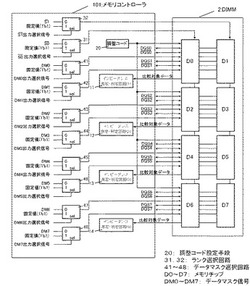

インピーダンス調整回路

【課題】 DIMMに実装されているSDRAMのOCDインピーダンス測定・調整が短時間で実行でき、設計が容易なインピーダンス調整回路を提供する。

【解決手段】 調整コードに対応してインピーダンスが可変の出力ドライバを有する、複数のメモリチップD0〜D7をランク選択信号とデータマスク信号の組合せにより選択して、インピーダンスの測定及び調整を行うインピーダンス調整回路において、異なるランクのメモリチップD0〜D7にランク選択信号をそれぞれ出力する複数のランク選択回路31,32と、ランクごとにメモリチップを選択するデータマスク信号をそれぞれ出力する複数のデータマスク選択回路41〜48とを備えたことを特徴とする。

(もっと読む)

フィルタ回路

【課題】高精度かつ小面積なフィルタ回路を提供する。

【解決手段】例えば、バンドパスフィルタBPFと、BPFの周波数特性(中心周波数)を設定する制御部とを設ける。制御部は、基準周波数信号Frefと、Frefから2次ローパスフィルタLPFSを介した信号とを位相比較し、その結果をコンデンサC3に蓄え、C3の電圧を電流に変換してLPFSおよびBPFに帰還する。この帰還ループによって、LPFSの遮断周波数はFrefに収束する。ここで、BPF内の可変抵抗回路RVa,RVbおよびLPFS内の可変抵抗回路は、MOSトランジスタからなる差動アンプ回路で構成され、この差動アンプ回路のテール電流に前述した帰還電流が用いられ、相互コンダクタンスに基づいて抵抗値が制御される。そして、このような可変抵抗回路を含むフィルタ回路全体をCMOSプロセスで形成する。

(もっと読む)

多入力多出力増幅器とこれを用いたアクティブインダクタ、フィルタ及び無線通信装置

【課題】対称3相信号のような対称多相信号を増幅できる多入力多出力の非反転増幅器を提供する。

【解決手段】和が一定のn(n≧3)個の入力電圧信号をそれぞれ受けるn個の外部入力端子11〜13と、n個の増幅ユニット31と、増幅されたn個の出力電圧信号をそれぞれ出力するn個の外部出力端子21〜22とを有し、増幅ユニットは増幅ユニット毎に異なる組み合わせのn−1個の端子と接続されるn−1個の内部入力端子311,312、内部入力端子からの入力電圧信号を電流信号に変換して出力するn−1個の電圧−電流変換器314,315、及び電圧−電流変換器314,315からの電流信号を加算した加算電流信号を出力電圧信号に変換して外部出力端子21〜23へ導く負荷Rを有する。

(もっと読む)

MOS抵抗制御装置、MOS減衰器、無線送信機

【課題】MOS減衰器としての可変特性を所望に合わせ込んでそのばらつきを吸収することが可能なMOS抵抗制御装置、これを用いる無線送信機を提供すること。

【解決手段】ソースが第1の基準電位に接続されたMOSトランジスタと、該MOSトランジスタのドレインと第2の基準電位との間に挿入・接続された第1の制御電流源と、第1、第2の入力端、および出力端を有し、該第1の入力端がMOSトランジスタのドレインと第1の制御電流源との接続ノードに接続され、該出力端がMOSトランジスタのゲートに接続されたオペアンプと、該オペアンプの第2の入力端に一端が接続されたインピーダンス素子と、該インピーダンス素子に一端の側から電流を入力する基準電流源と、インピーダンス素子に一端の側からさらに電流を入力する第2の制御電流源と、MOSトランジスタのドレインに電流を入力する第3の制御電流源とを具備する。

(もっと読む)

アクティブインダクタ回路、発振器、及び、フィルタ回路

【課題】 外部接続用の2端子の各入力インピーダンスが等しく差動回路に適用した場合の波形歪を抑制でき、小面積化、低消費電力化の図れるアクティブインダクタ回路を提供する。

【解決手段】 相互コンダクタンスの極性の異なる第1電圧制御電流源回路5A〜5Dと第2電圧制御電流源回路6A〜6Dの一方の入力と他方の出力、他方の入力と一方の出力

を互いに接続した能動回路1A〜1Dの4つを循環的に接続し、各能動回路の4つの接続点の対向する1対間にキャパシタ4を接続し、他の対向する1対を外部接続用の端子対Nx1,Nx2として構成する。

(もっと読む)

可変インピーダンス回路、それを用いた可変インピーダンスシステム、フィルタ回路、増幅器、通信システム

【課題】可変インピーダンス回路の歪を低減したい。

【解決手段】第1トランジスタM1は、差動入力信号の一方を受ける第1端子と、インピーダンスを変化させるための制御信号を受ける第2端子と、第2トランジスタと接続された第3端子と、基板に電位を供給するための第4端子とを含む。第2トランジスタM2は、差動入力信号の他方を受ける第5端子と、制御信号を受ける第6端子と、第1トランジスタと接続された第7端子と、基板に電位を供給するための第8端子とを含む。第3端子、第4端子、第7端子および第8端子が接続される。

(もっと読む)

キャパシタンス回路

【課題】外部からトランジスタの容量値を調整できる容量調整機能を有し、処理する信号の応答特性を適宜調整可能とし、成形波形の特性を一致させることが可能なキャパシタンス回路を提供する。

【解決手段】トランジスタを用いるキャパシタンス回路において、容量調整信号を受け付ける容量調整端子と、トランジスタのソース端子とドレイン端子とに接続されて、容量調整信号によりトランジスタの容量を調整する容量調整回路と、を具備する。

(もっと読む)

時定数回路

【課題】

抵抗およびコンデンサの数を増やすことなく時定数を詳細に設定でき、かつ、コンデンサの充電時の時定数と放電時の時定数とを別々に設定できる時定数回路を提供する。

【解決手段】

信号入力部1において、差動増幅器11に入力信号Vinが供給されるとき、コンデンサ2は、充電制御部3に入力される充電制御信号Vcおよび放電制御部4に入力される放電制御信号Vdの値に基づく時定数で充電される。

また、入力信号Vinが減少するとき、コンデンサ2は放電制御信号Vdの値に基づく時定数で放電する。

(もっと読む)

遅延回路

【課題】消費電力を低減し、かつ生成する遅延時間の誤差を縮小し得る遅延回路を提供する。

【解決手段】単位遅延時間のほぼ2倍の遅延時間を生成する複数の第一の遅延ユニットY1〜Y16と、単位遅延時間を生成する第二の遅延ユニットX1と、第一の遅延ユニットを直列に接続し、終段の第一の遅延ユニットY16に第二の遅延ユニットX1を接続することと、初段の第一の遅延ユニットY1に外部入力信号Dinを入力するとともに、各第一の遅延ユニットと第二の遅延ユニットには外部入力信号Dinを入力することと、第一の遅延ユニット及び第二の遅延ユニットは、前段の遅延ユニットの出力信号と外部入力信号のいずれかを遅延させて出力するスイッチ回路を備えることと、終段の第一の遅延ユニットY16の出力信号と第二の遅延ユニットX1の出力信号のいずれかを選択するセレクタ2とを備えた。

(もっと読む)

インピーダンス調整回路およびインピーダンス調整方法

【課題】半導体装置と外部抵抗の間の線路に存在する寄生抵抗分を特別の回路を設けることなく補正することのできるインピーダンス調整回路およびインピーダンス調整方法を得ること。

【解決手段】LSIケース201の外部には、ケースピンを介してインピーダンス設定用のクランプ抵抗208と、これと電位を比較するための第1および第2の参照電圧生成抵抗221、222が接続されている。第1および第2の参照電圧生成抵抗221、222の間には、LSI202内の折り返し線225を経由する形で他の線路と同一幅の2本ずつの線路の寄生抵抗分からなる抵抗回路224が設けられており、調整に悪影響となる他の線路の寄生抵抗分をキャンセルする。このため、コンパレータ211の比較結果を使用して制御回路205はインピーダンス調整用出力バッファ203を高精度に調整可能である。

(もっと読む)

フィルタ回路

【課題】LSIに形成されるGm-Cフィルタに使用される抵抗と容量の値が製造プロセスのばらつきにより変動した場合でも、Gm-Cフィルタのカットオフ周波数を所望通り自動的に校正し得るフィルタ回路を提供する。

【解決手段】マスタ回路20における抵抗と容量のプロセス変動分に応じて補正された電流を基準としてGmアンプG1、G2、G3のバイアス電流を変化させることにより、スレーブフィルタ回路10のカットオフ周波数を可変させる。

(もっと読む)

移相回路

【課題】低損失でかつ小型な移相回路を実現する。

【解決手段】一端が高周波信号入力端子1に接続され、かつ他端が高周波信号出力端子2に接続され、オン時に抵抗性を示し、オフ時に容量性を示す第1のFET3a、オン時に抵抗性を示し、オフ時に容量性を示す第2のFET3bと、第1のFETに並列接続された第1のスパイラルインダクタ4と、第2のFETに並列接続された第2のスパイラルインダクタ6と、第1のFETの一端に接続された第1のMIMキャパシタ7と、第1のFETの他端に接続された第2のMIMキャパシタ8と、第1及び第2のMIMキャパシタの他端同士と接続された第3のスパイラルインダクタ5とを備え、第2のFETは、一端を第3のスパイラルインダクタ5の他端に接続し、他端をスルーホール11に接続した。

(もっと読む)

補償部を備える信号変換器

【課題】補償部を含む信号変換器を提供する。

【解決手段】信号変換器は、信号変換部と補償部とを含む。信号変換部は、シングルエンド信号に応答して中間ノードに中間差動信号を発生させる。補償部は、中間差動信号の間の位相と振幅不整合エラーとを最小化させることによって、出力ノードに補償された差動信号を発生させる。補償部は、中間ノードと出力ノードとの間に対称的に形成されるトランジスタ対とキャパシタ対とを含む。本発明の実施形態による他の信号変換器は、特にRF受信器に有用に使用出来る。

(もっと読む)

イコライザ調整回路、イコライザ調整方法、及び電子機器

【課題】 調整用の信号として低周波から高周波までの周波数成分を含むステップ波を用い、それに対するイコライザの出力波形のオーバーシュートの有無を検出し、オーバーシュートがなくなるようにイコライザのゲインを調整することにより、イコライザ調整を効率よく行うこと。

【解決手段】 伝送信号を正極性信号L16Tと裏極性信号L16Cの差動信号として伝送路12に出力する出力ゲート11と、イコライザ13と、イコライザ13から出力される裏極性信号L18Cの電圧をコンデンサ33に保持させた状態で、出力ゲート11にステップ波を与え、イコライザ13の正極性信号L18Tの電圧をコンデンサ33に保持させた電圧と比較することによりオーバーシュートを検出し、オーバーシュートがなくなるようにイコライザ13のゲインを徐々に小さくするイコライザ調整回路20を有する。

(もっと読む)

利得制御フィルタ装置、利得制御複素フィルタ装置および受信装置

【課題】アクティブフィルタのSNを確保するために、フィルタ回路への入力信号レベルを一定にする利得制御機能を有する利得制御フィルタ装置を提供する。

【解決手段】反転入力端、非反転入力端、反転出力端および非反転出力端を有するアクティブフィルタ回路241と、アクティブフィルタ回路241の非反転入力端、反転入力端に至る第1および第2の入力路に挿入され第1の制御電圧によって抵抗値が制御される可変抵抗回路221とを備え、第1の制御電圧を変化させることによって利得を制御する。

(もっと読む)

遅延回路

【課題】電荷蓄積用キャパシタに蓄積された情報を破壊することなく読み出すことのできるスイッチト・キャパシタ型の遅延回路を提供する。

【解決手段】遅延セル11〜13は、書き込み信号Wが入力されたときに入力端子INへ入力される電流を取り込み、その取り込んだ電流の大きさに応じた電荷をキャパシタC1に蓄積し、そのキャパシタC1の出力電圧で電流源のNMOSトランジスタM1の出力電流の大きさを制御し、読み出し信号Rが入力されたときにその出力電流を出力する。書き込み制御用のシフトレジスタ2は、遅延セル11〜13へ入力する書き込み信号W1〜W3を制御し、遅延セル11〜13への電流の取り込みタイミングを1個ずつ遅延させる。読み出し制御用のシフトレジスタ3は、遅延セル11〜13へ入力する読み出し信号R1〜R3を制御し、電流の取り込み終了後の遅延セル11〜13からの電流の出力タイミングを制御する。

(もっと読む)

全差動増幅器

【課題】低電源電圧で動作可能で、同相信号抑圧機能を備える全差動増幅器の実現。

【解決手段】1段構成の反転増幅器41-48,41'-48'で構成され、入力側の同相信号をフィードフォワード手段によって打ち消すように構成された第1の全差動増幅器200(100,101)と、1段構成の反転増幅器51-58で構成され、出力側の同相信号をフィードバック手段によって打ち消すように構成された第2の全差動増幅器201(102)と、を備え、第1の全差動増幅器200の出力が、第2の全差動増幅器201の入力に接続されている。

(もっと読む)

バンドパスフィルタを同調させるための装置、及び方法

【課題】バンドパスフィルタを同調させるための装置、及び方法を提供する。

【解決手段】チューナブルバンドパスフィルタは、バンドパスフィルタと、フィルタに接続された複数のスイッチとを備える。バンドパスフィルタは、複数のトランスコンダクタと複数のコンデンサとを備える。チューナブルバンドパスフィルタは、複素バンドパスフィルタ、または、複素バンドパスフィルタの中心周波数を同調させるための同調装置として設定され得る。同調装置は、少なくとも1つの同調用積分器、及び比較器を備える。同調用積分器は、少なくとも1つのトランスコンダクタ、及びコンデンサを備える。トランスコンダクタは、複数のスイッチによって複数のトランスコンダクタの中から選択され、コンデンサは、複数のスイッチによって複数のコンデンサの中から選択される。選択されたトランスコンダクタ及びコンデンサは、バンドパスフィルタの中心周波数を決定する。

(もっと読む)

MOS抵抗制御装置、MOS減衰器

【課題】MOS抵抗の制御精度を向上することができるMOS抵抗制御装置およびこれを利用したMOS減衰器を提供すること。

【解決手段】ソースドレインが直列に接続され、該直列に接続されたソースドレインのうち最も外側のソースが第1の基準電位に接続された2以上のMOSトランジスタと、この2以上のMOSトランジスタの直列に接続されたソースドレインのうち最も外側のドレインと第2の基準電位との間に挿入・接続された電流源と、第1、第2の入力端、および出力端を有し、該第1の入力端に第3の基準電位が供給され、該第2の入力端が最も外側のドレインと第2の基準電位との接続ノードに接続され、該出力端が2以上のMOSトランジスタのゲートそれぞれに接続されたオペアンプとを具備する。

(もっと読む)

バンドパスフィルタ回路、バンドエリミネートフィルタ回路、並びに赤外線信号処理回路

【課題】Q値等の定数の調整が可能なバンドパスフィルタ回路を実現する。

【解決手段】本発明に係るバンドパスフィルタ回路10は、トランスコンダクタンスアンプ回路1〜3と、トランスコンダクタンスアンプ回路1の差動出力の直流電圧レベルが所定レベルになるように、トランスコンダクタンスアンプ回路1に第1制御信号を出力するコモンモードフィードバック回路4と、トランスコンダクタンスアンプ回路2の差動出力の直流電圧レベルが所定レベルになるように、トランスコンダクタンスアンプ回路2に第2制御信号を出力するコモンモードフィードバック回路5と、コンデンサC1〜C3とを備え、図1に示すような接続関係を有することで、上記Q値等の定数の調整が可能なバンドパスフィルタ回路を実現する。

(もっと読む)

101 - 120 / 224

[ Back to top ]