Fターム[5J098AA03]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | 半導体素子 (443) | FET (224)

Fターム[5J098AA03]に分類される特許

21 - 40 / 224

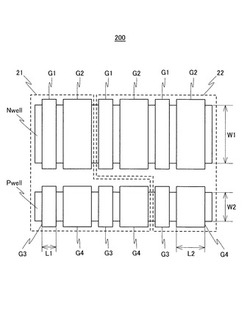

デカップリング回路及び半導体集積回路

【課題】容量値の切り換えが可能なデカップリング回路を提供すること。

【解決手段】本発明は、インバータ21を有する。インバータ21は、ゲート電極G1を有するi(iは1以上の整数)個のPMOSトランジスタ及びゲート電極G2を有するj(jは0以上の整数)個のPMOSトランジスタを有する。また、インバータ21は、ゲート電極G3を有するm(mは1以上の整数)個のNMOSトランジスタ及びゲート電極G2を有するn(nは0以上の整数)個のNMOSトランジスタを有する。ゲート電極G1〜G4は、インバータ21の入力端と接続される。ゲート電極G1及びG2の合計面積は、ゲート電極G3及びG4の合計面積と異なる。

(もっと読む)

減衰器

【課題】減衰量の周波数依存性を改善することができる減衰器を提供すること。

【解決手段】減衰器10は、FET11〜13、インダクタ14及び15、抵抗16、入力端子17、出力端子18を備え、入力端子17には、FET11のドレイン電極と、FET12のドレイン電極と、インダクタ14の一方端とが接続され、出力端子18には、FET11のソース電極と、FET13のドレイン電極と、インダクタ15の一方端とが接続され、FET11のドレイン電極とソース電極との間にインダクタ14と、抵抗16と、インダクタ15とが直列に接続された構成を有する。

(もっと読む)

フィルタ回路

【課題】フィルタ回路の中心周波数を調整する機能を備えたフィルタ回路を提供する。

【解決手段】入力信号とフィードバック信号(信号Vf)の加算信号を出力するカプラー109、加算信号を増幅した増幅信号を生成するAGC回路110、増幅信号の位相をシフトさせて信号Vfを生成する移相器111を備えたフィルタコア部102と、基準信号(信号Vr)を取得する基準信号生成部119、信号Vr、信号Vfの振幅を比較する振幅比較回路101、比較の結果に基づいてAGC回路110の増幅率を制御するゲイン制御電圧生成部108、信号Vrの位相と信号Vfの位相とを比較する移相比較回路103、比較結果に基づいて移相器111の位相のシフト量を制御する移相器制御電圧生成部117によってフィルタ回路を構成し、増幅率、シフト量が制御される間、カプラー109には信号Vfに代えて基準信号が入力される。

(もっと読む)

再帰型フィルタ回路

【課題】再帰フィルタ回路のエミッタフォロア回路の数を低減し、回路規模が小さい再帰型フィルタ回路を提供する。

【解決手段】バイポーラトランジスタ(Tr)101を流れる電流Iinとフィードバック電流Ifbとを加算して電流Iを生成するノードB、電流Iをテール電流とし、ゲインを変更する制御信号が入力されるバイポーラTr106及びバイポーラTr103を含む差動対100、バイポーラTr106に流れる電流を電圧に変換する抵抗素子105を含む可変ゲイン増幅部、変換後の電圧を増幅して出力信号を生成するバイポーラTr113を含む出力部115、可変容量素子104を含むハイパス部、ハイパス部から出力された信号をバッファリングする回路114、バッファリングされた信号を、可変容量素子109を介して周波数帯域制限するローパス部を含む移相部によって再帰型フィルタを構成する。

(もっと読む)

可変利得減衰器

【課題】特性劣化を引き起こす容量結合をしないで次段増幅器と接続でき、非常に広い周波数範囲に渡って同様の特性で、入力される高周波信号の利得を適切に減衰させて次段増幅器に伝達できる可変利得減衰器を提供すること。

【解決手段】高周波信号を入力するための入力ポート18と、高周波信号を出力するための出力ポート19と、外部からバイアス電圧を印加するためのバイアスポート20と、入力ポートと出力ポートとの間に直列に接続され、それぞれ同等の制御電圧により利得が制御されるMOSトランジスタ10,11と、MOSトランジスタ10,11の直列接続端とグランドとの間に接続され、MOSトランジスタ10,11に適用する制御電圧とは逆特性の制御電圧によって利得が制御されるMOSトランジスタ12とを備え、3つのMOSトランジスタの各バックゲート端子は共通にバイアスポートに接続されている。

(もっと読む)

スイッチトキャパシタフィルタ及びスイッチトキャパシタフィルタの制御方法

【課題】簡易な構成により雑音を低減することができるスイッチトキャパシタフィルタ及びその制御方法を提供すること。

【解決手段】本発明では、演算増幅器AMPの反転入力は積分キャパシタC0の一端と、出力は積分キャパシタC0他端と接続される。スイッチトキャパシタは第1〜3の順に接続状態が移行する。第1の接続状態では、第1の端子は入力信号と、第2の端子は固定電圧と接続される。第2の接続状態では、第1の端子は固定電圧と、第2の端子は演算増幅器AMPの反転入力と接続される。第3の接続状態では、第1の端子は演算増幅器AMPの出力と、第2の端子は演算増幅器AMPの反転入力と接続される。第2及び第3の接続状態のスイッチトキャパシタが各1個以上存在する場合の第2の接続状態のスイッチトキャパシタの個数は常に同じであり、第3の接続状態のスイッチトキャパシタの個数も常に同じである。

(もっと読む)

高インピーダンス回路、フィルタ回路及び増幅回路

【課題】従来技術の高インピーダンス回路は、温度変化等の影響を受けて、高いインピーダンスを維持することができないという問題があった。

【解決手段】本発明にかかる高インピーダンス回路は、ダイオード接続されたトランジスタ21,22を備え、トランジスタ21のバックゲートとトランジスタ22のソースとが接続され、トランジスタ22のバックゲートとトランジスタ21のソースとが接続される。このような回路構成により、温度変化等の影響を抑え、高いインピーダンスを維持することができる。

(もっと読む)

可変減衰器

【課題】 従来の可変減衰器では、高周波信号を損失少なく通過させる基準状態と、所望の減衰量を得る減衰状態との間で、通過位相差を生じてしまうという課題があった。

【解決手段】 入出力間FET3と並列、定位相可変減衰器4と直列に位相補正用FET5を設置することで、入出力間FET3がオン状態のときは位相補正用FET5をオフ状態とし、入出力間FET3がオフ状態のときは位相補正用FET5をオン状態とすることによって、基準状態と減衰状態との間で通過位相を等しくすることができる。

(もっと読む)

gm−Cフィルタの周波数補正方法と該方法を使うことができる装置

【課題】gm−Cフィルタの周波数補正方法を提供する。

【解決手段】周波数補正方法は、周波数補正回路が、gm−Cオシレータから出力され、工程変化を表わすオシレーション信号の周波数と基準コードとによって、gm−Cフィルタのカットオフ周波数を調節することができる補正コードを生成する段階と、周波数補正回路が生成された補正コードが、基準コードの範囲内に属するか否かを判断する段階と、周波数補正回路が、判断結果によって生成された補正コードをgm−Cフィルタに出力するか、またはgm−Cオシレータのトランスコンダクタンスとgm−Cフィルタのトランスコンダクタンスとを調節するための可変電流を生成する段階と、を含む。

(もっと読む)

遅延回路及び電圧制御発振回路

【課題】電源ノイズにより遅延時間が影響を受けにくい遅延回路及び遅延回路を用いた電圧制御発振回路を提供する。

【解決手段】第1及び第2の電源端子と一対の差動信号入力端子と一対の差動信号出力端子とを備え、一対の差動信号入力端子から入力した信号を遅延させて一対の差動信号出力端子から出力する遅延部と、電流制御端子により制御された電源電流を遅延部の第1の電源端子と第2の電源端子との間に流すように制御する電流制御部と、第1及び第2の電源端子の電圧が一定の電圧になるように制御する電圧制御部と、を備える。

(もっと読む)

電圧制御発振回路

【課題】電圧制御発振回路の回路規模の増大を抑制する。

【解決手段】電圧制御発振回路は、発振信号を増幅する発振アンプ部32と、発振信号の発振周波数を制御するLC共振部33と、負性抵抗成分を有する負性抵抗部34と、を備える。LC共振部33は、ループ状に接続されたgmセル25,26と、ループ上のノードに一端が接続された容量28〜31と、を有し、gmセル25,26と容量28,29とに基づくインダクタンス値と、容量30,31の容量値と、に基づいて発振周波数を制御する。

(もっと読む)

可変抵抗制御回路及び可変抵抗器

【課題】抵抗を広い範囲で変化させることができる可変抵抗制御回路及び可変抵抗器を提供すること

【解決手段】本発明にかかる可変抵抗制御回路は、電源10と、電源10よりも低い電位を有する電源11との間に設けられ、電源10と接続される抵抗21と、電源10と、電源11との間に設けられ、前記抵抗21と直列に接続されるMOSトランジスタ31と、電源10と、電源11との間に設けられ、前記MOSトランジスタ31と直列に接続されるMOSトランジスタ32と、抵抗21とMOSトランジスタ31との節点における電圧と、制御電圧とに基づいて、MOSトランジスタ32にゲート電圧を出力するオペアンプ41とを備え、オペアンプ41は、ゲート電圧に基づいて抵抗値が制御される外部の可変抵抗に対してゲート電圧を出力するものである。

(もっと読む)

フィルタ回路

【課題】高速に動作することが可能であり、周波数特性制御するためのフィルタ制御信号生成回路が小規模でしかも設計に要する時間が短時間で済むようなフィルタ回路を提供する。

【解決手段】Gm−Cフィルタのフィルタ制御信号生成回路を、MOSトランジスタ32、MOSトランジスタ32とゲート同士が接続されるMOSトランジスタ33、MOSトランジスタ32とドレイン同士が接続されるMOSトランジスタ30、ドレインとゲートが接続され、MOSトランジスタ30とゲート同士が接続され、MOSトランジスタ33とドレイン同士が接続されるMOSトランジスタ31、MOSトランジスタ30〜33のうちの1つのソースに接続される抵抗素子34によって構成し、MOSトランジスタ33,30のドレインに接続される出力端子35または出力端子36からフィルタ制御信号を出力させる。

(もっと読む)

ローパスフィルタ設計

高い品質係数(Q)を有するローパスフィルタリングのための手法。 例示的な実施形態では、入力電流は第1のトランジスタのドレインに接続される。 1のトランジスタのドレインとゲートとは抵抗器R1によって一緒に結合され、そして、ドレインは第1キャパシタC1によって基準電圧に結合される。ゲートは第2のキャパシタC2により、基準圧に結合される。ゲートはさらに第2のトランジスタのゲートに結合され、出力電流が第2のトランジスタのドレインに接続される。別の例示的な実施形態では、さらに受動素子が奇数次のローパス伝達特性を発生するために結合されることができる。 複数のフィルタは、任意のオーダーを有するフィルタを合成するために、直列にカスケード接続することができる。  (もっと読む)

(もっと読む)

時定数回路、スイッチ回路、DC/DCコンバータ及び表示装置

【課題】単調に減衰するだけの出力電圧特性に比べて、急峻に減衰した後に緩やかに減衰する出力電圧特性が得られる時定数回路等を提供する。

【解決手段】時定数回路10は、抵抗素子111と容量素子121との並列回路131,…が第一の端子14と第二の端子15との間に複数直列に接続されて成る直並列回路16と、第二の端子15に接続された第三の端子17と第四の端子18との間に接続された分圧用抵抗素子19と、を備えている。並列回路131は抵抗素子111と容量素子121とから成り、並列回路132は抵抗素子112と容量素子122とから成り、・・・、並列回路13nは抵抗素子11nと容量素子12nとから成る。nは、並列回路131〜13nの数であり、2以上の整数である。

(もっと読む)

回路公差を調節するための回路と方法

【課題】周波数に敏感な回路のための周波数応答調節器、及び回路の周波数応答を調節する方法を提供する。

【解決手段】周波数に敏感な回路の充電状態を第1の電圧として測定し出力する時定数センサと、第1の電圧をサンプルし、第1の電圧を変換して得られる結果である第2の電圧を出力する変換器と、トリミング要素アレイと、トリミング要素アレイから少なくとも1つのトリミング要素を選択するために第2の電圧を利用するセレクタとを含んでいる。この方法は、回路の時定数を感知することと、この感知を第1の電圧として出力することと、第1の電圧を、固定された間隔にわたってサンプルすることと、サンプルした第1の電圧を、第2の電圧に変換することと、第2の電圧を使ってトリミング要素アレイから、少なくとも1つのトリミング要素を選択する。

(もっと読む)

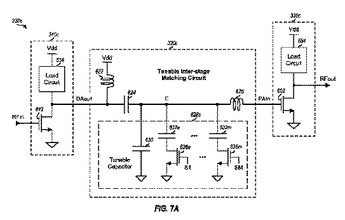

デジタルのチューナブル段間整合回路

性能を改善できるチューナブル段間整合回路について説明する。例示的な設計では、装置は、第1の能動回路(たとえば、ドライバ増幅器)と、第2の能動回路(たとえば、電力増幅器)と、第1の能動回路と第2の能動回路の間に接続されたチューナブル段間整合回路とを含む。このチューナブル段間整合回路は、第1の能動回路と第2の能動回路の間のインピーダンス整合を調整するために個別のステップで変化できるチューナブルキャパシタを含む。例示的な設計では、このチューナブルキャパシタは、(i)並列に接続された複数のキャパシタと、(ii)この複数のキャパシタに対してキャパシタごとに1つ接続された複数のスイッチとを含む。各スイッチは、関連するキャパシタを選択するためにオンにされるか、または関連するキャパシタの選択を解除するためにオフにされることができる。チューナブルキャパシタは、複数のキャパシタと並列に接続された固定キャパシタをさらに含むことができる。  (もっと読む)

(もっと読む)

フィルタ回路およびバイアス回路

【課題】回路面積の縮小を図りつつ、出力信号に含まれるオフセットを減少させることが可能なフィルタ回路を提供する。

【解決手段】フィルタ回路は、入力端子と出力端子との間に接続された第1のキャパシタと、前記出力端子と設定電位との間に接続されたバイアス回路と、を備え、前記バイアス回路は、前記出力端子と設定電位との間に接続された第1のMOSトランジスタと、前記第1のMOSトランジスタのゲートと前記出力端子との間に接続された第2のキャパシタと、前記第1のMOSトランジスタのゲートに一端が接続され、第1のバイアス電位が他端に印加された抵抗素子と、を有する。

(もっと読む)

可変利得増幅器及びそれを用いた移相器

【課題】 増幅素子の電流特性の非線形性を改善し、振幅設定精度を向上させた可変利得増幅器及びそれを用いた移相器を提供する。

【解決手段】 第2定電流源16からの電流を入力電流とし、この入力電流に比例した電流を第2カレントミラー回路17を介してエミッタ電流とする第7バイポーラトランジスタ18と、この第7バイポーラトランジスタ18の前記エミッタ電流に相応する第7バイポーラトランジスタ18のベース電流を入力電流とし、この入力電流に比例した電流を出力電流として第3バイポーラトランジスタ7及び第4バイポーラトランジスタ8のそれぞれのベースに入力する第3カレントミラー回路20とを備え、第3バイポーラトランジスタ7及び第4バイポーラトランジスタ8のそれぞれの入力電流に対する出力電流を線形とし、第2定電流源16からの電流に比例した利得を可変するようにした。

(もっと読む)

可変利得トランスコンダクタンスステージと同調可能な適応フィルタ

例示的な実施形態では、アナログフィルタ(400)を備えている通信デバイスを提供する。所望の値で、または、所望の範囲内でフィルタの極の位置を管理するために、デジタル信号プロセッサ(410)は、アナログフィルタの利得(420、440)と、フィルタの極の位置(430、480)とを同時に設定する。さらなる実施形態では、フィルタの、利得と極の位置とを同時に設定する方法論も与える。 (もっと読む)

21 - 40 / 224

[ Back to top ]