Fターム[5J098AA03]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | 半導体素子 (443) | FET (224)

Fターム[5J098AA03]に分類される特許

81 - 100 / 224

撮像装置及び当該装置におけるインピーダンス整合方法

【課題】 従来は、インピーダンスの整合を適切なタイミングで行うことにより、ノイズの影響を受けにくくする方法については考慮されていない。

【解決手段】 インピーダンス整合のための基準となる抵抗値を有する外部抵抗器260,261と、外部抵抗器が接続された端子の出力インピーダンスを、その外部抵抗器の抵抗値に対応して整合させるインピーダンス整合回路と、インピーダンス整合回路でインピーダンス整合を行わせるか否かを制御する制御信号280を生成する信号生成回路とを有する。

(もっと読む)

インピーダンス調整回路

【課題】回路規模を縮減するインピーダンス調整回路の提供。

【解決手段】外付抵抗3と、被調整抵抗5のレプリカをなすレプリカ抵抗4の抵抗値の大小を比較するコンパレータ2と、抵抗制御回路10と、を備え、抵抗制御回路10は、コンパレータ2での比較結果に基づきカウント値をアップ・ダウンしレプリカ抵抗への制御信号を出力するレプリカ抵抗制御カウンタ11と、被調整抵抗5へ与える制御信号を保持する被調整抵抗制御信号保持回路12と、前記カウンタの状態と、前記保持回路の出力を入力し、レプリカ抵抗制御カウンタ11のカウント状態と被調整抵抗制御信号保持回路12の出力(Y)との値の差(|X−Y|)が予め定められた所定範囲内にあるときは、被調整抵抗制御信号保持回路12の出力(Y)を被調整抵抗制御信号保持回路(12)への入力(Z)として供給する監視回路13を備えている。

(もっと読む)

低域ろ波回路

【課題】容量素子の小型化を図る低域ろ波回路(ループフィルタ)において、容量素子としてMOS容量を使用した場合の電圧依存によるPLL応答特性のばらつきと、MOS容量として薄膜ゲートトランジスタを使用した場合のゲートリーク電流によるジッタ特性の劣化を抑制する。

【解決手段】ループフィルタは、第1の容量素子31と、この容量素子31に直列に接続された抵抗素子32及び第2の容量素子33とを備える。前記第1の容量素子31の一端に接続された第1の入力端IN1に第1の電流(Ip/10)を与え、前記第1の容量素子31の他端に接続された第2の入力端IN2に第2の電流(Ip/10)を与えることにより、第1の容量素子31の小型化が図られる。前記抵抗素子32に直列に接続された可変電圧電源35は、電圧制御端子36から、第1の容量素子31の両端の印加電圧が一定になるように制御される。

(もっと読む)

誘導結合通信におけるインダクタンス補償方法及び装置

【課題】

本発明は、誘導結合(inductive coupling)送受信装置に関する。

【解決手段】

本発明の一実施例による誘導結合送受信装置は、データを送信及び/又は受信する誘導結合送受信器と、前記誘導結合送受信器に接続されたインダクタ(inductor)と、前記誘導結合送受信器及び前記インダクタに接続されて前記インダクタのインダクタンス(inductance)変化を補償する共振補償装置を含む。

(もっと読む)

広帯域分配器

【課題】出力端子に高電圧が入力された場合でもその影響をより少なくするとともに、広帯域なアイソレーション特性を持つ広帯域分配器を提供する。

【解決手段】入力端子1に一端が接続された第1の容量5と、前記第1の容量の他端にゲート端子が接続された第1のFET6と、前記第1のFETのドレイン端子と第1の容量の一端の間に接続された第1のフィードバック回路4と、第1のFETのソース端子6Sとグランド間に接続された第1のソース回路7と、第1のFETのドレイン端子と第1の出力端子2間に接続された第2の容量8とからなる第1の増幅器と、前記入力端子と第2の出力端子3間に接続され、第3の容量10、第2のFET11、第2のフィードバック回路9、第2のソース回路12及び第4の容量13からなる第2の増幅器と、第1のFETのソース6Sと第2のFETのソース11S間に接続されたアイソレーション回路14により構成される。

(もっと読む)

インピーダンス調整回路およびインピーダンス調整方法

【課題】インピーダンスを十分な精度で調整する。

【解決手段】一端を電源Vddに接続する抵抗11、12のそれぞれの他端をそれぞれ接続する端子13、14と、一端をスイッチ素子17を介して端子13に接続し他端を接地する可変抵抗素子19と、一端をスイッチ素子18を介して端子14に接続し他端を可変抵抗素子19の一端に接続する可変抵抗素子20とを備える。スイッチ素子17をオンとし、スイッチ素子18をオフとし、可変抵抗素子19の一端の電位が基準電圧となるように可変抵抗素子19の抵抗値を調整し、調整された可変抵抗素子19の抵抗値を維持して、スイッチ素子17をオフとし、スイッチ素子18をオンとし、可変抵抗素子20の一端の電位が基準電圧となるように可変抵抗素子20の抵抗値を調整する。

(もっと読む)

無限移相器及び移相器

【課題】ICチップ化が可能な無限移相器。

【解決手段】1.Aの無限移相器100においては、位相調整回路10に高周波が入力され、位相が0以上π/4未満の任意量で変化される。4相発生回路20では入力された高周波に対し、位相が一致した高周波、位相がπ/2、π及び3π/2進んだ高周波の4つが同時に生成される。ベクトル合成回路30では、入力された4つの高周波のうちの1つが利得調整回路40に出力されるか、位相がπ/2異なる2つの高周波のベクトル和が利得調整回路40に出力される。利得調整回路40では、ベクトル合成回路30に入力された4つの高周波のうちの1つが出力された場合の利得を基準として、ベクトル合成回路30に入力された4つの高周波のうちの2つの高周波の和が出力された場合の利得を1.5dB低くする。1.Bの無限移相器150は接続順序を替えたものである。

(もっと読む)

遅延素子、可変遅延線及び電圧制御発振器並びにそれを備えた表示装置及びシステム

【課題】温度が変化しても中心発振周波数が安定している電圧制御発振器等を、簡単な構成で提供する。

【解決手段】入力信号Viに遅延量τdを加えて出力信号Voとする遅延発生部11と、遅延τdを制御する遅延制御部12とを備えている。遅延制御部12は、遅延量τdを調節する第一の制御信号としての制御信号S1を出力する遅延調節回路13と、温度による特性変化を補償する第二の制御信号としての制御信号S2を出力する温度補償回路14とを有し、制御信号S1と制御信号S2とを合成して得た第三の制御信号としての制御信号S3を遅延発生部11へ出力することにより遅延量τdを制御する。遅延制御部12は、遅延調節回路13と温度補償回路14とを直列に接続することにより、制御信号S3を得ている。

(もっと読む)

集積回路コントローラ用の内部周波数補償回路

【課題】キャパシタの一端が接地電位へ接続される集積化に適した周波数補償回路を提供する。

【解決手段】集積回路内部の周波数補償回路であって、基準電圧を受ける第1入力31、入力電圧および入力電流を受ける第2入力32、第1出力電流を出力する第1出力33、および第2出力電流を出力する第2出力34、35、を含む相互コンダクタンス増幅器30と、前記相互コンダクタンス増幅器30の前記第2出力34へ接続される補償回路と、を有し、前記第1出力33は、前記第2入力32へ接続される、周波数補償回路である。

(もっと読む)

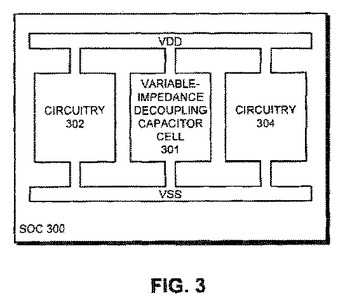

可変インピーダンスゲートデカップリングセル

本発明の実施形態は、電力レールと、接地レールとを含む、電力システム内のノイズを制御するシステムを提供する。システムは、電力レールと接地レールとの間でデカップリングコンデンサと直列に連結される、MOSトランジスタと、MOSトランジスタおよびデカップリングコンデンサと並列に電力レールに連結される、誘導パッケージング接続とを含む。MOSトランジスタ、デカップリングコンデンサ、および誘導パッケージング接続の組み合わせは、共振回路を形成する。動作中、システムは、電力レール上のVdd信号中にノイズが存在するかを判定する。Vdd信号中に存在するノイズに基づき、システムは、他の周波数でのスイッチングノイズの不必要な増加を引き起こすことなく、共振回路の関心周波数(ωinterest)付近の周波数範囲内のノイズを低減するように、MOSトランジスタのインピーダンスを調整する。  (もっと読む)

(もっと読む)

アッテネータ

【課題】アッテネータの減衰特性を電圧の値によって調整していたため、降圧回路などの電圧供給用回路が新たに必要となるアッテネータの回路規模が増大するとともに、熱雑音やショットノイズがアッテネータの出力信号に混入する。

【解決手段】直列接続された第1および第2回路と、これら第1および第2回路との間にシャント状に接続された第3回とを含むT型の二端子対網回路と、からなるアッテネータに対し、第1および第2回路の間に第3回路とは別にシャント容量を接続する。

(もっと読む)

チャージドメインフィルタ回路

【課題】低消費電力で動作可能であり、フィルタ特性がリコンフィギュアラブルである、チャージドメインフィルタ回路を提供すること。

【解決手段】所定の間隔でサンプリングされる第1の信号を出力する第1の信号出力手段と、第1の信号からサンプリング間隔のn倍(nは自然数)遅れて、かつ連続したタイミングでサンプリングされる第2の信号を出力する少なくとも1つの第2の信号出力手段と、第2の信号出力手段において時間的に後にサンプリングが行われる一つの第2の信号からサンプリング間隔のn倍遅れたタイミングでサンプリングされる第3の信号を出力する第3の信号出力手段と、第1の信号、第2の信号、および第3の信号を加算して出力する加算手段と、を含み、第1の信号出力手段と第2の信号出力手段とに備えられるサンプリングキャパシタの容量比を連続的にまたは離散的に可変とするチャージドメインフィルタ回路が提供される。

(もっと読む)

ノイズフィルタ回路、およびその方法、ならびに、サーマルヘッドドライバ、サーマルヘッド、電子機器、および印刷システム

【課題】 簡易な構造を有するノイズフィルタ回路等を提供する。

【解決手段】 ノイズフィルタ回路(10;60)は、入力信号(IN)を入力するラッチ回路(14;64)を備える。ラッチ回路(14;64)は、第1および第2の論理演算回路(たとえば、NAND回路)を含む。第1および第2のNAND回路のそれぞれにおいて、セット信号(S)またはリセット(R)信号を入力するP型トランジスタ(P1)の能力は、セット信号(S)またはリセット(R)信号を入力するN型トランジスタ(N1)の能力、および、このN型トランジスタ(N1)と直列に接続されるN型トランジスタ(N2)の能力(トータルな能力)より低い。ノイズフィルタ回路(10;60)は、ラッチ回路(14;64)からの出力信号(OUT(XQ;Q))を入力する波形整形回路(16)を、備えてもよい。

(もっと読む)

フィルタ回路及びこれを用いたテレビチューナ回路

【課題】広い周波数レンジでフィルタのQ値を所望の値に設定する。

【解決手段】フィルタ回路1は、入力電圧信号を電流信号に変換する可変トランスコンダクタンスgm1と、可変トランスコンダクタンスgm1の後段に結合されたRLCタンクと3aを備え、RLCタンク3aは、互いに並列に結合された可変キャパシタC1と可変抵抗R1とインダクタL1とを有し、可変キャパシタC1のキャパシタンス値を、フィルタ回路1の周波数特性を示す中心周波数またはカットオフ周波数の2乗に反比例して設定する周波数チューニング回路7と、可変抵抗R1の抵抗値を、可変トランスコンダクタンスgm1のトランスコンダクタンス値に反比例して設定するゲインチューニング回路8とをさらに備え、可変トランスコンダクタンスgm1のトランスコンダクタンス値は、中心周波数またはカットオフ周波数に依存した値に設定される。

(もっと読む)

精密集積位相ロック回路用ループ・フィルタ

【課題】基準精密抵抗器と、第1のFETのゲートが第2のFETのゲートに結合されている第1のFETおよび第2のFETと、第1のFETに接続されコンデンサ電圧を発生させるフィルタ・コンデンサとを含む位相ロック・ループ回路内のループ・フィルタが提供される。

【解決手段】コンデンサ電圧は、第1のFETのソース、第2のFETのソース、および仮想グラウンドとして機能する基準精密抵抗器の底部に印加される。フィルタ・コンデンサによって生成されるコンデンサ電圧は、第2のFETが集積精密抵抗器の特性を含むように、第2のFETのバイアス点を設定する。第2のFETによって生成される所定の電圧は、第1のFETのゲートに印加されて、第1のFETが集積精密抵抗器の特性を含むように、第1のFETのバイアス点を設定する。

(もっと読む)

可変アッテネータ回路

【課題】信号経路切替機能を有するアッテネータ回路において、信号伝搬における損失を抑制することが可能な可変アッテネータ回路を提供する

【解決手段】信号が入力される信号経路に並列に設けられ抵抗値制御端子に制御電圧が入力される可変抵抗VR1、信号経路と出力端子Sout1、Sout2との間に直列に接続された可変抵抗VR2a、VR2bを有するアッテネータ回路ATTN、制御電圧Vctrlが入力され制御電圧Vctrl2を出力するバイアス電圧発生部BVG、一端に制御電圧Vctrlが入力され、他端が可変抵抗VR2aの抵抗値制御端子に接続され出力経路切替信号PSaが与えられてオン/オフが制御される経路切替部PSa、一端に制御電圧Vctrlが入力され、他端が可変抵抗VR2bの抵抗値制御端子に接続され出力経路切替信号PSbが与えられてオン/オフが制御される経路切替部PSbを備えることを特徴とする。

(もっと読む)

可変減衰器及び無線通信装置

【課題】高周波で使用する1段当たりの可変減衰量が大きい可変減衰器を提供する。

【解決手段】可変減衰器は、ゲート、ドレイン、ソース、ボディを有するMOSFET12と、減衰量制御回路14と、温度補償回路21とを備える。減衰量制御回路14は、ゲート、及びドレイン、ソースに制御電圧を与える。温度補償回路21は、ボディに温度補償電圧を与える。入力端子、出力端子は、それぞれMOSFET12のドレイン、ソースに接続する構成をとる。温度補償回路21は、MOSFET12の動作温度に応じて、ボディに供給する電圧を制御して、ホディ電圧とゲート電圧との関係で入力端子及び出力端子間に流れる電流の抵抗値を調整する。

(もっと読む)

チューナブルインピーダンス整合回路

チューナブルインピーダンス回路は、コンデンサC1、C2、インダクタL1及び、インダクタL1と磁気的に結合するインダクタL2を備える。可変な位相と振幅を持つ、制御回路13からの制御電流Icontrolは、インダクタL2に流れる。インダクタL1のインピーダンスは、制御電流Icontrolの位相と振幅を変化させることによって、変化される。出力インピーダンスは、インピーダンス回路12aの有効インダクタンスと有効クオリティファクタを、RF PA11の出力電流IRFに対する制御電流Icontrolの位相と振幅によって、最適に設定することによって、最適なレベルに設定される。 (もっと読む)

温度補償バイアス回路、高周波増幅器及び高周波減衰器

【課題】負電圧で動作可能であり、かつ出力電圧の温度変化が大きな特性が得られる温度補償バイアス回路を提供する。

【解決手段】プラス側電圧印加端子3にドレイン端子が接続し、温度が高くなるにつれてドレイン電流が増加する傾向を示す閾値電圧Vth付近の電圧範囲のゲート−ソース間電圧Vgsが印加されるトランジスタ4と、一端がトランジスタ4のソース端子に接続し、他端が抵抗6の一端に接続するダイオード5と、一端が抵抗6の他端に接続すると共に、他端がマイナス側電圧印加端子1に接続し、トランジスタ4のゲート端子が抵抗6との接続部に接続する抵抗7と、ダイオード5と抵抗6との接続部に接続して出力電圧が取り出される出力電圧端子2とを備えた。

(もっと読む)

半導体集積回路

【課題】チップ占有面積が小さく低消費電力の広帯域RF信号処理回路を提供すること。

【解決手段】半導体集積回路は、第1制御端子101の第1制御信号Vc1により制御可能なキャパシタンスCRを有する第1キャパシタ1と、第2制御端子102の第2制御信号Vc2により制御可能なキャパシタンスCLを有する第2キャパシタ3を含み等価的にインダクタLをエミュレートするジャイレータ2、5とからなる共振回路を半導体チップに具備する。キャパシタンスCRとインダクタLは、並列共振回路を構成する。並列共振周波数を変更する際に、第1と第2のキャパシタ1、3のキャパシタンスを協調的に変更する。並列共振回路は増幅素子Q1の出力電極に接続されるアクティブ負荷に好適である。

(もっと読む)

81 - 100 / 224

[ Back to top ]