Fターム[5J098AA03]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | 半導体素子 (443) | FET (224)

Fターム[5J098AA03]に分類される特許

61 - 80 / 224

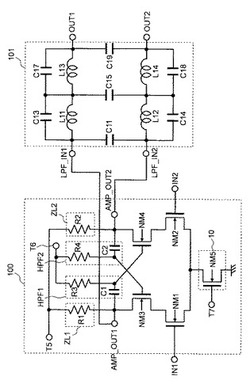

低周波透過回路、通信回路、通信方法、通信回路のレイアウト方法

【課題】透過周波数域における利得が一定かつ遮断周波数域への遷移における利得変化が急峻であって、かつ、帯域外抑圧比の大きい低周波透過回路を提供すること。

【解決手段】本発明の一態様は、インダクタ素子を有する低周波透過フィルタ101と、低周波透過フィルタ101に縦続接続され、低周波透過フィルタ101が透過から遮断へ遷移する周波数近傍かつ透過周波数域内に利得の盛り上がりを有する増幅器100と、を備える低周波透過回路である。

(もっと読む)

無線受信機用半導体装置

【課題】マルチバンド無線受信機のバンドパスフィルタを集積回路で構成する場合に、回路規模が大きくなり、チップ面積が大きくなったり、製造コストが高くなる。

【解決手段】混合回路58は無線受信信号SRFをダウンコンバートして中間信号SIFを生成する。IFBPF60は、抵抗R及びキャパシタCを用いたRCアクティブフィルタで構成され、SIFから目的受信信号を抽出する。抵抗Rは、クロック信号SCLによって駆動されるスイッチトキャパシタからなる等価抵抗により構成される。SCLを生成するフィルタ制御クロック生成回路72は、SCLの周波数fCLを、目的受信信号が属するバンドに応じて切り換えることができる。IFBPF60の通過帯域は、クロック周波数fCLによる抵抗Rの等価抵抗値の切り換えにより、受信バンドに対応して変更できる。

(もっと読む)

半導体装置

【課題】温度信号の製造バラツキが小さく、高精度の温度信号を生成可能な電子回路を提供すること。

【解決手段】本発明は、ピンチオフ状態にせしめられる第1FET(FET1)と、第1FETのソース端子S1に接続されてなる温度信号Vtempを出力する温度信号出力端子と、を具備する電子回路である。本発明によれば、ピンチオフ状態のFETのソース端子から出力される温度信号を用いることにより。製造ばらつきの小さい温度信号を得ることができる。

である。

(もっと読む)

フィルタ回路のトリミング方法

【課題】時定数が比較的短い高速なフィルタ回路について、トリミングを容易に行うことができるトリミング方法を提供する。

【解決手段】フィルタ回路4の出力端子に、パルス信号の出力状態が変化したことを検出すると、アクティブとなる検出信号を出力し続けるように構成されるパルス検出回路11を配置する。そして、フィルタ回路4の時定数を一定方向に漸次変化させながら、所定パルス幅のパルス信号を入力した場合、パルス検出回11路が検出信号を出力した時点に、フィルタ回路4に設定した時定数でトリミングを完了する。

(もっと読む)

フィルタ

【課題】タップ係数として任意の値を設定することができるフィルタを得ることを目的とする。

【解決手段】キャパシタ11,31により充電された電荷とキャパシタ13,33により充電された電荷の総和を出力端子Pに出力し、キャパシタ12,32により充電された電荷とキャパシタ14,34により充電された電荷の総和を出力端子Nに出力する。これにより、キャパシタ11〜14,31〜34の容量値Cpp,Cpn,Cnp,Cnnを適宜変更することで、タップ係数として任意の値を設定することができる。

(もっと読む)

MOSトランジスタ抵抗器、フィルタおよび集積回路

【課題】製造上のばらつきによるリーク電流の変化に起因する抵抗値の変動が低減され、かつ温度特性の良好なMOSトランジスタ抵抗器を提供する。

【解決手段】抵抗器として使用される第1MOSトランジスタM1と、第1MOSトランジスタのソースに接続され、入力電圧Vinを印加する入力電圧源1と、第1MOSトランジスタのゲートに接続され、ゲート電圧Vgを印加するゲート電圧源6とを備えたMOSトランジスタ抵抗器。ゲート電圧Vg及び入力電圧Vinは、第1MOSトランジスタのゲート−ソース間電圧及びソース−ドレイン間電圧が、第1MOSトランジスタを非飽和領域で動作させる範囲で印加されるとともに、第1MOSトランジスタの抵抗値における温度特性の温度特性が一定になる条件を満たす関係に設定される。

(もっと読む)

移相回路

【課題】入力信号の周波数に依存せずに入力信号に対して所定の位相差を有する出力信号を生成する。

【解決手段】VDDから定電流を供給する定電流回路201aと、入力電流に対してn倍の出力電流を流すカレントミラー回路204a、205aと、矩形波の入力信号1Aaの論理レベルによって定電流回路に流れる電流をカレントミラー回路に流すか、出力端子1Baに流すか切り替えるスイッチ回路202a、203aとを備えた波形生成回路102aにより、立ち上がり勾配1に対してn倍の立ち下がり勾配波形を有する三角波を生成する。これと反転信号1Abを入力した波形生成回路102bにより生成した三角波の電圧をコンパレータ103で比較し出力信号を生成する。入力信号のデューティー比が50%である場合には、1/(2+2n)周期遅延した出力信号が得られる。

(もっと読む)

半導体集積回路

【課題】 内蔵フィルタの周波数特性の不所望な変化を軽減すること。

【解決手段】 半導体集積回路は校正回路200を具備して、内蔵容量70:151は、複数の容量およびスイッチを有する。V・I変換器20、30は基準電圧を電流に変換して、電流に応答する時間積分器40、50は容量70の充電または放電の時間積分を実行して、電圧比較器80は基準電圧と内蔵容量70の端子電圧とを比較する。校正動作の間に複数回の時間積分と複数回の電圧比較が順次に実行されて、順次に生成される複数回の電圧比較の結果はラッチ90に順次に格納される。校正動作の完了時点のラッチの格納結果に従って、内蔵容量70:151の複数のスイッチの各オン・オフ制御と内蔵フィルタ150の周波数特性とが決定される。V・I変換器は、スイッチ素子SW0を含む。内蔵容量70:151の複数のスイッチとV・I変換器のスイッチ素子は、MOSトランジスタである。

(もっと読む)

移相回路

【課題】低損失化を図ることができるとともに、小形化を図ることができる移相回路を得る。

【解決手段】第1の入出力端子1aと、第2の入出力端子1bと、第1の入出力端子1aと第2の入出力端子1bの間に接続された第1のスイッチング素子2aと、第1の入出力端子1aに一端が接続された第1のキャパシタ3aと、第2の入出力端子1bに一端が接続された第2のキャパシタ3bと、第1及び第2のキャパシタ3a、3bの他端とグランド4の間に接続された第2のスイッチング素子2bとを設けた。

(もっと読む)

半導体集積回路装置

【課題】高精度に設定された受端抵抗を備えた半導体集積回路装置を提供する。

【解決手段】第1回路の第1端子は、所望の抵抗値を有する抵抗素子が接続され、電圧比較部は、第1端子の電圧と第1中間電圧との比較出力信号を形成し、制御論理部は、スイッチ部を制御して第2中間電圧を第2抵抗回路のMOSFETのゲートに供給し、第1抵抗回路の複数のMOSFETのオン/オフ制御により合成抵抗値を一方から他方に向けて変化させ、電圧比較出力が反転した時点のオン/オフ制御検知して記憶する。スイッチ部を制御して電圧比較出力を第2抵抗回路のMOSFETのゲートに供給する。第2回路の第3抵抗回路は、第1抵抗回路と同様な複数のMOSFETがオン/オフ制御され、第4抵抗回路のMOSFETのゲートは、第2抵抗回路のMOSFETのゲートと同じ電圧比較出力が供給される。

(もっと読む)

パルス伸長回路及び半導体装置

【課題】幅のより短いパルスに対して伸長が可能なパルス伸長回路及び半導体装置を提供する。

【解決手段】それぞれのソースが定電流源21を介して電源端子5に接続され、それぞれのドレインが定電流源21より電流駆動能力の大きな定電流源22を介して接地端子6に接続され、ゲートが入力端子27に接続されたp‐MOSトランジスタP1及びゲートが出力端子28に接続されたp‐MOSトランジスタP2と、一端がp‐MOSトランジスタP1、P2のソースと定電流源21との間に接続され、他端が接地端子6に接続されたキャパシタC1と、ドレインがp‐MOSトランジスタP2のゲートに接続され、且つ定電流源23を介して電源端子5に接続され、ソースが接地端子6に接続され、ゲートがp‐MOSトランジスタP1、P2のドレインと定電流源22との間に接続されたn‐MOSトランジスタN1とを備える。

(もっと読む)

パッシブイコライザ

【課題】ゲインを増大させるために負のインピーダンスを用いることができるパッシブイコライザを提供する。

【解決手段】

ゲインを増大させるために負のインピーダンスを利用するパッシブイコライザは、第1のRCループと、第2のRCループと、カスケードRL回路および交差結合反転器ユニットとを含む。第1のRCループおよび第2のRCループのそれぞれは、第1の抵抗器と、ノードで第1の抵抗器に直列に接続され、それによって抵抗器直列を形成する第2の抵抗器と、抵抗器直列に並列に接続されるコンデンサとを含む。カスケードRL回路は、RCループの間に接続され、第5の抵抗器と、第6の抵抗器と、第5の抵抗器と第6の抵抗器との間に接続されるインダクタとを含む。優れた高周波数ゲインを得るために負のインピーダンスの特徴を用いるために、交差結合反転器ユニットは、RL回路に並列に接続され、RCループの間に接続される。

(もっと読む)

アクティブバラン回路

【課題】アクティブバラン回路をMMIC化が容易な小型の構成にする。

【解決手段】平衡入力の一方を増幅し180度位相が回転した信号を取り出すN形電界効果トランジスタを有する第1の増幅回路と、平衡入力の他方を増幅し同位相の信号を取り出すP形電界効果トランジスタを有する第2の増幅回路と、第1および第2の増幅回路の出力信号を合成して不平衡出力として取り出す合成回路を備えたものである。

(もっと読む)

半導体集積回路

【課題】複数のノイズパルスが連続して印加される場合においてもノイズを除去する能力を高めたノイズ除去回路を含む半導体集積回路を提供する。

【解決手段】この半導体集積回路は、入力信号を遅延する直列接続された複数の遅延回路と、複数の遅延回路によって互いに時間差が与えられた少なくとも3つの信号の論理積を求めることによってセット信号を生成する第1の論理回路と、複数の遅延回路によって互いに時間差が与えられた少なくとも3つの信号の論理和を求めることによってリセット信号を生成する第2の論理回路と、第1の論理回路によって生成されるセット信号によってセットされ、第2の論理回路によって生成されるリセット信号によってリセットされることにより、正論理の入力信号からパルス状のノイズが除去された出力信号を生成するRSラッチ回路とを具備する。

(もっと読む)

信号処理回路

【課題】良好な入力インピーダンス整合特性を維持しながら低雑音化が可能となる増幅回路を有する信号処理回路を提供することを課題とする。

【解決手段】入力端子に入力された信号を増幅して出力端子から出力するゲート接地増幅回路(111)と、前記ゲート接地増幅回路の入力端子及び出力端子間に接続される帰還インピーダンス回路(Zf)と、前記ゲート接地増幅回路の出力端子から出力される信号を周波数変換し、相互に直交関係にあるI相信号及びQ相信号をI相信号用出力端子及びQ相信号用出力端子から出力する直交スイッチングミキサ(113)と、前記直交スイッチングミキサのI相信号用出力端子及びQ相信号用出力端子に接続される周波数フィルタ(116)とを有することを特徴とする信号処理回路が提供される。

(もっと読む)

差動単相変換回路

【課題】差動単相変換回路におけるチップ面積の縮小又は同相ノイズ信号の除去又は電力損失の低下を図る。

【解決手段】差動信号が入力され単相信号が出力される差動単相変換回路10であって、差動信号の一方が入力される制御端子、第1端子、及び第2端子を有する第1トランジスタM2と、接地された制御端子、第1トランジスタの第1端子に接続される第2端子、及び差動信号の他方が入力されるとともに、出力信号が出力される第1端子を有する第2トランジスタM3とを有するカスコード増幅器、第1トランジスタの第2端子に接続される位相調整用容量C2、及び、第1トランジスタの第2端子に接続される電流源M1、を備える差動単相変換回路が提供される。

(もっと読む)

アクティブ接地キャパシター

【課題】接地キャパシターのキャパシタンスを拡大する手段を提供する。

【解決手段】第一の抵抗1とキャパシター2で構成される低域通過濾波器の前段及び後段に電圧利得が+1未満で限りなく+1に近く、入力インピーダンスが十分に高く、出力インピーダンスが十分に低い前置増幅器3と後置増幅器4を接続し、さらに前置増幅器3の入力端と後置増幅器4の出力端を第二の抵抗5で接続し、第一の抵抗1の抵抗値は第二の抵抗5の抵抗値よりも大きくして実現する。

(もっと読む)

キャパシタンス乗算器回路

キャパシタンス乗算器回路が、追加の回路を追加することまたは追加の電力を必要とすることなしにキャパシタンス乗算器効果を達成するために、回路のRCフィルタ中のキャパシタを通る電流を検知し、その電流を乗算するように構成される。回路は、RCフィルタと、フィルタ出力に接続された第1の信号経路と、フィルタに入力に接続された第2の信号経路とを含む。フィルタを通る電流出力(iout)は、2つの経路に分割され、第1の経路において検知され、第2の経路において乗算される。乗算された電流は、キャパシタCの実効キャパシタンスを上げるために第2の経路からフィルタ入力にフィードバックされる。キャパシタンス乗算器回路は、フィルタ中のキャパシタの実効キャパシタンスを上げる際に、全体的な回路の周波数応答、直線性性能および/または安定性に影響を及ぼさない。  (もっと読む)

(もっと読む)

フィルタ回路及びその制御方法

【課題】CMCの正極側巻線と負極側巻線に流れる電流を等しくし、所望の特性を得るようにしたフィルタ回路の提供。

【解決手段】コモンモードノイズフィルタの正極側巻線と、負極側巻線に流れる電流を監視する手段(2、3)と、監視結果に基づき、正極側巻線と負極側巻線が互いに等しくなるように調整する手段(4、5、6)を備える。

(もっと読む)

アクティブインダクタおよび差動アンプ回路

【課題】低電源電圧下においても、半導体集積回路上での面積および消費電力の増大を抑えつつ、高域での利得のピーキングの傾きを急峻化する。

【解決手段】P型電界効果トランジスタM1のソースを電源電位VDDに接続し、P型電界効果トランジスタM1のドレインを出力端子outに接続し、N型電界効果トランジスタM2のドレインを電源電位VDDに接続し、N型電界効果トランジスタM2のソースを電流源IBを介して接地電位に接続し、P型電界効果トランジスタM1のゲートをN型電界効果トランジスタM2のソースに接続し、N型電界効果トランジスタM2のゲートを抵抗素子Rpを介してP型電界効果トランジスタM1のドレインに接続する。

(もっと読む)

61 - 80 / 224

[ Back to top ]